過采樣技術是數字信號處理者用來提高模數轉換器(ADC)性能經常使用的方法之一,它通過減小量化噪聲,提高ADC的信噪比,從而提高ADC的有效分辨率[1]。過采樣技術不但沒有增加額外的模擬電路,而且由于提高了有效分辨率還能簡化模擬電路,并且簡單易行,因而被數字信號處理實踐者廣泛應用于測控領域[2-6]。

過采樣技術的一個關鍵環節是采樣后的低通濾波器(LPF, Low Pass Filter),沒有這個濾波器,過采樣產生不了任何效果[7]。然而,許多應用中,需要測量多種信號,數據采集部分必須具有自適應特性,即根據輸入信號的頻帶能自主選擇下抽取率,過采樣后低通濾波器的特性也應隨之變化。因而,有必要設計一款參數可變的低通濾波器來滿足這種需求。

過采樣技術中的低通濾波器

過采樣技術的低通濾波器要同時完成量化噪聲的濾除和減采樣時抗混疊濾波的功能。過采樣技術能較完美實現其目標的濾波器參數滿足:通帶截止頻率,通帶衰減Rc=-3dB,阻帶截止頻率,濾除量化噪聲需要的阻帶衰減為

其中,M為過采樣率,N為下抽取率,B為ADC原有的分辨率,B0為提高的分辨率,N=4B0,并且通常有 。而濾波器的類型為FIR濾波器,其階次與下抽取率成正比。

可變參數低通濾波器的設計

由2節可知,過采樣中的濾波器特性由ADC本身的分辨率和下抽取率決定。下抽取率變化,濾波器參數會發生改變,濾波器則必須重新設計。從FIR濾波器的設計流程[8]來看,截止頻率變化后,濾波器系數會隨之變化。如果獲得截止頻率后再計算濾波器系數,會帶來大量運算量,因為每計算一組濾波器系數都要進行一次IFFT(Inverse Fourier Transform)。通常的做法是在PC機上計算出系數后,做成查找表。由于下抽取率變化,這樣的表會有很多張,會消耗大量存儲空間。而本小節采用的方法,避免了這種情況,選取一組合適的濾波器系數,便可完成多種下抽取率的濾波。

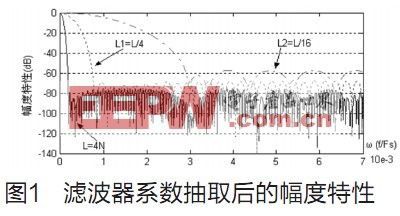

濾波器系數決定濾波器特性,理論上講,只用一組濾波器系數是不能實現可變參數濾波器的。由2節可知,下抽取率N與濾波器截止頻率成反比,與阻帶衰減成正比,與濾波器長度成正比。假設下抽取率為N0時濾波器系數h(n),n=0,1,2…L-1,我們怎樣通過h(n)這組基準系數來獲得N不等于N0時的濾波器系數呢?

當N

下抽取率的情況實現較為容易,然而當時,濾波器系數大于基準系數,此時怎樣設計濾波器來滿足要求呢?我們采用原本用來實現高計算效率的窄帶低通濾波器的插值FIR濾波器[8],來實現低通濾波器參數的變化。

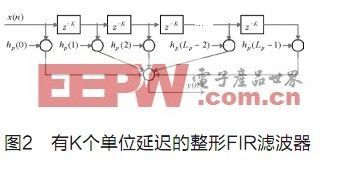

插值FIR濾波器是在L抽頭、非遞歸線性FIR濾波器的性能基礎上,將L抽頭的FIR濾波器各個抽頭之間的一個單延遲,用K個單位延遲代替而設計形成的,K為擴展因子,是一個整數,如圖2所示。原來的FIR濾波器稱為原型濾波器,具有擴展延遲的濾波器稱為整形子濾波器。

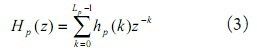

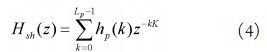

原型FIR濾波器在z域的傳遞函數為:

式(3)中,Lp為hp的長度。則整形子濾波器傳遞函數為:

其擴展沖激響應長度為 ,反映到時域上,整形子濾波器系數為:

,反映到時域上,整形子濾波器系數為:

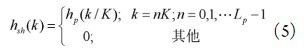

圖3給出了K=3個單位延遲在頻域的影響。時域濾波器沖激響應擴展K倍,導致頻域 幅度響應壓縮K倍,如圖3(b)。圖中那些以1/K整數倍為中心、重復出現的

幅度響應壓縮K倍,如圖3(b)。圖中那些以1/K整數倍為中心、重復出現的 的通帶稱為虛像。只要將這些虛像濾除,就能獲得衰減特性不變,截止頻率為原濾波器截止頻率1/K的濾波器,恰好符合過采樣后低通濾波器截止頻率與下抽取率成反比的特性,因而可用于過采樣中可變參數濾波器的設計。此處,濾除虛像的濾波器稱為壓制虛像濾波器。

的通帶稱為虛像。只要將這些虛像濾除,就能獲得衰減特性不變,截止頻率為原濾波器截止頻率1/K的濾波器,恰好符合過采樣后低通濾波器截止頻率與下抽取率成反比的特性,因而可用于過采樣中可變參數濾波器的設計。此處,濾除虛像的濾波器稱為壓制虛像濾波器。

插值濾波器其實是整形子濾波器和壓制虛像濾波器的級聯。整形子濾波器很好實現,只要在原型濾波器系數的基礎上按要求插入零值即可,下面主要看壓制虛像濾波器的設計。當下抽取率大于一定值時,低通濾波器為窄帶濾波器,則整形濾波器的虛像也為一窄帶。平均濾波器的幅度響應在1/L的整倍數處為一窄帶陷波器,可以濾除整形濾波器產生的虛像。虛像出現在1/K的整倍數處,因此,只要使得作為壓制虛像濾波器的平均濾波器的長度滿足, ,便可以濾除虛像。

,便可以濾除虛像。

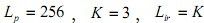

圖4為 時,原型濾波器、整形濾波器、壓制虛像濾波器和最后獲得的插值濾波器的幅度響應,原型濾波器為FIR切比雪夫濾波器。從圖4(a)可以看出,虛像出現的位置與平均濾波器的零點位置對齊,從而抑制了虛像。由于太小,平均濾波器的旁瓣寬度較大,陷波帶大于虛像帶寬,導致虛像的抑制沒有達到濾波器要求的阻帶衰減。但是,虛像所處頻率與過采樣頻率相當,此處出現的噪聲僅為量化噪聲,此處衰減特性只要將其抑制到ADC分辨率提高后的量化噪聲水平,即滿足過采樣的要求。例如:ADC分辨率經過采樣后提高6位,其要求的衰減特性為-36.1dB,而圖4(a)插值濾波器虛像處的衰減為52dB,足以滿足大部分設計的要求。

時,原型濾波器、整形濾波器、壓制虛像濾波器和最后獲得的插值濾波器的幅度響應,原型濾波器為FIR切比雪夫濾波器。從圖4(a)可以看出,虛像出現的位置與平均濾波器的零點位置對齊,從而抑制了虛像。由于太小,平均濾波器的旁瓣寬度較大,陷波帶大于虛像帶寬,導致虛像的抑制沒有達到濾波器要求的阻帶衰減。但是,虛像所處頻率與過采樣頻率相當,此處出現的噪聲僅為量化噪聲,此處衰減特性只要將其抑制到ADC分辨率提高后的量化噪聲水平,即滿足過采樣的要求。例如:ADC分辨率經過采樣后提高6位,其要求的衰減特性為-36.1dB,而圖4(a)插值濾波器虛像處的衰減為52dB,足以滿足大部分設計的要求。

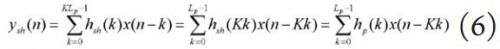

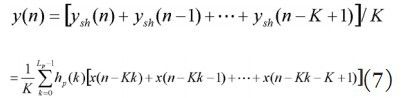

插值濾波器在過采樣中的實現的流程為:在原型濾波器進行K倍內插后,再做K點的平均濾波即可。看上去需要兩步才能實現低通濾波,實際上,由于整形和平均濾波的特性,我們可以一步完成濾波。由式(3)可知,整形子濾波器的輸出為:

為下抽取及計算方便,將整形濾波器的長度從 ,改為KLp 。由于FIR濾波器系數的不敏感性,這樣做并不會影響濾波器特性。則插值濾波器的輸出為:

,改為KLp 。由于FIR濾波器系數的不敏感性,這樣做并不會影響濾波器特性。則插值濾波器的輸出為:

由式(4-9)可知,插值濾波器輸出是將K點值平均后,再與原型濾波器系數加權平均的結果。可以看出,實現方式很簡單。

過采樣技術在FGPA的實現

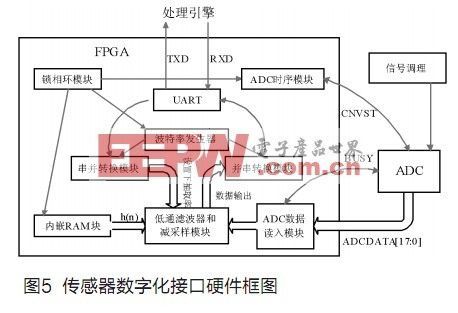

一些通用的數據采集模塊需要實現多種信號的測量,注重模塊的通用性,因此,放大、濾波等信號預處理電路這樣的個性事物是不被允許存在的。將過采樣技術應用于通用模塊,省略信號預處理電路,根據信號特點,選取合適的過采樣率和下抽取率,平衡最終采樣率和分辨率,來獲取要求的測量精度。根據通用模塊的要求,設計了圖5所示結構來實現通用模塊的過采樣技術。

由圖5可知,FPGA實現了以下功能:產生ADC時序,控制ADC的采樣頻率;以ADC轉換結束標志位為觸發信號,讀取ADC的轉換數據;為濾除ADC輸出信號的量化噪聲和減小數據量,實現低通濾波和減采樣模塊;配置一塊ROM區,用于存儲濾波器系數,用于濾波器的實現;為與外部處理引擎進行通訊,實現UART接口協議;為使個模塊協調工作,采用鎖相環產生不同頻率的時鐘。

而模塊的工作流程為:處理引擎將待測信號的頻率通過UART傳給低通濾波和減采樣模塊,該模塊根據該頻率設置濾波器參數和減采樣的下抽取率;ADC時序模塊產生CNVST,啟動ADC進行采樣,BUSY信號觸發數據讀取模塊將數據讀入;低通濾波器和減采樣模塊根據設置好的參數和下抽取率對讀入的數據進行處理,處理完畢后,再將數據通過UART傳到處理引擎做后續處理。

模塊中的ADC選用的是ADI公司的AD7674,18位、800KSPS逐次逼近型模數轉換器,具有較高的數據通過率。支持差分輸入模式,其內部采樣保持電路的負載可調,5V單電源供電。器件內部還集成了轉換時鐘、基準緩沖器及錯誤校準電路,并具有功能強大的串口和并口,與3V和5V電平兼容。而FPGA則選用的是Altera CycloneⅡ-EP2C8Q208C8,包括5個部分:可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源和底層嵌入功能單元。

基于AD7674和EP2C8,該模塊設計獲得的相關參數為:

(1) 下抽取率 ,過采樣率

,過采樣率 ,由于ADC的最高采樣頻率為800KSPS,則該模塊可用于0Hz -32kHz信號的測量;

,由于ADC的最高采樣頻率為800KSPS,則該模塊可用于0Hz -32kHz信號的測量;

(2) ADC的本身分辨率為18位,過采樣后達到的最大分辨率為25位;

(3) ADC基準電壓為4.096V,最高分辨率時可分辨的信號大小為:

(4) 為使ADC達到25位分辨率,除滿足下抽取率N=47外,還必須保證低通濾波器的阻帶衰減符合過采樣的要求。由式(1)和(2)可知, 阻帶衰減R0=64.3dB。使用切比雪夫最佳逼近法獲得濾波器系數,通過計算及考慮到設計余量,得到濾波器長度L=4N,N=47時,實際阻帶衰減為R0=75dB;利用MATLAB軟件中的函數CHEBWIN(L,R0)獲得濾波器系數;將濾波器系數量化成8位,并進行16倍下抽取,抽取后的值對應為N=45 時的濾波器系數。將其存入FPGA的ROM區,以此為基準得到其他下抽取率的濾波器系數。

(5) 實現該模塊消耗的FPGA資源為:7275個LE(88%),65544個memory bits(40%),24個9位乘法器(67%),27個I/O口(20%)1個PLL(50%)。

實驗結果和分析

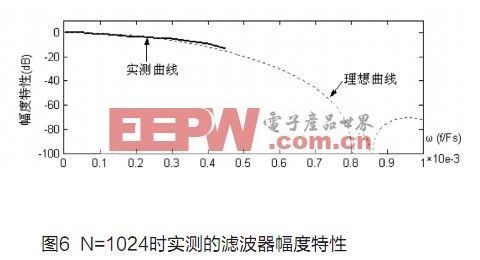

為考察模塊設計的正確性,對其進行了測試。主要分為兩個部分。第一部分為低通濾波器的測試。首先以N=1024 為例,驗證實際濾波器的幅度特性是否與設計的一致,然后驗證可變參數低通濾波器設計的正確性。第二部分則以心電信號為例,驗證模塊分辨率與過采樣率的關系。

圖6為N=1024時,MATLAB設計的濾波器幅度特性和實測的濾波器幅度特性的比對。測試方法為:ADC的采樣率為800kHz,下抽取率為1024,最終采樣率為 ;給系統加入3V不同頻率的正弦波,頻率范圍為5Hz-360Hz;獲得的數據傳到PC上,用MATLAB計算各組數據的FFT獲得幅度值;假設5Hz的正弦波經過系統后幅度不發生衰減,以此為基準計算各頻率點的衰減情況。由圖6可知,實測的幅度特性與設計的基本一致。不足之處是,受采樣率的限制,被測信號頻率不能大于采樣率的一半,我們只能得到部分采樣點的衰減情況。

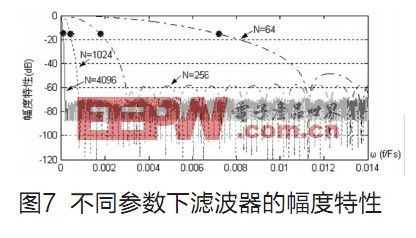

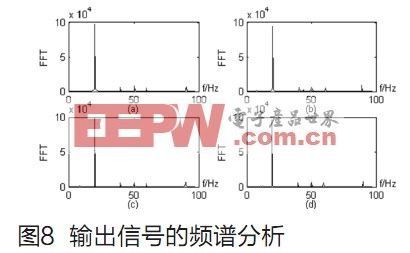

圖7是可變參數濾波器在不同下抽取率時的幅度特性。為驗證改變參數時濾波器是否正常工作,給系統輸入信號為2V、20Hz正弦波和0.95V、90Hz正弦波的加性信號,ADC分別以采樣率12.5kHz、50kHz、200kHz、800kHz對加性信號采樣,下抽取率依次為64、256、1024、4096,則四組數據的最終采樣率均為195Hz。以20Hz正弦波為基準,驗證90Hz正弦波的衰減情況。圖7中每條曲線上的黑點對應的是90Hz的衰減特性,分別為:15.345dB、15.504 dB、15.54 dB、14.958 dB。圖8是信號經過系統后的頻譜分析。由圖8可知,90Hz的正弦波明顯得到了抑制,其衰減分別為:16.896 dB、14.408 dB、17.345 dB、14.804 dB,實測的數據與設計的基本一致,說明各參數下的濾波器能正常工作。另外,圖8中三個小的尖峰,分別為50Hz干擾和20Hz的諧波。

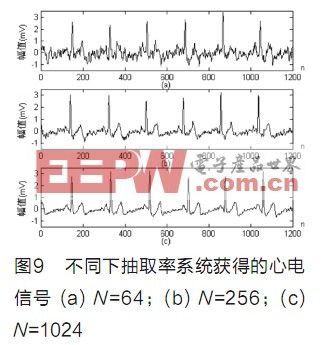

圖9是系統測得的實驗室某同學的心電波形。由圖9可知,隨著下抽取率的增大,心電信號的細節越來越清楚,即分辨率越來越高。因此,隨者下抽取率的增大,系統的分辨率是增加的。

綜上所述,基于過采樣技術的通用數據采集模塊可以根據被測信號的不同,改變自身的參數,達到測量要求,同時,也完成了可變參數低通濾波器的硬件實現。

結語

為減小通用數據采集模塊的體積和成本,將過采樣技術應用于模塊的ADC中。由于通用模塊測量多種信號,為達到過采樣對低通濾波器的要求,設計了可變參數低通濾波器。該濾波器簡單易行,并且計算效率高,在本文設計的通用模塊中,每獲得一個采樣點,最多只需進行4次18bits×8bits的乘法運算。

此外,本文從硬件上實現了該模塊的設計,并對模塊進行了測試,最后以心電為例,驗證了參數的可變性。