摘 要: 針對電視制式PAL /NTSC 信號輸出VGA 顯示格式的解決辦法,詳細講述了基于FPGA 視頻格式轉換系統的設計實現。采用Cyclone Ⅲ系列的EP3C1*84C6作為核心處理器件,實現了NTSC /PAL制式視頻的解碼、色空間轉換( CSC)、幀速率轉換和隔行逐行轉換、縮放、視頻DAC 轉換,最終實現分量R、G、B的VGA 視頻格式的視頻輸出,分辨率可達1 600 × 1 200@ 100 Hz。

1 系統設計

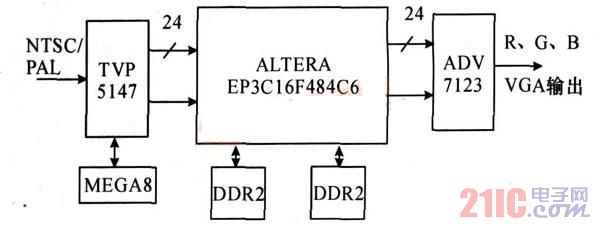

設計使用了ALTERA 的EP3C16F484C6型號FPGA 作為視頻處理核心,連接兩片DDR2 SDRAM,DDR2芯片型號為M icron的MT47H 32M16BN _37E,作為系統的數據存儲器件,帶寬為32 bit,時鐘速率為200MHz,數據速率為400 Mbps。視頻解碼芯片為TVP5147,視頻DAC 采用高性能ADV7123。整個系統框架如圖1所示。

圖1 視頻處理板框圖

2 硬件功能模塊。

2. 1 視頻解碼

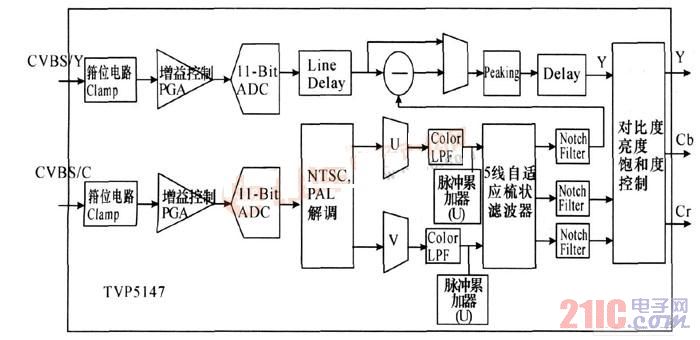

TVP5147的解碼過程如圖2所示。

圖2 TVP5147解碼過程

視頻解碼芯片TVP5147復位后,通過MCU 向其正確配置I2C寄存器。本文的TVP5147的I2C 寄存器配置的值如表1所示。

表1 TVP5147的I2C寄存器設置

2. 2 視頻存儲器

在視頻處理模塊中包括了大量的視頻數據存儲器模塊,主要可分為行存儲器、幀存儲器以及查找表存儲器3類。

( 1)行存儲器用于存儲視頻中一行的數據,由于數據量不大,用FPGA 內部RAM 來實現。

( 2)幀存儲器用于存儲一幀視頻數據,由于數據量大,用DDR2來實現。

( 3)查找表存儲器用于產生不規則的輸入輸出相應,如Sin函數和Gamma矯正曲線。

2. 3 FPGA 模塊設計

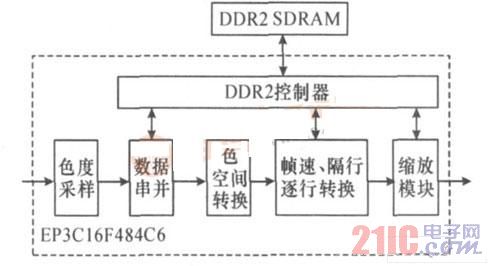

FPGA 模塊設計如圖3。

圖3 FPGA 模塊框圖

2. 3. 1 數據串并轉換和色度重采樣模塊

此模塊分為串并轉換和色度重采樣兩個部分。

串并轉換主要是為了把TVP5147 輸出的混合數據轉換為分量數據。由于采用了BT. 656 10- b it 4:2:2模式,其輸出數據時鐘為像素時鐘( 13. 5 MHz) 的兩倍,輸出數據依次為Cb0,Y0,C r0,Y1,Cb1,Y2,C r1 等,本模塊將其轉為4:2:2 的Y‘CbCr 分量數據,RTL 仿真結果如圖4所示。

圖4 串并轉換模塊仿真結果

雖然視頻分量傳輸帶來了更好的圖像還原度,但同時也帶來了數據帶寬的加大,因此很多時候人們把視覺上不那么重要的色差信號進行了重采樣為4:2:2 (或4:1:1)以降低傳輸數據帶寬。而在視頻和顯示系統內部基本使用4:4:4 的信號,因此色度重采樣也成了視頻轉換中必不可少的模塊。本文實現了4:2:2 到4%4%4和4:4:4 到4:2:2的轉換。4:2:2 到4:4:4 的轉換方法有直接重復法、一維濾波法以及亮度自適應濾波法。

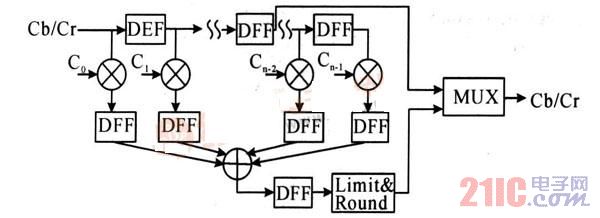

考慮硬件成本和處理質量,我們選用一維濾波法,即只考慮色度通道在水平方向的濾波。圖5為采用n抽頭FIR濾波器進行色度重采樣的模塊框圖。

圖5 4:2:2 到4:4:4色度重采樣模塊

2. 3. 2 色空間轉換模塊( CSC )

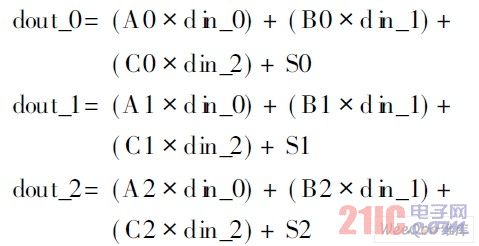

由于不同視頻標準采用了不同的色彩空間,而且有些視頻處理需要在特定色空間里處理,因此色空間轉換是十分必要的。色空間轉換實際上是一個三輸入經線性矩陣變換后得到新的三輸出,其基本的轉換公式如下:

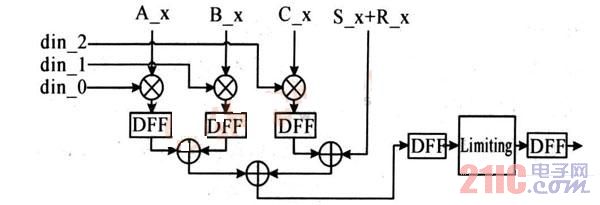

上式中的Ax,Bx,Cx,Sx 分別代表不同空間之間的轉換系數。一般視頻系統中涉及的色空間包括電腦的R' G ' B ' 空間,NTSC 和PAL的Y'UV 空間,以及Y’CbCr空間。圖6為轉換模塊框圖,其中的轉換系數可任意配置,即標準不限定。上節中的10 b it Y'CrCb可以通過這個色空間轉換器,用標清到高清的轉換系數轉為8 b it的BT. 709標準Y'CrC 數據。

圖6 色空間轉換模塊( Rx 為round ing 值)

輸入8 bit的R'G' B'信號,先經R' G' B' 到Y'CbC r轉換成10 b it的Y‘ CbC r信號,然后再轉成8 bit的R' G'B ' 信號。其中色空間轉換采用的是高清標準,采用小數部分為16 b it的定點小數來處理轉換系數。圖中上部分為8 bit的R'G'B'數據輸入,中間為10 b it的Y'CrCb數據,下部分為8 b it的R'G'B'數據輸出。由于做了流水線處理,輸出有3 個時鐘的延遲。

圖7 8 b its R’G‘B’轉10 bits Y‘ CbC r再轉回8 b its R’G‘B’仿真結果

2. 3. 3 幀率轉換和隔行逐行轉換模塊

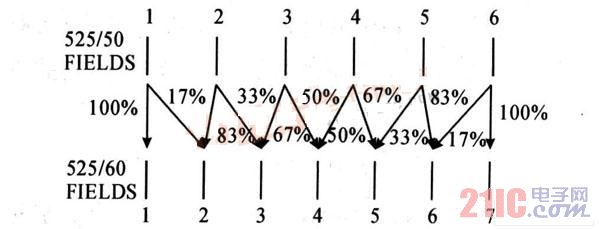

隔行轉逐行的方法可以分為空域和時域兩個方面。空域算法簡單,易于硬件實現,常見有直接重復行和在垂直方向上進行插值得到缺失的行。時域方法涉及到相鄰場之間的運算,常見方法有場混合、運動自適應去隔行算法以及復雜度最高的運動補償去隔行算法。本文折衷考慮使用場混合方法,即將場數據相鄰場兩兩合成為逐行的幀數據,如圖8所示。

圖8 場混合法實現隔行逐行變換

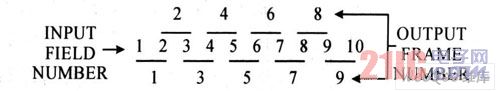

PAL和SECAM 制式的場頻為50 Hz,而NTSC 為60H z,當需要進行不同場頻信號的疊加就需要進行場頻轉換。大多視頻設備使用的幀頻為60 H z,因此本文只涉及50~ 60 H z的幀率轉換。常用方法有場重復、場插值、運動補償法,其中場插值算法如圖9所示。

圖9 50 Hz轉60 Hz的場插值方法

對于PAL制式從上面兩圖可知,只要能同時讀取3行場數據即可以實現隔行逐行變換和幀率轉換一次完成。如輸出的第1幀由輸入的第1,2 場數據決定,而輸出的第2 幀由輸入的第1,2,3場數據決定,而輸出的第3幀由輸入的第2,3,4 場數據決定,依次類推。

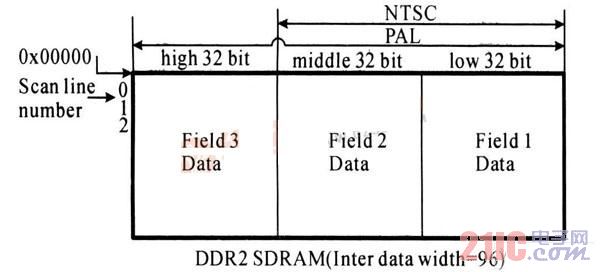

系統使用位寬為48的DDR2存儲器作為場存儲器,而在FPGA 內部DDR2控制器端數據寬度為96。如產生第2 幀輸出的處理過程為,在第1場存入時,把高64bit屏蔽掉不寫入,而低32 b it寫入場數據(實際只利用30 b it)。在第2場存入時,把高32 位和低32 b it屏蔽掉不寫入,而中間32 bit寫入場數據。在第3 場存入時,把低64 b it屏蔽掉不寫入,而高32 bit寫入場數據。這樣在數據讀取的時候可以順序同時讀出3場數據,然后進行上述的組合插值運算,即可得到輸出。場存儲器數據內格式如圖10所示。

圖10 可以實現同時去隔行和幀率轉換的場存儲器

注意新的輸入場數據不能覆蓋掉相鄰的數據,因此在數據存入時屏蔽位是在不斷跳動的,并以5 場為一個周期。雖然這樣降低了寫入的效率,但由于所有數據讀寫都是順序操作,因此從整體上來說仍然提高了DDR2 的存取效率,并且使操作變得簡單。對于NTSC 制式,由于幀率轉換部分可不用考慮,可以將只使用低64位部分進行兩場存儲。

2. 3. 4 縮放模塊

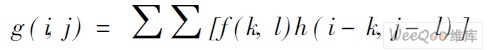

視頻縮放包括放大( up scaling ) 和縮小( downsca ling )兩個方面,而進行縮放的基本方法為空間插值。下式為對圖像進行插值的一般數學表達式,其中g ( i,j)為縮放圖像中待插值點的像素值,f ( k,l)為原始圖像中坐標( k,l)處的像素值,h( i- k,j - l)為插值基函數。

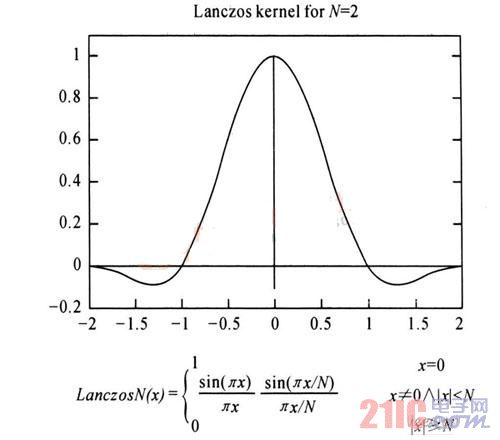

插值基函數的選擇可以有很多種,通常有二維的矩形函數、線性函數、三次函數及S inc 函數等,它們分別對應于最近鄰插值、線性插值、三次插值以及理想插值(實際中利用S inc函數截斷后插值) ,其插值效果為從差到好排列,但實現難度也依次提高。在實際處理中是利用濾波器來實現插值基函數,而且由于這些插值的對稱性,可以將其分解為橫向和縱向插值兩部分分開進行,如二維線性插值函數對應雙線性插值( Bilinear Interpo lation),三次函數對應雙三次插值( B icub ic Interpo lation) ,對于Sinc 插值函數實際中為多相位插值( Po lyphase Interpo lation)。本文使用多相位插值法實現圖像縮放,實際上在4 ? 4領域大小內進行多相位插值和三次插值幾乎是一樣的,只是對應插值函數值略微不同。多相位插值法是通過對輸出點對應原圖中的領域進行Lanczos2 函數移相插值來產生輸出點的。如圖11所示。

圖11 Lanczos2 函數

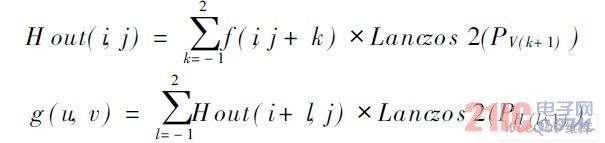

假設g ( u,v )為經縮放后輸出圖像中一點,其還原到原圖像的最近點為f ( i,j) 且兩者在原圖中相差( x,y )的坐標,則輸出點g ( u,v)的數學表達如下,從其可以看出實際上分為兩步實現分別進行垂直濾波和水平濾波。

其中有關系式: i = ( u ×W in ) /W out,j = ( v ×H in) /H out; x = ( u × W in)% W out,y = ( v ×H in)%H out。W in 和Wout分別為縮放前后的圖像寬度,H in和H out分別為縮放前后的圖像高度。圖12為4 ×4領域水平垂直相位,其中的水平相位值分別為PH 0,PH 1,PH 2,PH 3,垂直相位值分別為PV0,PV1,PV2,PV3。只要根據上述關系式求得x,y 值就能獲得8 個相位值,就能實現多相位濾波。

圖12 4×4 領域水平垂直相位

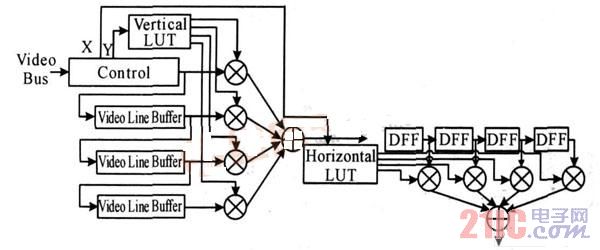

圖13為本文設計的圖像縮放器中濾波器部分框圖,其中的垂直水平查找表里分別存放著4個不同相位的Lanczos2 函數值。

圖13 圖像縮放器中的濾波器

2. 4 視頻DAC

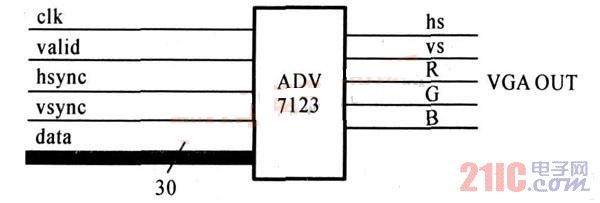

視頻編碼到模擬R、G、B 由視頻DAC 芯片ADV7123,它內部有三獨立通道10 bit高速DAC,如圖14所示為其功能圖及其系統作用。

圖14 ADV7123系統圖

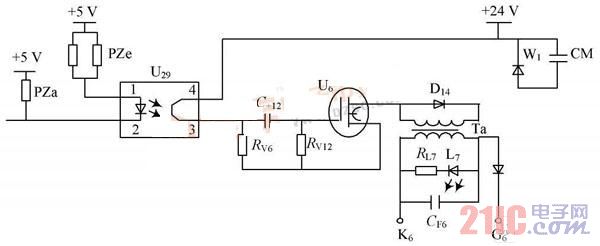

3 系統電源設計

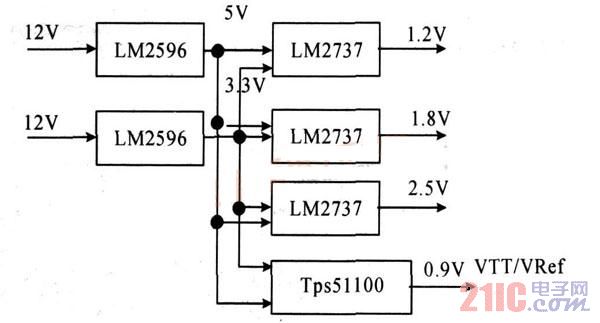

電源的可靠性是電子系統設計成敗的關鍵。在設計電源時,在保證電源的可靠性的基礎之上需要綜合考慮電源電路的效率與體積,此系統需要0. 9 V,1. 2 V,1. 8 V,2. 5 V,3. 3 V,5 V 共6種電源。

LM2737輸出電流最大為5 A,效率高達90%,封裝為SO IC,體積小。DDR2的VTT 與VRef的0. 9 V電壓由DDR 參考終端電壓通用芯片TPS51100 轉換而來。

圖15 電源設計框圖

4 結束語

本文采用Cyclone III的EP3C16F484C6器件及相關的視頻編解碼芯片設計視頻格式轉換系統,實現了普通電視信號到較為通用的VGA 接口信號的轉換,同時通過對視頻信號的縮放等處理增大視頻分辨率。另外,采用FPGA作為核心視頻處理器件,使得系統對視頻制式的支持具有很好的靈活性。