隨著數字信號處理和集成電路的發展,要求數據處理速度越來越高,基于單片機+DDS(直接數字頻率合成)的頻率合成技術已不能滿足目前數據處理速度需求。針對這一現狀,本文提出了基于FPGA+DDS的控制設計,能夠快速實現復雜數字系統的功能。

1 AD9910的硬件電路設計

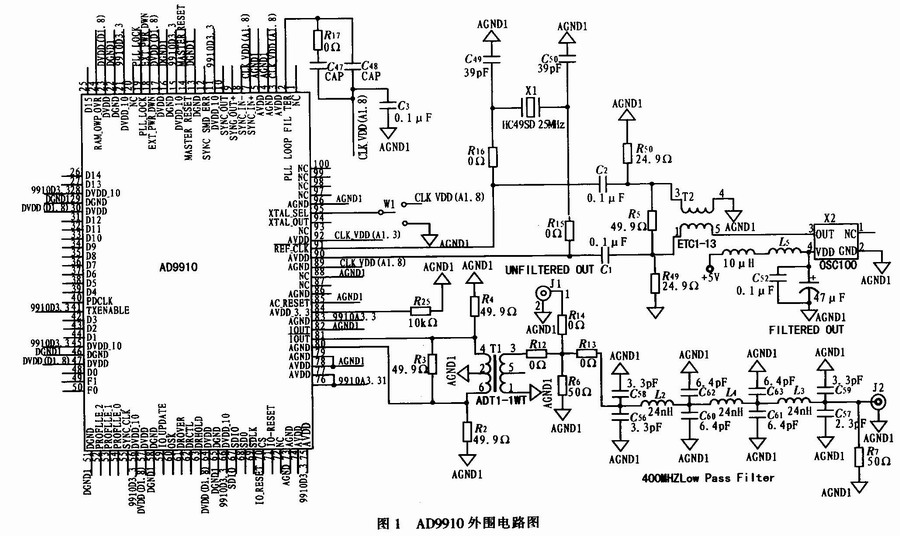

AD9910是ADI公司推出的一款單片DDS器件,內部時鐘頻率高達1GHz,模擬輸出頻率高達400 MHz,14-bit的DAC,最小頻率分辨率為0.23 Hz,相位噪聲小于-125 dBc/Hz@1 kHz(400 MHz),窄帶無雜散動態范圍大于80 dB,串行I/O控制,具有自動線性和隨機的頻率、相位和幅度掃描功能,1 024 32位RAM,具有調幅、調相的功能,1.8 V和3.3 V供電,可實現多片同步。應用在高靈敏度的頻率合成器、可編程信號發生器、雷達和掃描系統的FM調制源、測試與測量裝置以及高速跳頻系統AD9910芯片的主要外圍電路為:參考信號源、控制、環路濾波器和輸出低通濾波器等電路。參考信號源為AD9910提供基準頻率,參考信號輸入芯片后,內部的倍頻器和鎖相環起作用產生1GSPS的系統時鐘;控制電路通過芯片的I/O給內部寄存器寫入內容,寄存器內容不同,芯片工作狀態不同,控制芯片可以是單片、FPGA或DSP,本設計采用FPGA;

AD9910提供專門的管腳外接環路濾波器,以優化內部PLL的性能,環路濾波器為簡單的低通濾波器;AD9910輸出高達400 MHz的模擬信號,為了減少噪聲,在它的輸出端口設計了400MHz的低通濾波器。

圖1為實際設計的AD9910外圍連接圖。

在AD9910的電路設計中,應注意以下幾個問題:

1)AD9910電源和地設計。AD9910需要4組電源,AVDD(1.8 V)、DVDD(1.8 V)、AVDD(3.3 V)和DVDD(3.3 V),模擬電源和數字電源需要隔離,電源管腳的濾波最好采用鉭電容和陶瓷電容。在PCB設計中,數字地和模擬地分開,用磁珠單點連接,減少干擾。

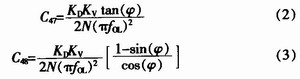

2)AD9910環路濾波器設計。當外部的時鐘較低時,例如100 MHz,系統時鐘1 GHz,芯片內部的鎖相電路起作用,這時需要在外部設計環路濾波器,如圖1中R17、C47和C48構成的RC濾波器,電容電阻值用如下公式計算。

![]()

其中:N為分頻比,KD為鑒相器的增益,KV是VCO的增益,fOL是環路帶寬。

3)晶振電路的設計。AD9910需要外部提供參考信號源,它的質量直接決定了模擬輸出信號的質量(頻率精度和相位噪聲),本設計采用高精度的溫補晶振,頻率100 MHz。在PCB設計時盡量靠近時鐘管腳。

2 FPGA控制AD9910的軟件實現

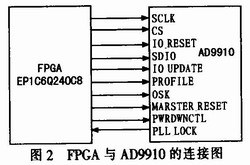

采用ALTERA公司的EP1C6Q240C8控制AD9910,該器件的外部時鐘頻率為50 MHz,20個128?36 bit的RAM塊,5980個邏輯單元(LE),240個管腳,屬表貼器件。

FPGA與AD9910的外圍電路簡單,無需外加任何驅動電路,從而節省了硬件電路設計和調試的時間,FPGA與AD9910的連接框圖如圖2所示。

其中,SCLK用于輸出數據交換的控制時鐘,CS為片選信號,IO_RFSET控制DDS的系統復位,SDIO是數據傳輸線,IO_UPDATE使能DDS內部各寄存器數據更新,PROFILE用來選擇八個相位/頻率寄存器中的一個,OSK用來選擇DDS的輸出鍵控模式,MASTER_RESET用來清除所有存儲單元,并且把寄存器設為默認值,PWRDWNCTL用來選擇是否使用外部使能控制,不使用時置為0,這里設置為0,PLL_LOCK用來指示鎖相環的鎖定狀態。另外,由于未采用多芯片數據通信,所以需將AD9910與同步信號相關的引腳懸空,例如7、8、9、10和53引腳。

根據需要AD9910有4種工作模式可供選擇,分別是單音模式、RAM調制模式、Digital ramp modulation模式和并行數據端口調制模式。這里選用最基礎的signal-tone單音工作模式。

對AD9910的17個寄存器進行設置,這里使用了AD9910的評估軟件對寄存器參數進行設置,只需要在評估軟件中輸入目標參數,軟件將自動給出寄存器中的值,這樣減小了工作量。根據需要,這里僅對其中的3個寄存器進行設置,分別是地址為0X01、0X02的控制寄存器和地址為

0X0E的單音模式profile。而其他的寄存器均使用默認值,因此無需設置。

FPGA對AD9910的軟件控制流程圖如圖3所示。

首先,對系統進行初始化,對FPCA的各控制信號進行復位操作,使能CS信號。

其次,對3個主要的寄存器進行設置。設置地址為0X01的寄存器CFR2,共32位,這里只需要使能第24位單音模式profile的幅度值,默認值為0,這里設為1,其余均使用默認值,因此地址為0X01寄存器的內容為0X01_40_08_20。

地址為0X02的寄存器CFR3主要用來設置PLL和VCO的參數。其中,第26位到第24位用來選擇PLL VCO參考時鐘的頻帶,這里選擇820~1 150 MHz的VC05,因此為101;第8位是PLL使能的選擇,默認值為0,這里選擇使能1;第7位到第1位這7 bit數據是PLL倍頻器的倍頻系數,默認值

為0000000b,這里對外部時鐘進行40倍頻,因此,設置為0101000b。其余各位均使用默認值。所以,地址為0X02寄存器的內容為0X1D_3F_41_ 50。

對地址為0X0E的單音模式profile進行設置,它是用來控制DDS的幅度、相位和頻率。其中第61位到第48位這14位用來設置幅度值,根據需要在評估軟件中輸入所需幅度值可以直接查看寄存器中相應位的值,這里使用默認值00_1000_1011_0101b;第47位到第32位這16位用來設置相位偏移量,這里仍舊使用默認值0X0000;低32位是用來設置頻率控制字的值,頻率控制字![]() ,其中,fout為輸出頻率,N為頻率控制字的位數,位數越大輸出頻率的分辨率越高,fc為系統時鐘1 GHz,這里輸出頻率為50 MHz,對應的頻率控制字為214748365,因此對應位的值設置為0X0CCC_CCCD。地址為0X0E寄存器的內容為0X0885_0000_0CCC_CCCD。

,其中,fout為輸出頻率,N為頻率控制字的位數,位數越大輸出頻率的分辨率越高,fc為系統時鐘1 GHz,這里輸出頻率為50 MHz,對應的頻率控制字為214748365,因此對應位的值設置為0X0CCC_CCCD。地址為0X0E寄存器的內容為0X0885_0000_0CCC_CCCD。

最后,結束IO_UPDATE的操作動作,完成一次完整的設置過程。

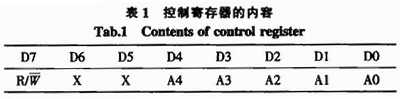

對寄存器的讀寫操作是通過向輸入端口SDIO發送8位指令來實現的,這8位中,最高位為讀寫指令,1為讀操作,0為寫操作,低5位用來選擇在通信周期時選通哪個寄存器進行數據的傳輸,控制寄存器的內容,如表1所示。

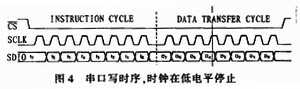

對AD9910讀寫操作時,需要注意AD9910的時序要求。對于串行I/O端口的各種控制信號之間的有4種基本的時序關系,分別是串口寫時序,時鐘在低電平停止;三線串口讀時序,時鐘在低電平停止;串口寫時序,時鐘在高電平停止;兩線串口讀時序,時鐘在高電平停止。這里采用第一種時序關系,時序圖如圖4所示。

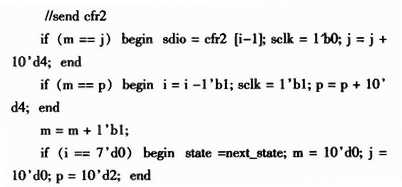

在SCLK上升沿,寫入數據有效,FPGA控制SCLK信號的產生。具體寫入數據的程序代碼(使用Vefilog HDL編寫)如下所示:

該指令用于對地址為0X01的控制寄存器CFR2進行寫操作。鑒于FPGA的高速處理能力,在程序設計時需要注意一些特殊的時序要求,如以下幾個方面。

1)AD9910開始工作時必須先將其復位,復位時間保持1 000個系統工作周期。

2)如果系統工作需要多次使用I/O_UPDATE,要注意I/O_UPDATE引腳置1的時間控制,這關系到系統能否順利設置各個寄存器。

為了更好的說明FPGA對AD9910的控制,以下給出相關例程:

例程中,將update信號設置為手動,通過頻率控制singletone profile0寫入頻率控制字0X0CCC_CCCD,此數字轉換成十進制為21474836 5,代入頻率控制字的公式,計算出頻率為50 MHZ。使用示波器測量觀察,如圖5所示。

圖中,橫坐標為時間t,單位為納秒(ns),縱坐標為電壓幅度(A),單位為毫伏(mv)。可以看出,輸出波形的頻率為50 MHz,與初始設定值一致。由此可見,程序符合設計要求。

3 結束語

FPGA對AD9910的控制是通過對其各個控制寄存器進行相關設置來實現的。隨著FPGA的廣泛應用,以及更快的數據處理速度,基于FPGA+DDS的方案對于頻率源的設計與實現具有工程實踐意義,而且還將在更多的領域得到應用。