摘要:依據標準的VGA顯示接口的顯示原理,介紹了一種利用可編程邏輯器件FPGA,并以VerilogHDL語言為邏輯描述工具來完成VGA接口的控制,從而實現簡單的彩色條紋顯示的具體方法。

關鍵宇:VGA;FPGA;VerilogHDL;彩色條紋顯示

0 引言

VGA作為一種標準的顯示接口,現已得到了廣泛的應用。傳統的VGA顯示控制主要以專門的芯片電路和通用處理器來實現,體積大且不靈活。隨著EDA技術的發展,可編程邏輯器件有了長足的發展。FPGA是現場可編程邏輯陣列器件,簡化的FPGA基本由可編程輸入輸出單元、基本可編程邏輯單元、嵌入式RAM模塊、豐富的布線資源、底層嵌入式功能單元和內嵌專用硬核等6部分組成。基于FPGA的產品設計具有開發過程簡單,投資小,可反復修改,周期短,易于產品升級等優點,故其應用越來越廣泛。本文介紹了一種用FPGA實現VGA顯示的控制器,從而實現簡易彩色條紋顯示,并在此基礎上通過外加存儲器模塊來完成圖像的實時處理與顯示的實現方法,該方法也可方便地應用于各種嵌入式便攜系統中。

1 VGA的顯示原理

VGA是IBM在1987年隨PS/2機一起推出的一種視頻傳輸標準。這個標準具有分辨率高、顯示速度快、顏色豐富等優點。根據分辨率不同,VGA又可分為VGA(640x480)、SVGA(800x600)、XGA(1024x768)等。VGA顯示采用逐行掃描方式。掃描是從屏幕的左上方開始,從左到右,從上到下。每掃完一行,電子束回到左邊下一行的開始位置,期間對電子束進行行消隱。并在每行結束時,用行同步信號對行進行同步,掃描完所有行后,再用場同步信號對場進行同步,并使電子束回到屏幕的左上方,同時對場進行消隱,并預備下一次掃描。該方法的關鍵是對時序的控制。

1.1 VGA時序

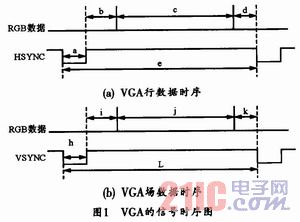

確定VGA顯示接口時序主要應考慮行同步信號(HSYNC)、場同步信號(VSYNC)、藍基色(B)、紅基色(R)、綠基色(G)這5個信號,如果能從FPGA中按其時的需要求準確發送這些信號到VGA接口,就可以實現對VGA的控制。VGA的信號時序如圖1所示,它分為行數據時序和場數據時序兩部分。

所謂行時序,就是顯示一行數據的時序。從圖1(a)可以看出,顯示一行數據需要的時序分四部分。產生行同步脈沖信號HSYNC的周期e=a+ b+c+d。其中a為同步信號時間。b為行消隱后肩時間,c為數據有效時間,d為行消隱前肩。從圖(b)可以看出,場同步時序與行同步時序類似,也是顯示一屏數據的時序,這里以行為單位。場同步脈沖信號VSYNC的周期L=h+i+j+k,其中h為同步信號時間,i為場消隱后肩時間,j為數據有效時間,k為場消隱前肩時間。

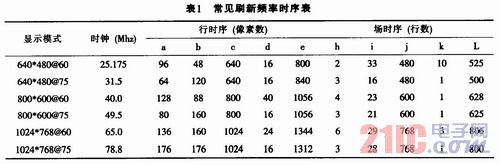

不同的分辨率下,行同步和場同步信號的周期是不同的,時序上的時間也不一樣。表1列出了VGA的常用分辨率參數。

本設計以640x480且刷新頻率為60Hz為例,其顯示器每秒掃描60場,VGA在實際工作時并不是每行掃描640個點,每場掃480行,由圖及表1可知,由于行消隱和場消隱的存在,實際是每行800個像素,每場525行。每行800個像素中包括行消隱前肩d(16個點)、行同步信號a(96個點)、行消隱后肩b(48個點)和有效點數c(640個)。每場525行中包括場消隱前肩k(10行)、場同步信號h(2行)、場消隱后肩i(33行)和有效行數j(480行)。所以,點像素的時鐘頻率為800x525x60=25.175MHz。

1.2 VGA時序控制信號的產生

VGA時序控制信號的產生包括行點計數器h_cnter、場行計數器v_enter、行同步狀態機和場同步狀態機。h_enter是800進制計數器,v_ cnter是525進制計數器。行同步狀態機有a(行同步)狀態、b(行消隱后肩)狀態、c(數據有效)狀態和d(行消隱前肩)狀態,4種狀態可根據h_ enter的值進行狀態翻轉。場同步狀態包括h(場同步)狀態、i(場消隱后肩)狀態、j(數據有效)狀態和k(場消隱前肩)狀態,4種狀態也可根據v_enter的值進行狀態轉換。其狀態轉移圖如圖2所示。

當狀態機上電復位后,行狀態機進入a狀態,此時HSYNC輸出為低,行計數器h_enter開始對25MHz的點時鐘計數,當計數到95時,轉移到b狀態,而當計數到143時,從b狀態轉移到c狀態,當計數到783時,從c狀態轉移到d狀態。在b、c、d三狀態時,HYNC輸出為高。當狀態機上電復位后,場同步狀態機進入h狀態,每當行計數器h_cater=7991時場行計數器v_enter加1,當v_enter=1時,狀態機從h狀態轉移到i狀態,當v_enter=34時,狀態機轉移到j狀態,當v_enter=514時,狀態機轉移到h狀態,此時場同步信號VSYNCS輸出為低,其他狀態輸出為高。只有當行同步狀態機在c狀態且場同步狀態機在j狀態時,才能向RGB輸入數據。

2 彩色條紋的實現

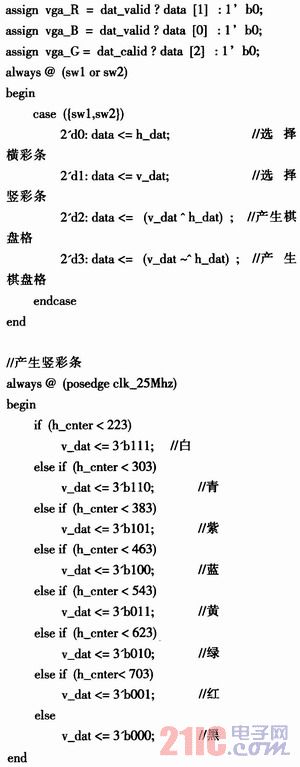

本部分包括彩色條紋模式顯示控制、橫彩條的實現、豎彩條的實現和棋盤格實現等。豎彩條可根據行計數器產生,在640個有效數據區內,每80個產生一個彩條,即對其進行8等分。橫彩條則可根據場計數器產生,在480個有效區內,每六十個產生一個彩條,也是8等分。棋盤格可由橫彩條數據和豎彩條數據異或而得到。可通過撥碼開關sw1、sw2來控制彩色條紋類型的輸出。其部分Verilog HDL代碼如下:

3 結束語

本設計主要通過FPGA來完成對VGA的控制。此方案簡單靈活且修改方便,可以充分發揮FPGA的靈活性。另外,此設計采用參數化設計,可方便的通過修改參數來滿足不同分辨率的實現,同時在此基礎上,通過外加存儲器模塊可以完成圖像的實時處理和顯示,因而可在嵌入式方面得到廣泛的應用。