摘要:AD公司的AD7266提供了先進的功能和特性。AD7266是一款差分/單端輸入、雙核2 MSPS、12位、3通道SAR A/D轉換器,為業界遙遙領先的同步采樣ADC。AD7266共有6個模擬輸入通道,能夠直接與光電編碼器連接,無需外部元器件,減化了設計并且降低了成本。這里主要對AD7266和基于AD7266的模塊設計進行介紹。

關鍵詞:AD7266;12bib 2Msps;模數轉換

0 引言

數據采集系統廣泛應用于雷達、通訊、圖像、軍工以及醫療、化工等領域,具有重要的應用價值。近年來,高速數據采集芯片(ADC)的快速發展,為用戶設計帶來了方便。選用AD公司的數據采集芯片AD7266,設計出一個具有四路一組的高速同步采樣及多組2Msps的采樣率的數據采集系統。

1 AD7266芯片介紹

1.1 AD7266概述

AD7266芯片集成有兩個獨立的高速12位連續逼近A/D轉換單元、吞吐量為2Msps、低功耗,單電源工作2.7~5.25V。在每個D/A前有三復用開關可組成三路差分或六路單端信號輸入;采樣保持放大器為帶寬10MHz的低噪聲電路。

應用先進技術設計的AD7266在吞吐量時功耗非常低,電源5V吞吐量2MSPS時最大電流4mA。當工作在休眠模式下芯片提供有電源/吞吐量節能管理功能,為電池供電提供了節能方案。模擬信號輸入范圍可選擇0~Vref或2Vref,輸出碼為二進制原碼或補碼。芯片內有2.5V參考源亦可外接100mV~2.5V的參考信號。AD7266的封裝有LFCSP和TQFP兩種。

1.2 AD7266的技術特性

AD7266為雙12位3通道ADC芯片;其最高吞吐量為2Msps;供電電源為2.7~5.25V;低功耗:在1.5Msps吞吐量電源3v時最大12mW;在2Msps吞吐量電源5V時最大30mW:寬輸入帶寬10MHz;100kHz輸入信號時70dB的SNR;片內參考2.5V;工作溫度-40~+125℃;靈活的電源/吞吐量管理;同步轉換/讀;無管道延時;高速串行接口兼容SPI/QSPI/MICROWIRE/DSP;關閉模式最大電流1 μA。其芯片內部組成見圖1。

1.3 AD7266引腳說明

AD7266芯片的引腳說明

2 設計原理

模塊主要實現多路數據采樣功能,主要用兩片AD7266構成24路單端或12路差分輸入,其中有四路可同時采樣。外圍邏輯及接口控制由CPLD、DSP或單片機構成,A/D輸出的串行數據變為并行后送入RAM或FIFO緩存。硬件結構框圖如圖2所示。

3 實現方法

3.1 輸入模擬信號預處理

輸入模擬信號主要有以下幾種:0~5V、0~10V、0~±5V、0~±10V、0~20mA、4~20mA等。AD7266的最大輸入電壓范圍為0~2×VREF即0~5V,電壓信號0~5V可用,其它信號需調理變換為0~5V。電流信號用250 Ω電阻取樣變為電壓信號后供AD7266轉換用。電路中兩片AD72 66可根據輸入信號是單端或差分分別進行設置,設置過程見圖3。

圖3中通過單端/差分控制信號SGL/DIFF*來實現對單端或差分輸入方式的控制,其中SGL/DIFF*高電平為單端輸入,SGIdDIFF*低電平為差分輸入;CS*下降沿有效。設計中通過控制單端/差分控制信號SGL/DIFF*實現不同輸入方式與不同輸入范圍,具體實現輸出二進制碼情

況見表2所示。

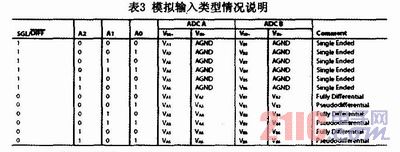

設計中通過單端/差分控制信號(SGL/DIFF*)與通道選擇控制信號(A0~A2)實現模擬輸入類型的不同,具體模擬輸入類型與通道選擇情況見表3所示。

3.2 數據采集、傳送及緩存

設計中轉換數據的定時關系如表4所示。

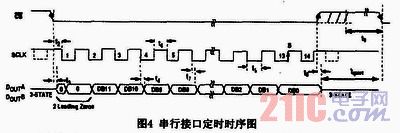

最大轉換時間TCONVERT為14×TSCLK,在電源5V、時鐘32MHz條件下轉換時間為437.5ns。精確控制CS*與SCLK的時序,從串行數字接口獲得轉換后的數據,時序見圖4。

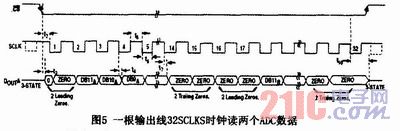

設計中用一根輸出線讀取兩個ADC數據。共需32個時鐘脈沖:其中A通道2個零標記頭、12位數據、2個零尾標記(計16位);B通道2個零標記頭、數據12位、2個零尾標記(計16位)。一根輸出線讀取兩個ADC數據時序的見圖5。

3.3 數據接口設計

串行數據在時序控制下輸出轉換為并行數據送存儲器緩存,數據接口為兼容的高速串行接口SPI/QSPI/MICROWIRE/DSP或由CPLD構成的接口。如圖2所示,本設計中采用CPLD實現接口的設計。串行數據經串行/并行轉換后輸出到FIFO進行緩存。

模塊的接口為PCI總線,由接口橋電路PCI9052實現。數據可用中斷或查詢方式進行單組或批傳送。PCI9052采用非復用、單周期讀/寫模式。

3.4 抗干擾設計

為減少高頻干擾,在制作電路板時應盡量采用多層板,在中間加上地線層和電源層。另外,由于采樣時鐘的相位抖動會對AD產生相當于模擬輸入正弦波所產生的影響,而時鐘輸入對AD7266來說相當于一個模擬輸入,因此應當盡量選擇低抖動晶體振蕩器。采用高頻時鐘經分頻后獲得需要的時鐘信號效果較好,并將時鐘電路與系統模擬電路、數字電路相隔離,以防止其產生噪聲。數字端電源、模擬端電源、數字端電源地和模擬端電源地增加電容網絡,該電容網的作用有三個:其一是與內部參考放大器一起在大頻率范圍下提供一個低阻抗源以驅動A/D內部電路;其二是提供運放動態需要的補償;其三是限制由參考電源產生的噪聲干擾。

采用直流耦合差分輸入的電路。在這種模式下,直流輸入將上升到相對參考電壓對稱擺動的點上。電路把兩個放大器配置為一個對稱單元以形成差分放大器。放大器的差分驅動電路可以把一個以地為參考電壓的單端信號轉換為一個以AD的VREF管腳電壓為中心的二倍的差分信號。單端輸入信號接到不同放大器的兩個相反的輸入端上可以驅動差分放大器,放大器可選用雙通道放大器AD8056。通常為保護AD7266不受過電壓的影響,應當在放大器的輸出端和AD的輸入之間加一個接地二極管。如果放大器和AD7266用同樣的正電源,AD就不會受到過電壓的影響。這種電路應當是最佳選擇,為信號穩定變換提供保障。

4 結束語

本設計充分體現A/D采集模塊的特點,整個設計結構緊湊、性能穩定、抗干擾能力強,并且適用于各種工業控制場合。設計上此模塊可實現四路一組的高速同步采樣及多組2Msps的采樣吞吐量。應用DSP高速處理器進行數據處理,可以很容易地實現實時諧波分析功能,且系統運行穩定性和所能達到的精確度均優于傳統的以微控制器為核心所構成的系統。