引 言

外部總線接口大都出現在功能和價格較高的高端微處理器中。例如,Freescale半導體公司生產的Coldfire和PowerPC微處理器,在低端的微控制器行列中,一般很少出現,主要原因是微控制器一般內部包含了Flash和SRAM,而不是像微處理器那樣需要外擴大容量存儲器放置代碼和運行程序。但是,微控制器也會遇到需要外擴外部總線設備的情況,筆者在某項目中需要使用MCF51QE128(以下簡稱“QE128”)微控制器連接外部Flash存儲測試數據,存取速度要求較高,因此無法使用串行接口的存儲器,只能使用具有地址線和數據線的Flash存儲器。

QE128是Freescale半導體公司推出的Flexis系列的首款產品,具有25 MHz的總線速度和多種外設模塊;還有一個特點是,其內部包含了與其他微控制器不同的快速GPIO模塊。

1 設計思路

使用微控制器中通用I/O模塊模擬實現外部總線接口是一個比較好的方法,但目前微控制器中GPIO模塊一般僅包含8個I/O口,而大容量的存儲芯片一般的地址總線和數據總線都是16位或者更高位數的。這種情況下需要使用2個GPIO端口組合才能模擬,速度不高。

QE128微控制器中的快速GPIO模塊(RGPIO)是一個比較特殊的模塊。該模塊直接與處理器的32位內部總線連接,支持字節、字和雙字的訪問,支持單周期、零等待的數據傳輸。這種特性與普通的GPIO有較大區別。區別的根本原因在于普通的GPIO模塊都是與微控制器內部的從設備總線連接的。

實現的關鍵在于,如何使一個RGPIO模塊既可以作為地址總線使用,又可以作為數據總線使用。通過對總線的分析,所有的數據通信都由主設備發起,然后發送地址信號,最后發送數據或接收總線數據,這種操作是有先后順序的。基于這種分析,將RGPIO模塊分時復用便可解決此問題。

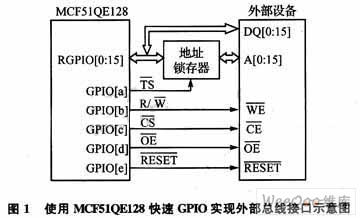

使用QE128快速GPIO實現外部總線接口的設計示意圖如圖1所示。

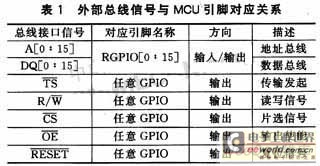

RGPIO模塊的16個引腳連接外部設備的地址總線和數據總線(此處需要注意),各信號線的含義如表1所列。其中的GPIO表示微處理器中方向可以為輸出的通用輸入/輸出引腳。需要注意的是,RGPIO模塊的16個引腳是與兩個通用I/O模塊PORTC和PORTE復用的,所以在原理圖設計時,用作控制信號的GPIO引腳應選擇PORTC和PORTE端口之外的GPIO。另外,如果RGPIO需要內部上拉,則需要設置PORTC和PORFE的內部上拉寄存器。這一點在軟件設計中的外部總線接口初始化函數Exb_Init中有體現。

2 硬件連接實例

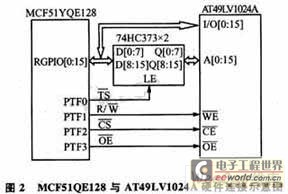

以Atmel公司的單電壓存儲器AT49LV1024A為例。AT49LV1024A存儲容量為128 KB(64K×16位),工作電壓為3.3 V,可以直接與QE128連接。AT49LV1024A的地址線和數據線寬度均為16位,控制信號包括芯片使能信號CE、輸出使能信號OE和寫使能信號WE。

圖2為QE128與AT491LV1024A的硬件連接實例。在本實例中,鎖存器使用的是2片TI公司的8路D型鎖存器74HC373.2片74HC373的鎖存使能LE(Latch Enable)引腳相連,通過QE128的TE信號控制來選擇地址總線和數據總線。

地址/數據信號外的其他控制信號使用GPIO控制。本實例中使用PTF端口的4個引腳。

3 軟件設計

RGPIO模塊常用的寄存器共有以下6個:數據方向寄存器RGPIO_DIR、數據寄存器RGPIO_DATA、引腳使能寄存器RGPIO_ENB、數據位清零寄存器RGPIO_CLR、數據位置位寄存器RGPIO_SET和數據位翻轉寄存器RGPIO_TOG。6個寄存器均為16位寄存器。其中前面3個寄存器是其他的GPIO口都具有的,后面3個寄存器是RGPIO模塊比較有特色的地方。這3個寄存器與數據寄存器RGPIO_DATA的每一位是對應的,將RGPIO_CLR中某一位置為0,則相應RGPIO_DATA的對應位就會清零。類似的,將RGPIO_SET或RGPIO_TOG的某一位置1,則會將RGPIO_DATA對應位置1或反轉。相對于普通MCU中的讀取數據至累加器→置位→寫入寄存器的操作。RGPIO可以減少操作的時間,具體比較詳見QE128參考手冊中RGPIO一章。

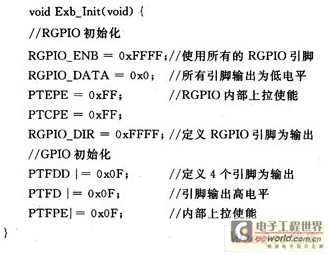

了解底層寄存器后,筆者對外部總線接口實現的底層函數做了通用性的封裝,共包括3個函數:外部總線接口初始化函數void Exb_Init(void);外部總線寫函數void Exb_QueuedWrite(word*pAddr,word*pData,bytenTransfer);外部總線讀函數void Exb_QueuedRead(word*pAddr,word*pData,byte nTransfer)。Exb_QueuedWrite函數進行nTransfer次寫操作,將數據數組中的數據寫入地址數組中的地址。Exb_QueuedRead函數進行nTransfer次讀操作,將地址數組中地址對應的數據讀出放人數據數組中。其中Exb_Init函數代碼如下:

根據這3個通用底層接口函數便可以編寫針對不同的外部設備的函數進行操作。本文以對AT49LV1024A的Flash存儲器進行數據寫入和讀出操作為例,基本滿足常用功能的需要。具體的AT49LV1024A存儲器的命令序列請參考該芯片的技術手冊。

結 語

MCF51QE128微控制器的快速GPIO模塊是具有特色的一個模塊。本文在對該模塊進行分析的基礎上給出了實現高速外部總線的方案,以及硬件連接和軟件底層通用接口,解決了QE128連接外部高速總線設備的問題。