摘要:基于DDS和VHDL硬件描述技術,采用大規模可編程門陣列FPGA,實現了FSK和PSK數字調制。介紹了m偽隨機基帶碼元發生器、跳變檢測器和DDS信號發生等模塊。系統參數易修改、可移植性強、性能穩定。

關鍵詞:FSK/PSK;DDS;m偽隨機序列;FPGA

在通信領域,經常需要將基帶信號進行某種調制,使其適合于信道傳輸。FSK、PSK即為常用的兩種數字調制方式。傳統模擬調制系統中大量采用分立元件,體積較大,電路復雜。由于模擬元件自身參數的離散性和受環境溫度、濕度等因素影響,導致系統穩定性較差。本文提出了一種基于DDS技術的FSK/PSK調制的數字實現方法,提高了系統的穩定性,克服了模擬調制的弊端。

1 FSK/PSK調制原理

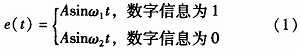

頻移鍵控(Frequency Shift Keying,FSK),是利用載波的頻率參量來攜帶數字信息的調制方式。常用的是二進制頻率鍵控信號,即2FSK,用載頻w1表示數字信息“1”,用載頻w2表示數字信息“0”,而w1和w2之間的變化是瞬間完成的。

相移鍵控(Phase Shift Keying,PSK),它是受鍵控的載波相位按數字基帶脈沖的規律而改變的一種數字調制方式。這種以載波的不同相位直接表示相應數字信息的相位鍵控,通常被稱為絕對移相方式。當基帶信號為二進制數字脈沖序列時,所得到的相位鍵控信號為二進制相位鍵控,即2PSK,它的表達式為

![]()

式中,φ(t)由數字信息“0”“1”控制。在絕對移相中,因為φ(t)選用的參考相位基準就是未調制的載波,所以φ(t)就是載波的絕對值。一般說來,數字信息為“1”時,φ(t)=0,數字信息為“0”時,φ(t)=π。即

![]()

FSK、PSK的調制示意圖如圖1所示。

2 FSK/PSK調制邏輯設計與仿真

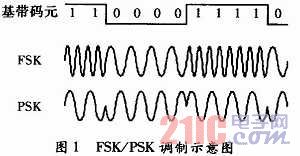

FSK/PSK調制邏輯共分為3個部分:分頻器、m序列產生器和FSK/PSK調制器。分頻器用于產生FSK/PSK調制器和m序列的基準時鐘信號f1,f2和f3,m偽隨機序列器產生基帶碼元。FSK/PSK調制器根據輸入的基帶碼元和基準時鐘產生相應的FSK或PSK信號,調制模式由mode模式選擇。當mode為低電平時,表示選擇FSK調制,當mode為高電平時,表示選擇PSK調制。FSK/PSK調制器輸出的數字調制信號經DAC轉換成模擬信號輸出。邏輯模塊框圖,如圖2所示。

2.1 分頻器

分頻器對頻率為f0的時鐘輸入信號clk分別以分頻系數D1,D2和D3產生FSK/PSK調制器和m序列的基準時鐘信號f1,f2和f3。其關系如式(1)所示。

![]()

f1和f2決定了FSK調制信號的兩個載波頻率,f2決定了PSK調制信號的載波頻率,f3決定了基帶碼元速率。為了保證每個基帶碼元的寬度T是載波周期的整數倍,在選擇分頻系數時應滿足式(2)。

![]()

式中,M為D1和D2的最小公倍數。

2.2 m序列產生器

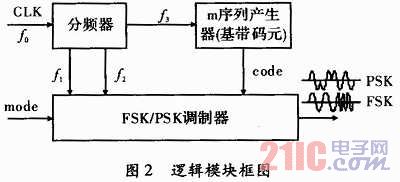

m序列是由多級移位寄存器或其他延遲元件通過線性反饋產生的最長的碼序列。m序列的最大長度取決于移位寄存器的級數,而碼的結構取決于反饋抽頭的位置和數量。其特點是:隨機特性、預先可確定性、循環特性。

本設計利用帶有兩個反饋抽頭的3級反饋移位寄存器得到一串7位循環序列“1110010”,并采取措施防止進入全“0”狀態。通過更換時鐘頻率,可以方便地改變輸入碼元的速率。這一系列的循環序列碼作為基帶信號碼元。其電路結構如圖3所示。

2.3 FSK/PSK調制器

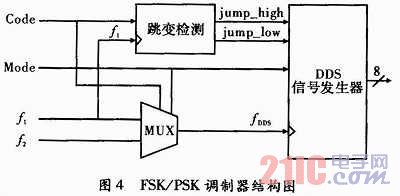

FSK/PSK調制器由時鐘選擇模塊、跳變檢測模塊和DDS信號發生模塊3部分組成。原理如圖4所示。

2.3.1 時鐘選擇模塊

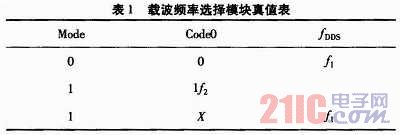

載波頻率選擇模塊的兩個輸入端分別接時鐘信號f1和f2,其輸出信號fDDS作為DDS信號發生模塊基準時鐘信號。該模塊的輸出真值表,如表1所示。

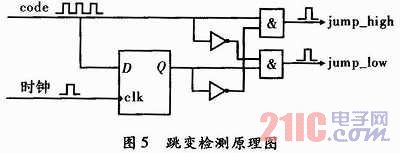

2.3.2 跳變檢測模塊

跳變檢測模塊用于檢測基帶碼元的變化情況。當基帶碼元上升或下降沿到來時,其對應的輸出端產生與時鐘周期等寬的高脈沖信號jump_high或jump_low。該信號提供給下一級DDS的相位累加器,來控制累加器的相位偏移。跳變檢測原理圖如圖5所示。

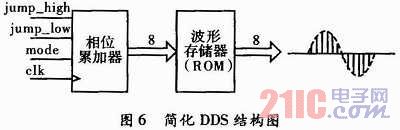

2.3.3 DDS信號發生模塊

DDS是一種應用數字技術產生信號波形的方法。由于模塊中只需產生兩種頻率和相位的波形,因此對DDS的設計中省略了頻率控制字和相位控制字等部分。頻率改變通過時鐘選擇模塊選擇不同的基準時鐘來實現。簡化后的DDS主要由相位累加器和波形ROM組成,如圖6所示。

相位累加器在頻率為fc的時鐘信號clk控制下,以步長K作累加,輸出的N位二進制作為波形存儲器ROM的地址,以該地址對ROM進行尋址。則DDS輸出波形的頻率f0的表達式,如式(3)所示

![]()

本設計中,取K=1,N=8,波形存儲深度為100個采樣點,則可得f0=fc/100。jump_high、jump_low、mode和clk通過控制相位累加器的輸出來實現:FSK/PSK波形合成輸出。當mode為低電平時,即FSK調制模式時,jump_high和jump_low中任一信號出現高脈沖時,累加器清零,然后根據clk進行循環累加。當mode為高電平時,即PSK調制模式時,累加器的工作方式如表2所示。

ROM表是對選取的采樣點進行量化、編碼,通過相位累加器的地址值查找ROM表中的內容,以得到可合成正弦波的正弦點的值。其原理是:在橫軸上取100個采樣點,將縱軸的正弦值[-1,+1]總體提升一個單位,即將正弦值的取值區間變為[0,2],并將其均勻地分成255個量化區間,再對這255個量化間隔在00000000~11111111進行編碼,即將所取的采樣點的幅度值對應到各個量化間隔。

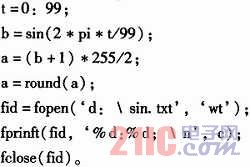

具體實現方法,可通過用Matlab產生一個mif文件。Matlab源程序如下:

3 系統仿真結果

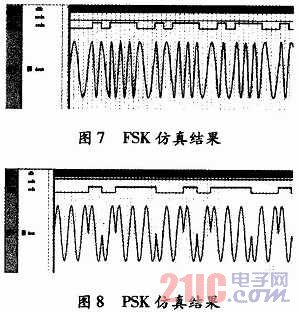

Altera公司的QuanusⅡ集合了綜合和仿真的功能。本設計在Quartus II中完成了VHDL的代碼編寫和綜合布線,并對整個設計系統進行了時序仿真,仿真結果如圖7~圖8所示。其中,clk為外接輸入100 MHz時鐘;mode為模式控制鍵;code為由m序列產生的偽隨機碼,用做基帶碼元;dout為輸出的調制結果。

圖7中,mode的值為“0”,說明是FSK調制方式。從圖中可以看出,當基帶碼元code為“0”時,dout輸出低頻調制波。當基帶碼元code為“1”時,dout輸出高頻調制波。實現了用不同的頻率變化傳遞數字信息,完成了FSK調制。

圖8中,mode的值為“1”,說明是PSK調制方式。從圖中可以看出,dout的輸出波形頻率是單一的,當基帶碼元由“1”向“0”跳變時,波形出現倒π現象,實現了通過相位變化傳遞信息,完成了PSK調制。

4 結束語

介紹了一種基于DDS技術的FSK/PSK調制方式的FPGA實現方法。整個系統采用VHDL硬件描述語言進行軟件編寫,參數修改方便,并具有較強的可移植性。其原理簡單,易于實現。相比傳統模擬調制方式,這種數字調制方式具有較好的穩定性和抗干擾能力,在通信領域中具有較強的實用性。