摘要:為了解決目前記錄系統" title="系統" target="_blank">系統容量小、存儲" title="存儲" target="_blank">存儲速度低的問題,采用性能優良的固態NAND型FLASH為存儲介質,大規模集成電路FPGA為控制核心,通過使用并行處理技術和流水線技術實現了多片低速FLASH時高速" title="高速" target="_blank">高速數據的存儲,提高了整個系統的存儲容量和存儲速度。針對FLASH內部存在壞塊的自身缺陷,建立一套查詢、更新和屏蔽壞塊的處理機制,有效的提高了數據存儲的可靠性。

關鍵詞:高速;流水線;FLASH;FPGA

0 引言

在數據采集存儲系統中,往往需要對采集后的數據進行存儲以方便后續分析處理。隨著我國航空電子技術和雷達成像技術的快速發展,分辨率和采樣率大幅提升,由此便帶來了高速大容量" title="大容量" target="_blank">大容量數據的存儲問題。同時存儲系統又要求掉電存儲數據并具有良好的抗振動能力,因此存儲電路通常采用非易失的電路芯片構成,而傳統的DOC,E2PROM等存儲技術由于容量小、速度低等缺點已經不適用高速大容量數據的存儲。快速發展的閃速存儲器(FLASH MEMORY)因其具有體積小、成本低、功耗小、壽命長、抗振動和寬溫度適應范圍等特點,逐漸成為高速大容量存儲系統設計" title="設計" target="_blank">設計的主流方案。

1 FLASH的控制邏輯

目前FLASH芯片主要分為NOR型和NAND型。NOR型具有可靠性高,隨機讀取速度快等優點,適用于程序代碼的存儲。NAND型是一種線性存儲設備,適用于大容量數據和文件的存儲。 K9WBG08U1M是三星公司推出的一款NAND型FLASH芯片,存儲容量達到4 GB,它內部由兩片2 GB的FLASH構成,通過片選信號CE1/CE2進行選擇控制,每片FLASH由8 192個塊組成,每塊有64頁,每頁能存儲(4 096+128)個字節的數據。因此,訪問芯片需要5個地址周期,其中3個周期的行地址用來確定某一頁,2個周期的列地址用來確定每頁的某個字節。對FLASH進行的操作主要有:存儲、讀取和擦除。由于指令、地址和數據復用芯片的8個I/O口,因此需要2個控制信號CLE和ALE分別鎖存指令和地址。

存儲操作一般使用基于頁的連續存儲模式,所有的命令字、地址、數據都是在![]() 的上升沿寫入。首先輸入命令字80H,隨后緊跟輸入5個周期的地址,并且在

的上升沿寫入。首先輸入命令字80H,隨后緊跟輸入5個周期的地址,并且在![]() 的上升沿將串行輸入數據加載進芯片內部的數據存儲器中,最后輸入頁編程確認命令10H便可啟動存儲操作,數據將自動的從片內寄存器寫入存儲體中,隨后可通過輸入讀狀態命令70H來判斷I/O端口輸出是否為O來檢測此次編程操作的成功性。

的上升沿將串行輸入數據加載進芯片內部的數據存儲器中,最后輸入頁編程確認命令10H便可啟動存儲操作,數據將自動的從片內寄存器寫入存儲體中,隨后可通過輸入讀狀態命令70H來判斷I/O端口輸出是否為O來檢測此次編程操作的成功性。

讀取操作通常也以頁為單位進行。輸入起始命令字00H、5個周期的地址和結束命令字30H后,對應地址的一頁4 096個字節數據便傳輸給數據寄存器,隨后在的下降沿將數據驅動到I/O總線輸出。

擦除操作與存儲、讀取操作略有不同,它是以塊為單位進行的,因此只需要3個周期的地址即可。在輸入擦除命令后,芯片便自動進行擦除操作,將存儲體內的數據全部恢復為“FF"狀態,隨后也可通過輸入讀狀態命令字70H判斷端口輸出是否為0來檢測此次擦除操作的成功性。

2 系統存儲關鍵技術

K9WBG08U1M一頁的存儲容量是4KB,最短25ns時間寫入一個字節。因此,芯片接口的寫入速度最高為40MB/s。芯片的存儲時間分為加載時間和編程時間兩部分,寫滿一頁所需的命令、地址和數據的加載時間總共為102.5μs,編程時間的典型值為200μs,最大編程時間為700μ-s。為了減小數據在存儲過程中出錯的概率,設計中使用最大的編程時間進行計算,因此對單片FLASH而言,存儲速度最高可達5.1MB/s。

2.1 并行總線處理技術

按照操作FLASH的傳統方法,存儲完一片FLASH后,再進行下一片FLASH的操作,這樣最高存儲速度也只是單片FLASH的存儲速度即5.1 MB/s,顯然無法適用于高速數據傳輸存儲的場合。通過并行處理技術可以很直觀的提高存儲速度,具體實現方法是:將N片低速FLASH芯片并聯起來,使用相同的控制線、片選線和讀寫信號線,構成一個多位寬的FLASH組。這樣N片FLASH并行工作,進行相同的操作,存儲量可達到單片FLASH的N倍,所以理論上存儲速度也是單片FLASH的N倍。

2.2 流水線技術

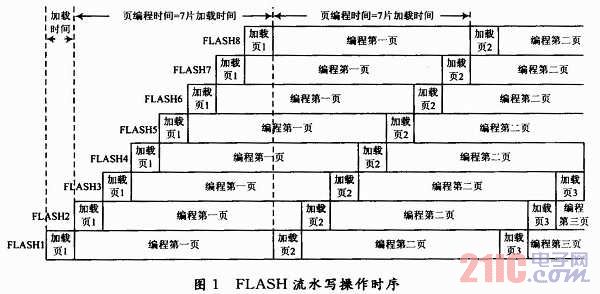

流水線技術在計算機領域得到廣泛運用,它是在程序執行時多條指令重疊進行操作的一種準并行處理實現技術。借鑒這種技術在進行FLASH存儲時可以大大節省存儲時間,提高存儲速度。FLASH每頁數據的加載時間和編程時間是器件本身所決定的,當加載完一頁數據后,FLASH就進入忙狀態,此時需要等待加載的數據自動編程,即將數據從寄存器中寫入存儲單元內,這期間不能進行其余的操作,當編程結束后,FLASH才恢復空閑狀態,此后才能進行下一頁數據的加載,然后再進行編程。因此如果可以善加利用編程時間,使FLASH在進行本頁數據編程的同時去執行下一頁數據的加載,這樣便可節省存儲時間,提高速度。加載完一頁數據的時間約為102.5μs,最大編程時間為700μs,這樣在每頁的編程時間內可以完成7次的FLASH加載操作(700/102.5≈7),由此畫出8級流水操作的時序圖如圖1所示。

圖1中每片FLASH都分為加載時間和編程時間,當第一片FLASH完成第一頁的數據加載后進入數據編程階段。此時第二片FLASH開始進行第一頁數據加載,加載完成后也進入數據編程階段。然后依次對第三片到第八片FLASH進行相同的操作,當第八片FLASH也完成了第一頁數據的加載后,此時系統耗費的總時間約為7×102.5=717.5μs,大于單片FLASH的最大編程時間700μs即第一片FLASH已經完成了數據編程,可以接著進行第二頁的數據加載。當第二頁數據加載完成后,第三片FLASH便完成了第一頁的數據編程,可以接著進行隨后操作。這種循環流水操作,使FLASH在高速存儲過程中不必去考慮頁編程是否完成,節省了頁編程時間,從而使存儲速度近似達到芯片接口寫入速度即40 MB/s。由此可見,運用流水操作技術的存儲速度將是單片FLASH存儲速度的8倍,實現了FLASH的快速高效無丟失存儲。

2.3 壞塊處理技術

NAND型FLASH芯片在出廠時內部會隨機分布有壞塊,壞塊是指一個塊內含有一位或更多位的數據單元無法進行操作,并且在芯片的長期使用過程中不可避免地還會增加新的壞塊。不允許對壞塊進行擦除和編程操作,這樣會導致數據的存儲錯誤。因此在操作FLASH的過程中,需要建立一個壞塊管理列表,將芯片內部的所有壞塊信息寫入列表中,并且在出現新的壞快時能夠及時的更新壞塊管理列表。

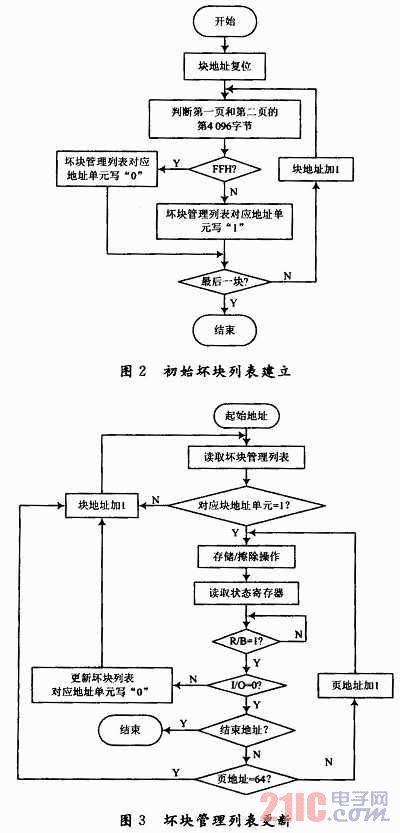

FLASH內部的壞塊有兩種,一種是芯片出廠時本身含有的初始壞塊,此類壞塊廠家已經標明,通過讀取芯片每塊第一頁和第二頁的第4 096個字節來進行判斷,如果均是“FFH”,則認為此塊是有效塊,否則便為壞塊。另一種則是在使用過程中新增加的壞塊,可以通過讀狀態寄存器來進行判斷。

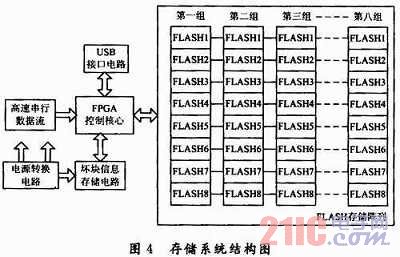

壞塊管理列表的建立和更新可以使用將其內部地址空間和FLASH內部塊地址一一對應的映射方法,當發現是壞塊時,只需將列表中對應此塊地址的單元寫入1比特“0”信息即可,而其余的地址單元仍是1比特“1”信息代表有效塊。在對FLASH的每一塊進行操作之前,需要先讀取壞塊管理列表中對應此塊地址單元的信息,如果發現是壞塊就跳過此塊不進行操作,然后再進行下一塊的判斷,直至找到有效塊時再進行操作。壞塊管理列表的建立和更新分別如圖2、圖3所示。

3 系統設計

3.1 系統硬件結構組成

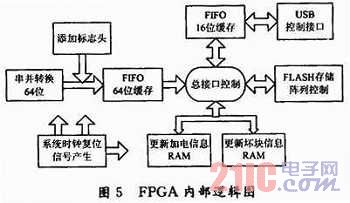

本文所設計的高速大容量存儲系統的結構框圖如圖4所示。系統中FLASH芯片選用三星公司的K9WBG08U1M,存儲陣列分為8組,采用流水線操作,每組由8片FLASH并聯共用控制線,各組對應行的FLASH共用數據線。系統存儲容量達到4×8×8=256 GB,存儲速度理論值為40MB/ s×8=320 MB/s。FPGA是整個系統的控制核心,它將產生各種復雜的邏輯時序來控制外圍芯片協調有序地工作,選用Altera公司StratixⅡ系列的EP2S60F484I4芯片,該芯片有48 352個邏輯單元,內置存儲RAM容量達2.5 MB,滿足緩存數據的要求。USB接口電路選用CYPRESS公司的CY7C68013A,該芯片集成了一個8.5 KB片上RAM的8051核、4 KB的FIFO以及USB 2.0收發器,滿足USB2.0通信協議,是進行USB2.0開發的常用芯片。壞塊信息存儲電路用于存儲和更新FLASH存儲陣列隨機出現的壞塊位置,它必須是非易失零出錯的存儲介質,因此選用AMD公司的Am29LV800B NOR型FLASH,存儲容量為8 Mb,保證無壞塊。

3.2 系統具體實現

FPGA是整個硬件系統的核心,它完成電路的復雜時序控制,使系統有條不紊地運行。FPGA上電后進行初始化和加載配置信息,完成后進入工作狀態。首先根據USB接口電壓判斷是進入數據記錄狀態還是數據下載狀態,然后分別按照各自流程進行工作。FPGA內部邏輯設計如圖5所示。

由于FLASH存儲陣列是8片并聯一起操作,因此數據總線寬度便為64位,同時由于USB的接口數據寬度為16位,因此系統中使用了2個FIFO分別進行緩存。在系統記錄狀態下,前端接收到高速串行數據后首先進行串/并轉換,然后為其添加一個64位的標志頭一并存入FIFO緩存,標識頭是用來標記每次的加電情況,方便FLASH數據的分段下載。同時將外部NORFLASH內所存儲的壞塊信息讀入FPGA內部建立的RAM中,在總接口控制下,屏蔽FLASH存儲陣列內部的壞塊,并按一定順序將數據寫入FLASH芯片。由于數據在存儲過程中會產生新的壞塊,因此在每頁寫操作結束后需判斷此頁編程是否成功,若編程失敗,則對照此壞塊地址更新RAM中的壞塊信息,等待FLASH的存儲操作結束后,再將更新后的RAM數據寫入外部NOR FLASH進行保存。

在系統下載狀態時,首先對FLASH內部的存儲數據進行搜索,找到標識頭所在存儲陣列中的位置并將此位置信息寫入FPGA內部的RAM中,這樣便可知道每次加電后存儲數據在FLASH陣列中的起始塊位置和所占塊的容量。然后通過上位機軟件輸入起始位置,塊容量和下載命令后,FPGA內部的總接口控制便可根據這些命令信息,同時屏蔽壞塊后將FLASH存儲陣列中相應的數據寫入16位FIFO緩存中,隨后便可通過USB接口下載至計算機進行數據分析。

4 結語

隨著基于NAND技術的FLASH固態存儲器的快速發展,其存儲密度也越來越大,而體積、功耗和成本卻在減小,這使得NAND型FLASH在大容量高速存儲設備的研制中得到廣泛應用。本文針對單片FLASH存儲速度慢的缺點,將多片低速FLASH芯片并行起來工作,同時又運用流水線操作節省了FLASH的自身編程時間,從而使得整個存儲系統的存儲速度大大提高。針對NAND FLASH內部存在壞塊的問題,建立了一套完善的壞塊處理機制,使得系統能夠準確的存儲數據,保證數據的可靠性。使用FPGA對FLASH存儲陣列及USB下載電路進行控制,充分發揮了FPGA處理復雜邏輯的特點,簡化了系統的硬件結構。