目前的嵌入式系統中, 軟件代碼一般存儲在諸如EEPROM、F lash等存儲器中, 但其中存儲的程序代碼易被讀取, 非法拷貝, 是其致命弱點。

目前為止, 有些廠商采取先預先加密軟件代碼, 寫入存儲器中, 執行時, 通過軟件解碼來實現對代碼的保護, 但是這種方法效率低, 成本高, 實用性比較低; 現有的一些硬件加解密系統, 只能保護有限類型的NAND- Flash存儲器中的代碼, 并且系統中的密匙一旦固化就無法改變。針對這些局限性, 本文提出了一種全新的嵌入式產品軟件代碼保護系統, 該系統適用于目前通用的基于I2C、SPI總線的EEPROM 和F lash;以及主流廠商的NAND- Flash。

1 嵌入式軟件代碼保護系統構成

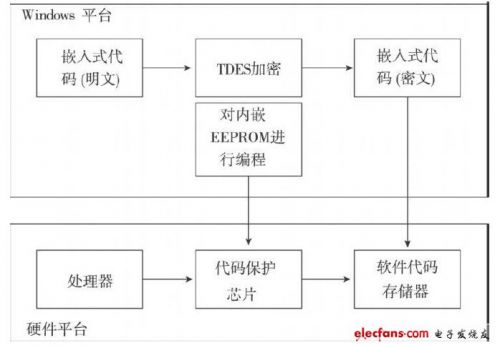

嵌入式軟件代碼保護系統由兩部分組成: PC 機上運行的TDES加密軟件和硬件電路中隔離處理器與軟件代碼存儲器直接通路的代碼保護芯片組成, 如圖1所示。PC機上的TDES 程序對嵌入式軟件代碼進行加密, 生成密文形式的數據, 并寫入軟件代碼存儲器中, 供嵌入式系統使用; 同時通過GPIO 口模擬I2C 或者SPI通信協議, 對代碼保護芯片中, 存放相關重要數據的EERPOM 區域進行配置: 達到諸如更改代碼保護芯片中TDES的密匙的目的。

代碼保護芯片內嵌于嵌入式系統的硬件電路中, 用戶可以選擇隔離處理器和指令代碼存儲器之間的通路: 所有寫入存儲器的數據將被加密后才寫入其中; 所有從存儲器中讀出的數據將被解密后才送回給CPU執行; 用戶也可以選擇不隔離處理器和存儲器之間的通路: 讀寫操作將不會進行任何加密和解密。

圖1 嵌入式軟件代碼保護系統

2 代碼保護芯片設計

2. 1 內部結構簡介

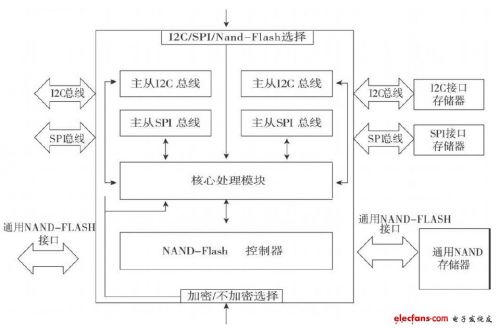

代碼保護芯片隔斷了原有嵌入式系統處理器和軟件代碼存儲器之間的直接通路, 如圖2所示。該系統主要分成主從I2C 總線接口模塊、主從SPI總線接口模塊、Nand- Flash通信模塊以及核心控制模塊。

如果用戶選擇I2C 接口, 芯片將通過I2C總線和存儲器進行通信, 如果用戶選擇SPI接口, 芯片將通過SPI總線和存儲器進行通信, 否則芯片將通過NAND- F lash模塊和存儲器進行通信。

如果用戶選擇加密模式, 那么處理器和存儲器之間的通路將被隔斷, 所有準備寫入存儲器的數據經過TDES加密后才寫入其中, 所有從存儲器讀入的數據經過TDES解密后才送回至處理器執行; 如果用戶選擇不加密模式, 那么處理器將直接和存儲器進行通信, 代碼保護芯片將不啟動任何加密/解密操作。這種設計方式, 使得芯片可以適用于更多的嵌入式系統, 同時也給予用戶最大限度的靈活性。

圖2 代碼保護芯片架構

2 .2 核心處理模塊

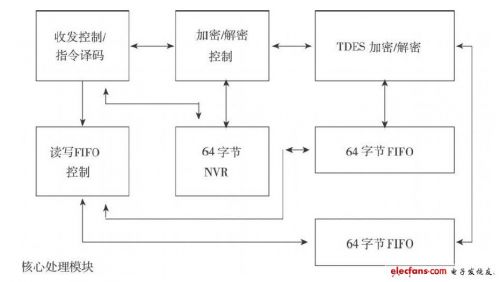

核心處理模塊是整個系統的核心部分, 如圖3所示: 主要完成指令譯碼、控制FIFO 的讀寫、控制TDES加密/解密的運行, 控制I2C、SPI、通用N and- Flash模塊和外界的數據接收和傳送以及對內部EEPROM進行操作。當代碼保護芯片接收到處理器發出的讀數據命令后, 將從存儲器中預取64 字節的數據, 然后進行TDES解密。解密的同時, 芯片再次從存儲器預取64字節的數據, 寫入內部的另外的64字節FIFO 中: 乒乓FIFO 架構的設計以及采用流水線技術的TDES加密/解密, 大大提高了代碼保護芯片的效率。

圖3 核心處理模塊框圖

2.3 芯片內部EEPROM 存儲數據內容介紹

由于存儲器出自不同的廠商, 因此對于存儲器的讀寫等命令存在著一定的差異, 為了滿足系統對不同廠商芯片的適用性, 該代碼保護芯片內部內嵌了一個64字節的可讀寫EEPROM, 用來存放一些特殊的數據,用戶可以通過特殊的命令, 達到對相關地址的寫操作。相關地址存放數據如下所示:

地址0x00至0x05: 分別代表SPI讀操作指令代碼、SPI寫操作指令代碼、SPI寫狀態寄存器指令代碼、SPI讀狀態寄存器指令代碼、SPI關閉寫操作指令代碼、SPI允許寫操作指令代碼。

地址0x06至0x07: 分別代表I2C 器件地址、I2C有效地址字節數。

地址0x08至0x0D: 分別代表NAND - Flash 讀操作指令代碼1、NAND - FLASH 讀操作指令代碼2、NAND - FLASH 讀操作指令代碼3 、NAND- FLASH 頁編程操作指令代碼1、NAND- FLASH 頁編程操作指令代碼2、NAND- FLASH有效地址字節數。

地址0x0E至0x25: 分別代表24字節的TDES密匙。

地址0x25以后的區域為保留區域, 預留給將來使用。

3 代碼保護芯片設計實現

3.1 綜合結果

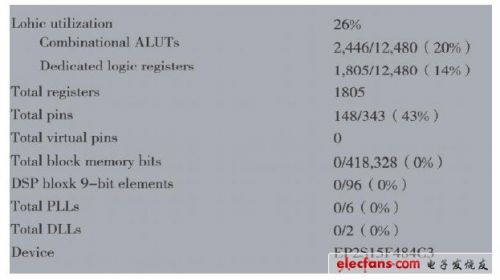

本文設計的嵌入式軟件代碼安全保護芯片, 使用V erilog 語言進行編程, 并進行了功能驗證, 使用Quartus- 7 2進行了綜合及布局布線, 并完成了后仿真。實驗結果表明, 整個系統適用的時鐘工作頻率介于4MH z和96MH z之間, 滿足目前主流的嵌入式系統的數據讀寫速度。使用Stratix II系列的EP2S15F484C3器件進行了綜合, 綜合結果見圖4:

圖4 綜合結果

3.2 系統性能分析

3.2.1 基于I2C /SPI接口的存儲器

當代碼保護芯片第一次從處理器接收連續讀操作指令后, 由于代碼保護芯片需要從存儲器預取64 字節, 所以必須等待1 28ms(和存儲器通信的頻率為400K) ; 因為代碼保護芯片采取流水線技術的TDES, 所以第51個時鐘周期后, 解密后的數據就可以傳送回處理器, 由于在向處理器傳送數據的同時, 代碼保護芯片也同時從存儲器接受數據, 因此, 處理器不需再等待額外的時間, 就可以連續的從代碼保護芯片接受解密后的指令。因此當系統時鐘工作頻率為4MH z, 處理器必須等待1 29275ms后, 才可接收數據; 當系統始終工作頻率為96MH z, 處理器只須等待1 28053m s后, 就可接收數據。

3.2.2 N and- Flash存儲器

目前主流的Nand- F lash器件, 其最大的串行讀出數據時間為50ns, 預取64 字節, 必須等待3200ns,TDES解密時間同節3.1.1, 因此當系統時鐘工作頻率為4MH z, 處理器必須等待15 95us后, 才可接收數據;而當系統時鐘工作頻率為96MH z, 處理器只須等待3 73125us后, 就可接收數據。

本文設計的嵌入式軟件代碼保護系統, 已經成功地對國家半導體公司的CAT1026芯片存儲器進行解/加密讀寫操作, 雖然基于TDES的加密和解密的過程降低了嵌入式系統的運行速度, 但是以少量降低性能換取更高的產品安全性, 對于用戶來說, 是完全可以接受的。它對于保護公司的知識產權、提高產品的市場壽命有著重要的、積極的意義, 有著極為廣泛的應用前景。