1 TMs320 F28335結構特點

TMS320F28335采用高性能靜態CMOS技術,具有150 MHz的工作頻率。系統組成包括:包含浮點運算單元的CPU、片內存儲器、中斷管理模塊、片內集成外設。TMS320F28335的CPU采用與TMS320F28x相同的32位定點低功耗CPU,但其中包含一個浮點運算單元(FPU),其32×32位的MAC操作及8級流水線技術使程序的執行不用高速存儲器也能達到較高的速度。中斷擴展模塊(PIE)共支持58個外設中斷,能夠快速響應中斷。片上存儲器包括最高達512 kB的閃存與68 kB的RAM,代碼安全性模塊具有128位密碼保護,用來保護Flash/OTP和部分SRAM,從而保證了相關寄存器的數據安全。BOOTROM中固化的代碼,提供了多種DSC啟動方式。

TMS320F28335支持最多88個通用I/O口(GPIO),GPIO的多路開關寄存器(GPIO MUX)可以將一個引腳最多設置成4種可選工作模式:3種獨立的外設模式和1種通用的I/O模式,提高了引腳的利用率,使硬件設計時的布線更加簡便合理。GPIO0-GPIO63引腳可以連接到8路外部中斷,使DSC能夠對外部設備進行有效的中斷控制。

TMS320F28335內部首次引入了6路直接存儲器存取(DMA)模塊,為數據在CPU不參與運算的情況下在外設和存儲器之間進行傳輸提供了一種硬件方法,為其他系統函數的執行釋放了帶寬。另外,DMA可以重新布置內存中的數據,優化CPU處理。DMA模塊是基于事件工作機制的,它需要外設中斷觸發開始數據傳輸,6個DMA通道可以分別設置中斷觸發源,并且每個通道包含自己的獨立PIE級中斷,以便CPU能夠控制DMA傳輸的起始或完成。

同時,TMS320F28335中包含了多種串行通信外設,其中最多可以包括2個CAN通信模塊,3個SCI(UART)模塊,1個SPI模塊和2個McBSP模塊,并加入了1個I2C模塊。這些外設加強了DSC的通信功能,為多控制器聯接提供了豐富的資源。此外,TMS320F28335支持IDLE,STANDBY和HALT這3種低功耗工作方式,并可通過關閉各個獨立片上模塊的時鐘,降低整體功耗,適合于電池供電等低耗電量硬件系統。

2 硬件系統設計

2.1 方案概述

該系統主要功能是DSC通過ADC采樣芯片對12路模擬信號進行同時采樣。在DSC中進行數據處理后通過異步串行收發器上傳到上位機。同時,上位機也可以通過異步收發器向DSC發送預先制定的命令,來控制信號處理板的工作模式和狀態。

按照功能要求,整個硬件電路可分為3部分:電源模塊、數字部分和模擬部分。其功能結構框圖如圖1所示。

2.2 電源模塊設計

整個處理板的外部輸入電壓為5 V和±12 V,分別通過對應的電壓轉換芯片為模擬和數字部分提供不同的電壓幅值。對于數字部分,電源模塊需要為DSC提供1.9 V的核電壓,同時為DSC的外圍和其他芯片提供3.3 V的外圍電壓。本系統選用LT1963AES8集成芯片提供1.9 V,LT1963AEST-3.3集成芯片提供3.3 V。對于模擬部分,系統要求輸入ADC的信號幅值范圍在±12V內,所以系統分別選用LT1086IT-12和LT11 75IT把輸入的±15V電壓轉換成±12V。

2.3 數字電路設計

數字部分電路主要是以DSC為中心的應用電路。該部分主要是對ADC傳送的數據進行處理、存儲,同時完成DSC同上位機的通信和數據傳輸。由圖1可以看到,它包含以下幾個部分。外圍SRAM擴展,EEPROM擴展電路,SCI上位機通信接口電路。

2.3.1 外圍SRAM擴展

考慮到TMS320F28335片內的RAM資源有限,加上程序空間和數據空間RAM僅為34 kB,16位數據寬度,從而需要對片內的RAM進行擴展,來滿足較大量程序的運行。本系統選用Cypress公司的CY7C1011CV33-12ZSXE集成芯片,利用TMS320F28335提供的XINTF接口完成片外RAM的擴展。

XINTF是TMS320F28335所提供的一個非復用異步總線,用來完成外部異步器件的擴展。XINTF可以映射外設到3個固定的內存映射區域,當外部資源掛接到某個區域時,則需要通過XINTF的一個片選信號來進行外部資源的選定。

CY7C1011CV33-12ZSXE是一個CMOS的靜態RAM存儲器,其容量大小為64 kB,16位數據寬度。圖2是外圍SRAM擴展電路連接圖。

如圖2所示,本系統選用ZONE7區域作為RAM的外圍擴展。DSC通過其XZCS7管腳向片外SRAM發送片選信號。WE信號用來控制DSC對片外SRAM的讀寫,當DSC的XWEo管腳為低電平,則DSC對片外RAM進行讀寫操作;XWEo為高電平,同時DSC的XRD管腳為低電平,則為讀操作。

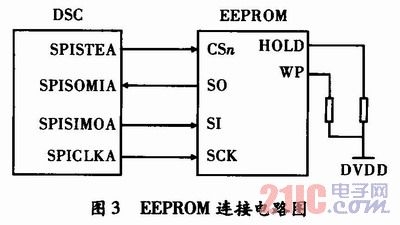

2.3.2 EEPROM擴展

考慮到系統在加電后,需要對一些設備的狀態進行一些初始化,而這些初始化的數據在設備運轉時又需要不斷改變。因此,在設備運轉過程中,實時將數據加以保存,以至于設備斷電后數據依舊存在。本系統利用TMS320F28335的SPI接口外擴了一個EEPROM保存設備運轉時實時獲取的初始化數據。本系統選用Atmel公司的AT25160集成芯片。該芯片的容量為2 kB,其寬度為8位數據寬度。模塊電路如圖3所示。

如圖3所示,DSC通過SPISTEA管腳發送片選信號選中EEPROM,通過SPICLKA管腳發送SPI傳輸時鐘,而數據的寫入和讀出則分別通過SPIS-IMOA和SPISOMIA管腳完成。EEPROM中的HOLD管腳用來暫停與主設備間串行數據傳輸,WP管腳則用來進行對EEPROM的寫保護,如果其為低電平,則主機無法向其寫人數據。系統對兩管腳輸入高電平,保證EEPROM在讀寫操作過程中一直可以進行而不被中斷。

2.3.3 SCI上位機通信接口

為了實現上位機同DSC異步的通信和數據傳輸,本系統利用TMS320F28335所提供的SCI接口來完成所需要求。SCI是一個2線的異步串行端口,即常說的UART。其數據的收發支持全雙工通信,內部收發均有一個16級的FIFO來緩存數據。為了保證數據可靠,SCI提供奇偶校驗,數據溢出檢測等操作。SCI接口輸出信號的電平是LV—TTL電氣標準,通過RS232收發轉換器加以驅動,獲得RS232電氣標準的信號,以便上位機接收。

2.4 模擬電路設計

模擬部分電路主要是以ADC為中心的應用電路。其主要實現模擬信號的處理,采集等工作。其中核心部分為AD轉換。

AD轉換部分,主要是通過數字采樣來完成模擬信號到數字信號的轉變。本系統選用的ADC芯片是美國模擬電氣公司的AD7656。模數轉換芯片AD7656是高集成度、6通道6 bit逐次逼近(SAR)型ADC,內含1個2.5 V基準電壓和基準緩沖器。該器件的功耗比最接近的同類雙極性ADC降低了60%。AD7656在每通道250kb·s-1采樣速率下的精度是同類產品的兩倍。可以由引腳和軟件選擇模擬電壓范圍:10 V或5 V;模擬電源電壓范圍為4.75~5.25 V,因而大范圍的工作電壓使其無需電平轉換等其他措施便可以直接與DSC相連;提供有并行和串行接口。可以工作在-40~85℃。標準模式5 V供電,250 kb·s-1時的功耗為140 mW,待機時僅為100μW。基于iCOMS技術制造的AD7656可以滿足工業領域對分辨率、多通道、轉換速率和功耗等方面的較高要求。

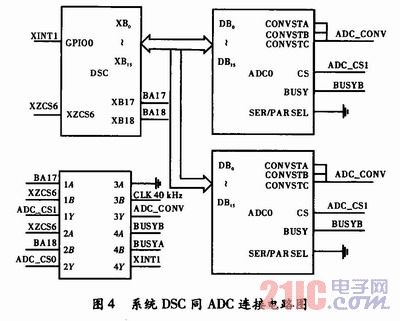

AD7656支持和DSC的并口、串口數據傳輸,通過SER/PAR SEL管腳的高低電平的選擇,來控制采樣后數字信號的傳輸方式。當其為高電平,則使用串行傳輸方式,反之則使用并行傳輸方式。本系統選用并行傳輸方式。在具體的轉換過程中,每片AD7656內部的6條采樣通路可以分為A、B、C共3組,其中每組通路包含2路通路。3組通路可以同時采樣,也可以單獨采樣,而每組內的兩條通路同時采樣。管腳CONVSTA,CONVSTB,CONVSTC分別用來對A、B、C采樣通路進行控制。當一個上升沿電平到達任一管腳,則該管腳對應模數轉換的2路通路被啟動,開始完成模數轉換。當把三管腳連接,3組采樣通路,即所有的6條采樣通路同時采樣。系統選用3組通路同時采樣。

當DSC連接有多片ADC時,則需要通過CS片選管腳來進行ADC的選擇。當采樣開始,BUSY管腳將從低電平變為高電平,在整個采樣的過程中,BUSY一直保持高電平,當采樣結束,BUSY則從高電平變為低電平,此時DSC就可以開始讀取數據。本系統則利用該管腳作為DSC外部中斷源的輸入管腳。當BUSY上電平由高變低,則通知DSC產生中斷,來進行數據的讀取。

本系統選用2片AD7656完成12路數據采樣,通過DSC的XINTF ZONE6把ADC設備映射到DSC上,進行數據傳輸。通過地址譯碼和邏輯控制實現2片ADC同DSC的連接。具體結構如圖4所示。

圖4中左下角為邏輯部分,通過DSC的地址線BA17和BA18完成對ADC的選擇。可以得到ADC0和ADC1在DSC中的地址映射為0x180000和0x1400 00。而外部輸入40 kHz的時鐘,作為ADC的采樣頻率。兩個ADC對應DSC的同一個中斷,當任意一片ADC采樣完畢,都會引起DSC的中斷,從而進行采樣數據的讀取。

3 系統軟件設計

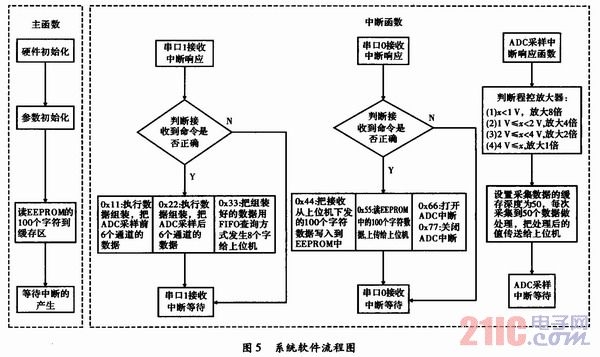

如前所述,整個信號處理板一共有12路模擬信號通路,通過傳感器接收到12路模擬信號。2片AD7656把12路模擬信號轉換為數字信號傳送給TMS320F28335,在TMS320F28335中對這些采集到的數據做相應處理后通過SCI傳送給上位機。同時對有必要保存的數據通過SPI接口保存到EEPROM中。整個采集、通信過程由上位機發送相關的命令來加以控制。程序的流程如圖5所示。

在主函數中,程序首先完成相應模塊的初始化,設定好CPU運行的時鐘,選定好各個模塊的工作模式,然后讀取EEPROM中的設備初始化數據,后進行入等待狀態。此時CPU等待ADC采樣的數據,當ADC采樣過程結束,則進入ADC中斷響應函數,在此函數中,主要完成數據的讀取,對于小信號,通過程控放大器放大其幅值,然后存儲到自定義的緩存區中。兩個串口工作方式均由上位機發送命令,從而觸發SCI的串口收中斷服務函數。然后在中斷服務函數中完成對應命令要求。系統選用串口1完成采集數據向上位機的傳輸,串口0完成向EEPROM發送需保存的數據和一些相關操作。而SCI0和SCI1分別對應DSC外設中斷的INT9.1和INT9.3,外部中斷XINT1對應INT1.4。程序設置兩個串口的傳輸速率均為38.4 kb·s-1。

在設備工作時,由于SCI1的中斷源是上位機的命令發送,系統規定上位機每20ms發送一個數據接受命令,因此SCI1的中斷響應周期為td= 20 ms。而由于采樣率為40 kHz,因此ADC的中斷服務函數響應周期為0.025 ms。系統規定采集一組數據的個數為50,那么采集一組數據的時間即為tc=1.25 ms,所以在一次SCI1中斷過程中,ADC會采集16組數據。考慮到串口傳輸的波特率為38.4kb·s-1,因此傳送一個16位的數據時間為tt=0.417 ms。而一組數據采集時間加上串口數據傳輸的時間為tc+tt=1.667 ms<

所設計的信號處理板以TMS320F28335為核心處理器,利用AD7656完成模擬信號采樣的功能硬件平臺。TMS320F28335片內集成了豐富的外圍資源,通過驅動軟件的配置和硬件系統的設計,可以方便、高效地完成大量數字信號的處理和運算。AD7656的6路模擬信號采集和16位高精度的模擬信號采樣,較好地完成了模擬信號的數字化轉換,減少了模擬信號采樣的失真。實驗證明,信號處理板所采集到的數字信號的誤差值約為1.37 mV,可達14位的采樣精度。