CCD是利用光電轉換原理把圖像信號轉換為電信號,即把一幅按空間域分布的光學圖像,轉換成為一串按時間域分布的視頻信號的半導體元器件。因其具有體積小、重量輕、功耗低、靈敏度高、工作穩定、壽命長、自掃描和便于同計算機接口等優點,被廣泛應用于圖像傳感和非接觸式測量。CCD應用的關鍵問題之一,是驅動時序發生器設計。它直接關系到CCD的信號處理能力、轉換效率和信噪比等光電轉換特征。針對Sony公司面陣CCD ICX098BQ的工作原理和驅動時序的要求,給出了驅動時序發生器的具體設計,使用VHDL語言對驅動時序發生器的實現方案進行了硬件描述,采用Quartus II 8.0對所設計的時序發生器進行了功能仿真,在該驅動時序發生器作用下,對Sony公司ICX98BQ面陣CCD產生的輸出信號波形進行了驗證。

1 CCD成像系統

CCD成像系統如圖1所示,目標通過光學系統成像在CCD上。在偏置電壓和驅動脈沖的作用下,CCD完成光電荷的轉移、存貯等工作,將光信號轉換成具有直流分量的模擬電信號。形成的模擬電信號經過信號處理器,進行除噪、增益和模數轉換后,將數據傳輸到顯示器或計算機上,進行后期處理。在上述系統中,CCD信號采集模塊是關鍵。對此,主要對CCD信號采集進行分析。

2 面陣CCD圖像傳感器驅動時序分析

2.1 Sony ICX098BQ型面陣CCD

ICX098BQ是Sony公司生產的一款1/4英寸(0.635cm),具有可變電子快門的行間轉移型彩色面陣CCD芯片,芯片結構如圖2所示。該芯片靈敏度高,暗電流小,具有較好的抗彌散功能。

ICX098BQ芯片由感光陣列、垂直移位寄存器、水平移位寄存器和輸出放大器4個主要部分組成。要使該CCD芯片正常工作,需要8路驅動時鐘來驅動。分別為4路垂直轉移時鐘Vφ1、Vφ2A、Vφ2B、Vφ3,控制垂直移位寄存器中的電荷信號向水平移位寄存器移動,其中當Vφ2A和Vφ2B為+15V高電平時作為讀出轉移時鐘,將感光陣列的信號電荷轉移到垂直移位寄存器中;兩路水平轉移時鐘Hφ1、Hφ2,控制水平移位寄存器中的電荷信號向前遷移;復位門時鐘RG,使水平移位寄存器中的電荷信號順利輸出,其頻率為10MHz,直接決定CCD電荷信號的水平輸出頻率并控制曝光量的電子快門時鐘φSUB。

上述驅動信號均由CCD驅動時序發生器產生。由于面陣CCD的驅動信號數量多,相位要求嚴格,且需要多種電壓的驅動,因此進行時序分析并設計出高精度的驅動時序電路是問題的關鍵。

2.2 驅動時序分析

ICX098BQ芯片的一個工作周期分為4個階段:感光階段、垂直轉移階段、幀轉移階段和水平讀出階段。感光階段進行光電轉換,完成感光陣列的電荷積累。垂直轉移階段實現感光陣列積累的電荷包讀出轉移到相鄰的垂直移位寄存器。幀轉移和水平讀出階段包括電荷包從垂直移位寄存器向水平移位寄存器并行轉移以及從水平移位寄存器向輸出放大器的串行輸出。

在CCD工作周期中,首先在Vφ1、Vφ2A、Vφ2B、Vφ3的控制下,感光陣列的垂直移位寄存器進行一次電荷轉移,將之前殘留下來的電荷徹底清除,為下一步做好準備。然后垂直驅動時鐘V1將持續一段高電平。此刻,讀出時鐘V2A、V2B跳變為+15V的高電平窄脈沖,讀出時鐘迅速將感光陣列中的所有像素電荷并行地轉移到相鄰的垂直移位寄存器中。在每個行消隱期間,垂直移位寄存器中的電荷在四相垂直驅動時鐘Vφ1、Vφ2A、Vφ2B、Vφ3交替作用下逐行地向水平寄存器轉移。此時水平驅動時鐘Hφ、Hφ2保持不變。在行正程期間,轉移到水平寄存器的一行信號電荷受頻率為10MHz的兩相水平驅動時鐘Hφ1、Hφ2控制,向浮置擴散放大器水平轉移。輸出放大器以復位門時鐘RG的頻率將像素電荷逐一轉換成信號電壓后串行輸出,在輸出端得到與光學圖像對應的一行的視頻信號。

3 基于VHDL的時序發生器設計

由于面陣CCD驅動時序的復雜性,選用硬件描述語言VHDL設計CCD時序。VHDL采用自頂向下的設計方式,具有較強的硬件描述能力和仿真能力。在程序中,定義的輸入輸出端包括兩個輸入端和10個輸出端。

整個驅動時序發生器的實現程序為兩重嵌套的循環,整個過程采用3段式狀態機來完成。一個CCD工作周期流程如下:

(1)對水平寄存器進行清空復位。

(2)垂直轉移,將電荷從感光區轉移到相鄰的垂直移位寄存器。

(3)進行幀轉移和水平讀出階段。幀轉移一行,水平讀出一行,直到整幀讀出完畢。

(4)返回,讀取下一幀。即返回步驟(1)。

狀態轉移圖如圖3所示。

IDLE:為空閑狀態;當積分啟動后,轉到狀態1。

狀態1:為預讀出狀態;讀出水平寄存器內的電荷,當水平讀出700個電荷后,轉向狀態2,否則,自循環。

狀態2:為垂直轉移狀態;使感光區的電荷轉移到垂直移位寄存器,垂直轉移后,轉到狀態3。

狀態3:幀轉移狀態;其中Flag為場有效標志,當Flag=1時,進入積分狀態,開始下一幀的工作。

狀態4:水平讀出狀態。

狀態5:積分狀態,轉向空閑狀態,開始下一幀的工作。

根據分析,設計出產生上述時序的頂層原理圖,如圖4所示。

在CCD時序發生器模塊中,輸入為時鐘和復位信號,以及兩路同步信號VD和HD;輸出除了CCD驅動所需的10路信號外,還包括SHP和SHD兩路用于相關雙采樣的電路以及暗像元、啞像元驅動時序。

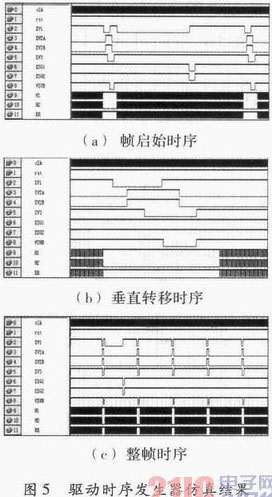

在對VHDL語言描述的時序發生器進行編譯后,對驅動時序發生器進行功能仿真,仿真結果如圖5所示。

通過對FPGA芯片程序的下載。將功能模塊集成于CycloneII系列芯片EP2C8T144C8N中。該時序發生器頂層模塊程序資源占用率僅為3%。

4 硬件實現以及測試結果

CCD信號采集驅動電路硬件部分主要分為兩個部分,即CCD驅動電路和偏置電壓的設計。

4.1 偏置電壓電路

對ICX098BQ的數據手冊進行分析,Hφ1、Hφ2水平移位驅動工作電壓峰峰值為3.3V,分別為-3.3~0V和0~3.3V,Vφ1、Vφ3垂直轉移工作電壓為5.5 V(-5.5~0 V),Vφ2A、Vφ2B為三電平,工作電壓為(-5.5V、0V、+15V)。因而需要-5.5V和+15V作為CCD垂直驅動時序的工作電壓。偏置電壓+15V和-5.5V采用Linear公司生產的LDOLT3487獲得,偏置電壓產生電路如圖6所示。

LT3487是一款單芯片穩壓器,可以在單輸入電壓(2.3~16 V)基礎上,獲得正負電壓。與其他同類型穩壓器相比,其輸出斷開功能可避免在器件關閉期間出現直流漏電所導致的功率損耗。文中輸入電壓值為+5V,通過USB接口從電腦得到,其供電能力完全能夠滿足驅動及CCD電路的電流消耗。

4.2 驅動器電路

如圖7所示,CCD工作所需的驅動時序均由CycloneII系列器件EP2C8T144C8N產生。在CCD工作所需的4路垂直驅動時鐘Vφ1、Vφ3、Vφ2A、Vφ2B中,Vφ1、Vφ3為兩電平,Vφ2A、Vφ2B為三電平。而FPGA產生的信號只有‘0’和‘1’兩種狀態。對此,可將時序發生器中的XV2和XV3時序分別與XSG1和XSG2時序利用脈沖合成驅動器CXD1267AN進行合成來生成Vφ2A、Vφ2B。

如圖7所示,在FPGA產生的時序發生器的10路信號中,XV1、XV2、XSG1、XV3、XSG2、XV4經過脈沖合成驅動器CXD1267AN后,合成為Vφ1、Vφ2A、Vφ2B、Vφ3;而H1、H2和復位脈沖RR通過ACT04反相器后進入CCD進行工作,提升了H1、H2和RG的驅動電壓,增加了CCD的水平讀出能力。驅動電路在-5.5V和+15V的電壓下工作。在電壓偏置電路和驅動電路的工作下,產生的CCD信號為包含直流分量大小為幾百mV的交流信號。

4.3 硬件測試結果

物體的圖像經過光學鏡頭投射到面陣CCD上,并將上文實現的驅動時序用于面陣CCD的驅動,并用示波器對隔直后的CCD信號進行測量。

圖8為CCD輸出的某一行中各感光像元電荷信號的波形,每個周期代表一個像元。每個像素單元分為3部分,它們分別是復位脈沖饋入、參考電平和數據電平。每個周期中的尖峰為復位脈沖饋入到CCD的讀出電容,在CCD輸出波形中形成,每個像素感受到光信號的有效值由參考電平和數據電平的差表示。由此可見,在驅動時序作用下面陣CCD能正常工作。

5 結束語

時序控制方案采用VHDL語言進行設計,用EDA軟件對所設計的驅動電路進行了仿真。仿真結果表明,該驅動電路能夠滿足面陣CCD驅動時序的求。