引言

隨機數發生器是信息安全領域不可或缺的重要組成部分,廣泛應用于金融、軍事等信息安全保密通信的電子設備中。目前,隨著對RNG體積、功耗、接口方式等要求的提高,設計集成化芯片或IP核形式的隨機數發生器成為一種必然。為此,基于純數字電路實現的隨機數發生器已成為研究的熱點,而FPGA可編程邏輯芯片為此類隨機數發生器的研究提供了良好的開發環境。

為方便隨機數發生器IP核的下載、運行及測試,同時保證產生的隨機數能夠快速地傳送給主機進行隨機性檢測,本文以FPGA芯片為核心,以USB接口為通信接口,設計實現了一個隨機數發生器的驗證平臺。該平臺結構簡單,功能完善,對于其他特殊應用的驗證平臺搭建也具有指導意義。

1 系統硬件結構及工作原理

隨機數發生器驗證平臺主要由CycloneII FPGA芯片EP2C20Q240C8N、與主機進行通信的USB收發器電路、下載配置芯片EPCS4、頻率為48 MHz的時鐘源芯片、外部存儲器(Flash)、兩個電壓轉換電路、復位電路和其他電路組成,如圖1所示。

在每次實驗演示時,將該芯片通過USB口與PC機相連,由主機為平臺提供5 V電源,當與主機連通后系統上電,復位電路進行工作,對整個系統進行復位。以QuartusII 7.2為開發環境,采用ByterBlsterII下載電纜,通過JTAG下載口或以AS下載方式,通過配置芯片EPCS4將隨機數發生器系統下載到實驗平臺中,最終通過USB口連接主機與平臺進行信息交互。由主機向系統發送命令,在系統控制下,產生的隨機數通過USB收發器傳送給主機,主機接收數據后進行隨機性的各項檢測。

2 核心器件和關鍵技術

2.1 FPGA芯片EP2C20Q240C8N

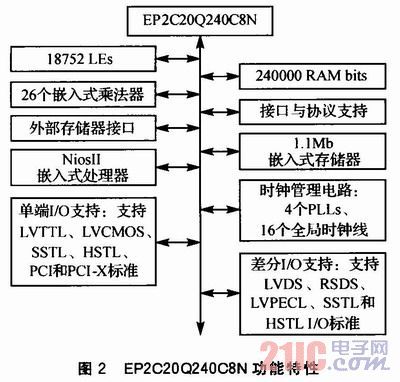

EP2C20Q240C8N芯片是A1tera CyeloneII系列產品中的一員,它采用TSMC1.2 V、90 nm和低電介絕緣工藝技術,由12英寸(300 mm)晶圓制成,具有潛在速度方面的極大優勢。

該芯片提供了許多功能特性,如圖2所示。該芯片資源豐富,可為隨機數生成系統提供良好的實驗環境。隨機數生成系統主要由OC8051IP核、隨機數發生器IP核及USB控制器組成,實現了USB接口與隨機數生成系統的連接,保證了主機與平臺的信息交互。

2.2 PDIUSBP11A收發器芯片

PDIUSBP11A USB收發器是Philips公司推出的,設計用來與USB物理層進行交互,來自串行接口引擎(SIE)的VPO和VMO作為主驅動器的輸出。串行接口引擎和USB收發器的共同作用允許USB專用集成電路設計者設計靈活的USB設備,與更多可用邏輯元件相兼容。其主要特性包括:

①符合USB1.1協議規范;

②利用數字信號的輸入與輸出來傳送和接收USB串行數據;

③支持全速(12 Mb/s)和低速(1.5 Mb/s)的串行數據傳輸;

④支持單端口數據界面;

⑤單一的3.3 V電源;

⑥允許USB專用集成電路與USB的物理層進行交互;

⑦有SO-114、SSOP-14和TSSOP-14封裝。

3 設計方案實現

3.1 系統供電電路

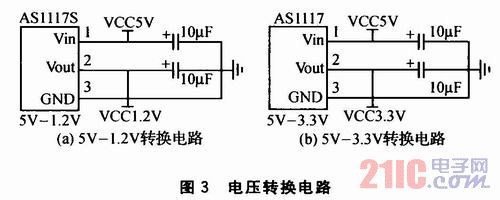

本系統沒有設置專門的電源電路,而是通過USB接口由主機提供5 V電源。由于系統內部工作電壓為3.3 V和1.2 V,為此,專門設計了兩個電壓轉換電路,將USB接口的5 V電壓轉換成3.3 V和1.2 V后再提供給系統,保證系統正常工作。電壓轉換電路采用封裝為SOT-223的AS1117和AS1117S芯片,主要電路原理圖如圖3所示。

為保證輸出電壓的穩定性,在電壓輸入端和輸出端都接有10μF的輸出電容。

3.2 USB收發器電路

PDIUSBP11A芯片擁有14個可用引腳,其電路原理圖如圖4所示。

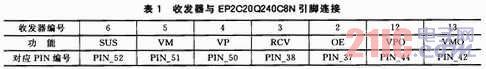

在本設計電路中,將PDIUSBP11A芯片的引腳1和引腳8懸空;引腳7和引腳14分別接地和3.3 V電壓;差分數據信號D+和D-引腳分別經一個阻值為24 Ω的電阻與USB接口的D+和D-相連,同時D+經上拉電阻與3.3 V電壓相連;引腳9經上拉電阻與3.3 V電壓相連,使USB保持在全速工作模式下;其他引腳與FPGA芯片相應的引腳相連接,具體連接方式如表1所列。

3.3 配置芯片及下載電路

Altera編程硬件主要包括MasterBlaster、ByteBlasterMV、ByterBlsterII、USB-Blaster和Ethernet Blaster下載電纜或Altera編程單元(APU)。

本文采用ByterBlsterII下載電纜,選用EPCS4配置芯片,設計實現了AS主動串行配置模式與JTAG下載模式相混合的下載配置電路。

本設計采用AS和JTAG兩種下載方式,可以通過JTAG方式對程序進行調試,同時通過QuartuslI軟件提供的一個可在線操作FPGA片上RAM內容的工具InSystem Memory Content Editor,用戶可以查看和修改RAM的內容。用戶可以預期對RAM中的內容進行修改,并通過該工具查看修改后的結果,兩者進行對比就可驗證程序運行是否正確。此外,在JTAG模式下可以利用jic文件驗證配置芯片是否已經損壞。

3.4 復位電路

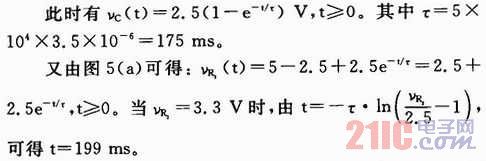

為使驗證系統初始化正確,當整個系統在電源上電時,必須處于復位狀態。一般應保持復位脈沖為高保持兩個機器周期以上,而系統晶體振蕩器達到穩定一般需要150 ms左右。為此,本文設計了基于RC器件的復位電路,如圖5所示。

其中,R1=R2=100 kΩ,C1=3.5μF,對于虛線中的電路,運用戴維南定理把系統上電后電路中除電容支路以外的部分進行化簡,得到的電路如圖5(b)所示。

由此可得,該復位電路能夠正常復位,保證系統正常工作。

3.5 時鐘電路

時鐘由晶振芯片提供,晶振芯片有無源晶振和有源晶振兩種。無源晶振為無極性元件,共有2個引腳,只有在時鐘電路工作控制下才能產生振蕩信號;有源晶振由石英晶體組成,此外還有晶體管和阻容元件,信號穩定,它共有4個引腳,常用的連接方式為:1腳懸空,2腳接地,3腳輸出,4腳接電壓。本設計采用ELV型號為SMD5*7的48MHz晶振。

3.6 存儲器模塊

為滿足特殊功能需求,擴展了1 Mb的Flash。Flash選用Spansion公司的CMOS多功能器件,型號為AM29LV010B,采用32引腳的標準TSOP封裝,工作電壓為3 V,8位數據寬度。數據總線使用D0~D7,地址總線使用A0~A16,其他還有芯片使能信號CE,輸出使能信號0E和寫使能信號WE。它與FPGA芯片引腳的具體連接方式如表2所列。

3.7 其他電路

為保證系統中各個芯片能夠正常工作,本設計在各電壓源都并聯有0.1μF的退耦電容,并將這些電容擺放在芯片的周圍,濾除高頻雜波。

4 測試與驗證

各模塊電路設計完成后,經Altium Designer09仿真驗證,完成了相應的PCB版圖設計,并最終進行電路版圖的印刷和元器件焊接,實現了整個驗證平臺。

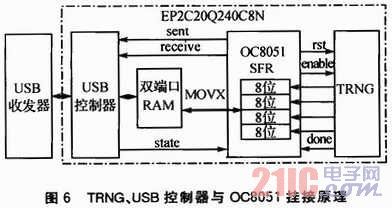

為檢驗平臺工作的正確性,本文對參考文獻中的隨機數發生器利用VHDL語言進行了實現,并在輸出模塊中增加了一個32位的移位寄存器,每產生32位隨機數進行一次輸出。最后,將該隨機數發生器及參考文獻中所設計的USB控制器與參考文獻中所提供的OC8051 IP核進行掛載連接,其掛接原理圖如圖6所示。

掛接完成后,利用QuartusII軟件,將整個系統以AS下載方式,通過配置芯片EPCS4下載到FPGA板中。由OC8051 IP核控制隨機數發生器模塊進行工作,每產生32位隨機數時,TRNG向OC8051發送一個done信號,OC8051接收32位數據,并將其分為4個8位存于4個特殊功能寄存器(Sp-ecial Function Register,SFR)中,并通過指令MOVX借助累加器將32位數據轉移至雙端口RAM中。之后進行下一32位隨機數的產生及傳送,直到運行16次后,RAM中所存儲的隨機數為512位時,OC8051置sent信號有效,USB控制器將512位隨機數封裝成數據包,通過USB收發器傳送給主機,傳送完成后向OC8051返回一個state信號,表明傳送結束。重復上述過程即可源源不斷地將產生的隨機數傳送給主機,由主機最終完成隨機數檢測,檢測結果表明所接收到的數據滿足隨機數特性。

在隨機數生成系統下載、隨機數生成及隨機數傳送過程中,整個平臺工作正常,表明各模塊電路原理及連接的正確性:

①電壓轉換電路連接正確,能為系統提供穩定電壓,同時表明,退耦電容起到了很好的去噪作用;

②下載電路連接正確,能夠將程序正確下載到FPGA中;

③復位電路工作正常,時鐘電路能給系統提供穩定的時鐘;

④USB收發器電路連接正確,能正常收發數據。

由此表明,該驗證平臺具有一定的可靠性和穩定性,能為隨機數發生器提供一個良好的驗證環境。

結語

本文結合實際需求,在充分理解FPGA結構原理和元件特性的基礎上,設計實現了一個小型的FPGA開發板。它不僅可以作為隨機數發生器的驗證平臺,同時也可為其他基于數字電路實現的系統提供服務。本文所設計的開發板結構比較簡單,故難以滿足大型數字電路開發系統的要求,為此,下一步的工作是擴展功能模塊,設計更多的外圍擴展電路,滿足更高的實驗需求。