本系統以AD7892SQ和CPLD(復雜可編程邏輯器件)為核心設計了一個多路信號采集電路,包括模擬多路復用、集成放大、A/D轉換,CPLD控制等。采用硬件描述語言Verilog HDL編程,通過采用CPLD使數據采集的實時性得到提高。

1 硬件設計

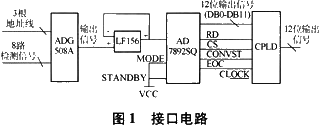

針對多路信號的采集,本系統采用4/8通道ADG508A模擬多路復用器對檢測的信號進行選擇,CMOS高速放大器LF156對選中的信號進行放大,AD7892SQ實現信號的A/D轉換,CPLD完成控制功能。電路如圖1所示。

AD7892SQ是美國AD公司生產的LC2MOS型單電源12位A/D轉換器,可并行或串行輸出。

AD7892SQ A/D轉換器具有如下特點:單電源工作(+5V或+10V);內部含有采樣保持放大器;具有高速的串行和并行接口。

AD7892SQ控制字的功能如下:

a)MODE:輸入控制字,低電平時為串行輸出,高電平時為并行輸出,本系統為并行輸出;

b)STANDBY:輸入控制字,低電平時為睡眠狀態(功耗5mW),高電平時正常工作,一般應用時接高電平;

c)CONVST:啟動轉換輸入端,當此腳由低變高時,使采樣保持器保持開始轉換,應加一個大于25ns的負脈沖來啟動轉換;

d)EOC:轉換結束信號,轉換結束時,此腳輸出100ns的低電平脈沖;

e)CS:片選,低電平有效;

f)RD:低電平有效,與CS配合讀,使數據輸出。

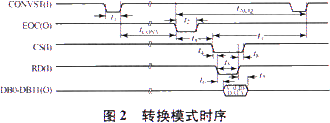

MODE腳接高電平時,AD7892SQ為并行輸出,時序如圖2所示。

在EOC下降沿時間內開始采樣,就是轉換一結束就開始下次采樣,采樣時間fACQ應大于等于200ns或400ns,轉換結束后(即E0C的下降沿),當CS和RD有效時,經過t6=40ns的時間,就可以在DB0-DB11上獲得轉換之后的12位數據,CS和一般的片選信號相同,可以一直有效,外加RD的時間T5也應大于35ns。CONVST信號t1應大于35ns,在上升沿時采樣保持器處于保持狀態,開始A/D轉換,轉換所需的時間tCONV為1.47μs或1.6μs,轉換結束后,EOC腳輸出的t2為大于等于60ns的負脈沖用來進行中斷或數據鎖存。由此得出下次采樣和本次的輸出可以同時進行,因此最小的一次采樣轉換輸出的時間為1.47+0.2=1.67μs(600kSPS(千次采樣每秒)),最大1.6+0.4=2μs(即500kSPS),圖2中的t9大于等于200ns,t7近似為5ns,t3、t4、t8可為0,(此時t9=tACQ)。

2 程序設計

2.1 系統介紹

系統中的CPLD是結構比較復雜的可編程邏輯器件,硬件描述語言設計的控制程序寫入CPLD內即可實現其功能。系統采集的數據常常放在數據緩存器中,數據緩存區要求既要有與A/D轉換芯片的接口,又要有與系統DSP的接口,以提高數據吞吐率,本系統選用FIF0(先進先出),并且FIF0具有不需要地址尋址的優點。

2.2 系統的軟件描述

本系統采用Verilog HDL語言進行描述。VerilogHDL被近90%的半導體公司使用,成為一種強大的設計工具。其優點是:

a)Verilog HDL是一種通用的硬件描述語言,易學易用;

b)Verilog HDL允許在同一個電路模型內進行不同抽象層次的描述,設計者可以從開關、門、RTL或者行為等各個層次對電路模型進行定義;

c)絕大多數流行的綜合工具都支持VerilogHDL,這是Verilog HDL成為設計者的首選語言的重要原因之一;

d)所有的制造廠商都提供用于Verilog HDL綜合之后的邏輯仿真的元件庫,因此使用Verilog HDL進行設計,即可在更廣泛的范圍內選擇委托制造的廠商;

e)PLI(編程語言接口)是Verilog HDL語言最重要的特性之一,它使得設計者可以通過自己編寫C代碼來訪問Verilog HDL內部的數據結構。

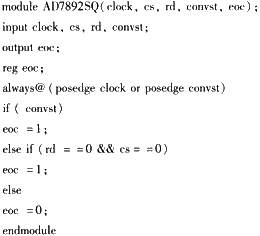

2.3 AD7892SQ描述

描述AD7892SQ模塊,可以把模塊用于采集系統的仿真,以驗證FSM(有限狀態機)設計的正確性。該模塊主要有4個輸入信號和1個輸出信號,與芯片的控制信號一致。程序如下:

AD7892SQ仿真波形見圖3。

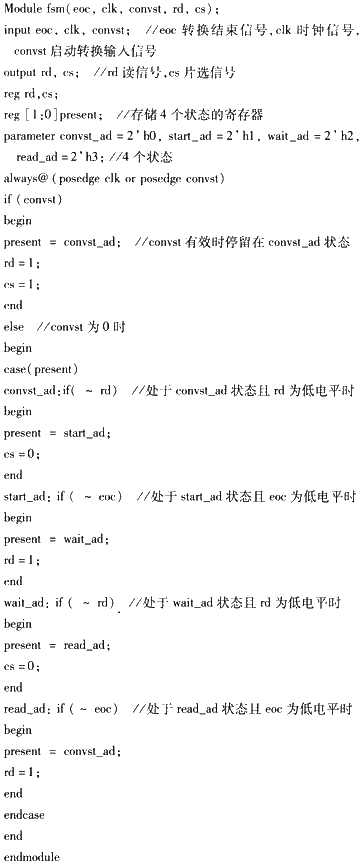

2.4 FSM描述

FSM為異步工作。當convst有效時停留在convst_ad狀態,且rd和cs都為1,convst為0且處于clock的上升沿時FSM會處于4個狀態中的一個狀態。圖4為FSM仿真波形。

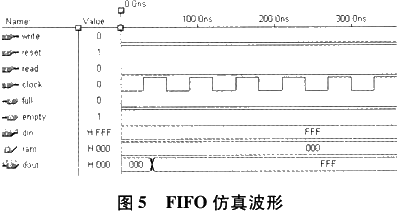

2.5 FIFO描述

FIFO為同步工作。當reset有效且處于clock的上升沿時,dout為O;reset為1且處于clock上升沿時,read和write組合的4種情況分別對應各自的工作狀態。圖5為FIFO仿真波形。

3 結束語

Verilog HDL硬件描述語言已越來越廣泛地應用于EDA(電子設計自動化)領域,多數EDA設計工程師都用它進行ASIC(專用集成電路)設計和CPLD/FPCA開發。用高級語言進行電路設計,能夠靈活地修改參數,而且極大地提高了電路設計的通用性和可移植性。最后需要指出的是,采用IP核的方法設計電路,不但可以單獨使用,而且可以嵌入到ASIC或CPLD/FPGA的電路設計中,同時縮短了產品的開發周期,應大力推廣。

作者:秦曉芳 朱堅民 郭冰菁 來源:電子工程師