引言

與過去幾代(DDR和DDR2)器件相比,DDR3存儲器器件有了明顯的進步。DDR3存儲器系統可以大大提升各種數據處理應用的性能。為了充分利用和發揮DDR3存儲器的優點,使用一個高效且易于使用的DDR3存儲器接口控制器是非常重要的。視屏處理應用就是一個很好的示例,說明了DDR3存儲器系統的主要需求以及在類似數據流處理系統中DDR3接口所需的特性。希望能給大家有個客觀的認知。

視頻處理系統將對于數據帶寬的要求推高到了極致:系統可以處理越多的數據,就具有越高的性價比。視頻聚合器和路由器可并行處理多個視頻流,因此對于匹配數據處理能力和視頻帶寬的需求就成為了設計的一大挑戰。FPGA可通過在單個FPGA中實現多個視頻處理器來提供強大的處理能力。那么現在的挑戰就變成了要使數據盡快且高效地從FPGA進出。DDR3存儲器系統在大多數情況下可以為這些基于FPGA的系統提供足夠的帶寬。

視頻處理設計說明

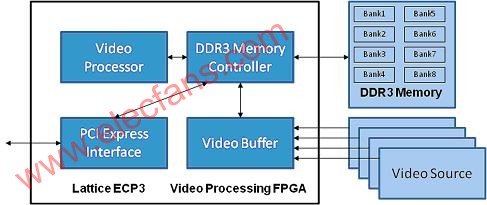

我們的目標視頻處理設計將同時處理四個視頻源,將視頻數據轉換和壓縮為一種可以通過PCI Express接口傳輸到存儲器hub的格式。系統的主要功能塊如圖1所示。

圖1:視頻處理器框圖

FPGA獲取并緩存四個視頻源的數據流。這些FIFO緩沖器由DDR3存儲器控制器清空并保存在DDR3存儲器中。一旦一個完整的視頻數據包存儲完畢,視頻處理器會向DDR3存儲器控制器申請數據,存儲器控制器讀取數據并將其傳到視頻處理器。視頻處理器對視頻數據進行格式化和壓縮,并通過DDR3存儲器控制器寫回存儲器。當一個視頻數據包全部處理完畢,并準備通過PCI Express接口進行傳輸,DDR3存儲器控制器從視頻處理器獲取數據并將其傳到PCI Express接口。

DDR3存儲器接口控制器概述

雙倍數據速率(DDR3)同步動態隨機存取存儲器(SDRAM)控制器是一種通用存儲器控制器,能與行業標準的DDR3 SDRAM器件和具有JESD79 - 3C型規范兼容的模塊接口。并對用戶應用提供了一個通用命令接口。DDR3 SDRAM是新一代SDRAM存儲器技術,具有更快的速度,緩沖SSO,由于直接將信號連到SDRAM,取代了低偏移的樹狀分布的方法,因此減少了布線。這個IP核減少了需要整合DDR3存儲器控制器與應用的其余部分所需投入的工作量。

特點

支持所有LatticeECP3“EA”器件

能與工業標準的DDR3 SDRAM器件和具有JESD79 - 3C規范兼容的模塊接口

高性能DDR3,高達400 MHz/800 Mbps的操作

支持存儲器數據路徑寬度為8 - ,16 - ,32和64位

支持x8和x16器件配置

支持無緩沖的DDR3 DIMM

支持一個DIMM和每個DIMM的一個級

8(固定)、“chopped 4”,或8(傳輸),或“chopped 4”(固定)的可編程突發長度

可編程的CAS延遲

可編程寫延遲

四位順序或交織的讀突發類型

支持自動的DDR3 SDRAM的初始化和刷新

對每個DQS自動寫

支持掉電模式

支持動態片上終端(ODT)的控制

終端數據選通(TDQS),僅適用x8寬度

ECP3 IO原語管理讀偏移(讀電平相等)

自動可編程間隔刷新,或用戶啟動刷新

DDR3的SDRAM控制器可作為IPexpress用戶可配置的IP核,能夠進行IP的配置,生成網表和模擬文件用于設計。請注意,除非購買了這個IP 的許可證,否則生成的位流可能會被阻止,或比特流可能有時間邏輯。

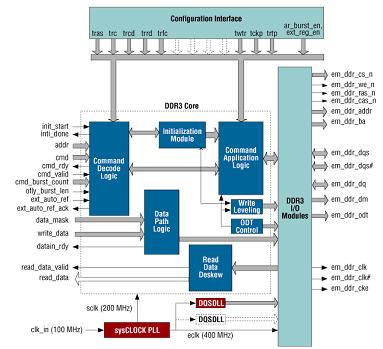

圖2:DDR3存儲器控制器IP核框圖

DDR3存儲器控制器應支持廣泛的存儲器速率和配置,以滿足各種應用需求。例如,Lattice ECP3 DDR3存儲器控制器支持高達800Mb/s的DDR3器件速率,8至64位的存儲器數據通道(帶有x8或x16 DDR3器件),并且同時支持雙列直插式存儲器塊(Dual Inline Memory Modules,DIMM)和單個存儲器的器件。

DDR3存儲器控制器必須為各種存儲器訪問實現不同的時序要求。一些要求對于我們的目標應用來說非常重要,包括以下幾個方面:

DDR3存儲器使用"類似cache"的bank進行組織,每個器件帶有8個bank.訪問最近工作(打開)的bank比訪問未工作的(關閉)的bank速度快。

可使用4位、8位或交叉存取方式進行突發(burST)模式讀訪問。

根據存儲器速率和用戶設置,CAS和寫延遲都是可變的。從讀請求轉換為寫請求需要額外的延遲時間,因為雙向的數據總線必須改變傳輸方向。

針對視頻處理的IP核實現

為了使存儲器數據帶寬和效率最大化,針對視頻處理設計的IP核實現需根據DDR3存儲器特性使用相匹配的算法。下面列出了一些重要的實現考慮。

使用突發(Burst)模式的數據訪問

DDR3存儲器可通過突發模式訪問,突發模式在數據以數據塊形式存放(如視頻處理應用)的應用中是非常有效的。同樣,通過將視頻數據以優化的方式放入8個bank中,數據傳輸帶寬和之后的數據處理率可維持在一個高速的水平。在我們的示例中有4個視頻源,因此如果我們為每個視頻源使用2個bank(一個用作存儲緩沖器,另一個用作處理緩沖器),這將使DDR3保持高傳輸效率。高效的DDR3存儲器控制器應當基于每個bank的狀態,使用最快的訪問時間處理突發讀和寫。此外,視頻處理器將事務分組,使總線換向時間最小化并進一步提高存儲器帶寬。 更高帶寬的數據緩沖分配

來自視頻源1的數據可通過FIFO讀取并存儲到DDR3存儲器中的Bank 1.這將是一個只寫操作,可以使用突發模式來保持傳輸的高效。一旦一個數據包保存到Bank 1,視頻處理器可從Bank 1讀出數據,對其進行操作并存入Bank 2.這些操作都可使用突發模式,因此總線換向的花銷僅占用存儲器帶寬的很小的百分比。一旦Bank 2中的數據經過處理后可被讀出,還是使用突發模式,然后發送到PCI Express接口,再傳輸到hub.盡可能地保持存儲器bank為打開狀態可使得控制器使用最短的存儲器訪問時間,從而提高了效率。

使用交叉存取的并行數據處理

數據讀可在bank之間切換或交叉存取,而無需大量延遲或總線換向時間。因此,只要處理硬件能夠支持,多個視頻流可通過視頻處理器同時處理。當處理好的數據寫回DDR3存儲器時,多個寫操作也可以通過交叉存取來提高帶寬。一個易于使用和可預測的存儲器控制器,如:ECP3 DDR3存儲器控制器,在用戶基于其對數據處理的基本算法的了解的情況下來分配存儲器緩沖區時,可以最小的硬件和軟件開銷來實現最大的帶寬。

刷新和初始化

因為DDR3存儲器中的數據必須定期進行刷新,一些存儲器訪問必須分配給刷新操作。DDR3控制器應支持自動刷新指令隊列,它可能是深度為8的指令集,可以作為一個指令組來執行,以使效率最大化。DDR3器件的初始化過程是非常繁復的并且很容易出錯,特別是在手動執行時。DDR3控制器的初始化模塊應該通過與用戶邏輯的一次簡單的握手,自動初始化存儲器,從而極大地簡化了接口設計。

流水線的指令處理

存儲器控制器應當使用指令流水線來提高吞吐率,在當前指令出現在存儲器接口時,譯碼隊列中的下一條指令。這種方法提供了高于雙周期存儲器控制器100%的吞吐量。

功耗管理

在一些DDR3應用中,功耗管理可能是一個需要考慮問題。在一些設計中,使用Power Down指令是非常有用的。該指令在沒有數據訪問需求的時候,降低功耗。在power down狀態下,器件功耗的降低可達90%.萊迪思DDR3存儲器控制器支持該指令。此外,萊迪思ECP3為帶有SERDES和高速接口,如DDR3存儲器控制器的應用提供最低功耗的可編程解決方案。

設計和驗證流程

DDR3存儲器控制器IP核必須易于配置、生成并應用到一個目標設計中。使用圖形化用戶界面(GUI)來配置各種DDR3控制器參數是一種簡便的方法,為目標系統快速創建正確的控制器。所有的參數都需要確定,如:存儲器寬度、深度、速度和延遲。每一類配置參數都有其獨立的選項卡,有助于將設計任務分為一個個可管理的"任務塊".一旦參數選定,生成代碼(用VHDL或Verilog)和生成相應的測試基準應當是比較容易的。

例如,萊迪思IPexpress工具只需三個步驟,如圖3所示,在ispLEVER設計軟件中創建ECP3 DDR3存儲器控制器IP核:

1)從萊迪思網站下載IPexpress工具并將IP核導入。

2)IP核參數可通過每個配置組對應的選項卡進行選擇,配置組有:類型、設置、時序、引腳和設計工具。

3)基于Verilog或VHDL的IP核和測試基準一起生成,包括頂層、監視器、指令生成器、用于Aldec或ModelSim的配置和腳本文件。

圖3:下載、配置和生成IP核設計流程

小結

我們對很多數據處理應用的設計中,如本文中視頻處理的例子,當存儲器具有足夠的帶寬時,可以充分利用FPGA的并行處理能力的優勢。DDR3存儲器具有靈活、易于使用的存儲器控制器。此外,一個經驗證的IP核與可靠的設計和驗證環境也加速了這些應用的上市。