摘 要:介紹了數字衛星調諧芯片ZL10036的內部結構及工作原理,研究了其應用的主要問題,實現了其在射頻至基帶轉換器中的應用。

關鍵詞:ZL10036? 下變頻 I2C總線? 電荷泵" title="電荷泵">電荷泵鎖相環? 射頻至基帶轉換

?

?

??? 隨著數字衛星和無線通信技術的迅猛發展,面向專用系統的射頻集成芯片的種類越來越多,集成度也越來越高。從某種程度上說,一個完整的無線通信系統射頻模塊的構建過程,已經變成對不同芯片的選擇與使用的過程。因此,射頻系統性能的優劣很大程度上取決于所選核心集成芯片的性能。ZL10036是卓聯(ZARLINK)半導體公司生產的一款用在數字衛星信號接收機中的進行直接下變頻的射頻芯片。在本文所述的應用中,該芯片被用來作為一臺射頻至基帶轉換器的核心部件。本文在介紹這款芯片特點的同時,將圍繞它在射頻至基帶轉換器中的具體應用做詳細研究。

1 芯片ZL10036

??? ZARLINK半導體公司的數字衛星調諧芯片ZL10036是一個單片寬帶直接變頻調諧器,它提供高度集成的衛星調諧器功能。內部集成有I2C串行總線接口控制器,低相位噪聲PLL頻率合成器" title="頻率合成器">頻率合成器,正交相位分離調諧器,全集成的本地振蕩器和可調帶寬的基帶低通濾波器。包括PLL頻率合成器,芯片增益和基帶帶寬在內的所有芯片功能都通過I2C串行總線接口實現控制。此外,ZL10036對相鄰信道有良好的隔離度,提供了一個可供選擇的射頻旁路,總線接口可與3.3V的邏輯電平兼容,具有降功耗模式等特點。

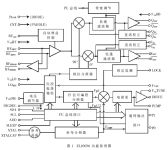

??? ZL10036功能原理框圖如圖1所示,可以分為RF信號處理部分(圖1上半部分)和PLL頻率合成器(圖1下半部分),此外還有芯片的邏輯控制寄存器部分(圖1中未畫出,見圖3)。

?

1.1 RF信號處理部分

??? RF信號處理部分主要由前置增益可調放大器、兩個線性度高的混頻器、兩個帶寬可調的基帶濾波器、自動增益調控模塊(AGC SENDER)、直流偏移校正(DC CORRECTION)模塊組成。

??? 射頻信號經過良好的阻抗匹配由差分輸入端口RFINPUT和/RFINPUT進入芯片,輸入至前置放大器級,然后分為兩個通道,分別與正交的兩路本振" title="本振">本振信號混頻,下變頻至基頻,然后分別通過帶寬可調(4~40MHz)的基帶低通濾波器,再經差分放大器放大后分別輸出QOUT,/QOUT和IOUT,/IOUT兩路正交的差分基頻信號。

??? 整個通路的增益控制設計非常有特點,可分為模擬RF AGC、RF數字控制增益、基帶前置濾波器和基帶后置濾波器四個部分(圖1只表示出第一部分),增益的控制非常靈活和方便。其中模擬RF AGC增益是連續變化的(0~72dB),由AGC SENDER實現控制;RF數字控制增益是一個0dB、4dB二選一的增益開關,由芯片內部邏輯位RFG的高低來實現控制;基帶前置濾波器和后置濾波器的增益均為0~12.6dB,步長為4.2dB,分別由芯片內部邏輯位BA1、BA0和BG1、BG0來實現增益選擇控制。

??? 基帶濾波器的帶寬可以根據用戶的需要在4~40MHz范圍內連續調整,也可通過I2C總線設置邏輯位BF1-BF6和BR0-BR5來實現。

??? ZL10036芯片中還帶有放大器的直流偏移校正電路。它通過一個內置的偏置矯正反饋放大器消除放大器的直流偏移。在放大器的增益達到飽和狀態時,直流偏移會影響放大器的工作點而影響非線性性能。但是,偏移校正電路中的時間常數會影響芯片的上電時間,所以在對上電時間要求比較嚴格的情況下,可以通過外接交流短路電容來禁用偏移校正功能[4]。

1.2 PLL頻率合成器部分

??? ZL10036芯片中用于與射頻信號混頻的本振信號由芯片內電荷泵鎖相環(CPPLL)頻率合成器產生。在電荷泵鎖相環中,鑒頻鑒相器與電荷泵相結合使得采用無源環路濾波器" title="環路濾波器">環路濾波器的電荷泵鎖相環理論上能產生無限的直流增益和無窮大的頻率牽引范圍,并且獲得零靜態相位誤差[2][3]。

??? ZL10036中所采用的整數分頻" title="分頻">分頻頻率合成器結構是一種最基本的電荷泵鎖相環結構,其結構如圖2所示,包括由晶體振蕩器產生的參考時鐘、鑒頻鑒相器、電荷泵、環路濾波器、壓控振蕩器、可編程分頻器。鑒頻鑒相器比較兩個信號的相位與頻率差,并且產生up和down的控制信號給電荷泵,電荷泵相應地給環路濾波器充放電,壓控振蕩器的輸出頻率正比于環路濾波器上的控制電壓,最終使參考時鐘與可編程分頻器輸出信號同頻同相,從而壓控振蕩器的輸出信號頻率為參考時鐘信號頻率的N倍,N為芯片內15位可編程分頻器的分頻比。

?

??? ZL10036芯片中除了環路濾波器和參考時鐘需要外接之外,其他所有構成電荷泵鎖相環路的組成部分都已經集成在片內。其中外接環路濾波器采用無源一階低通濾波器,而參考時鐘信號由外接晶體振蕩器電路產生的振蕩信號經過芯片內的參考分頻器(REFERENCE DIVIDER)分頻后得到。

??? 15位可編程分頻器和參考分頻器的分頻比,以及電荷泵的最大電流均通過I2C總線設置芯片相關邏輯位實現控制。此外,壓控振蕩器組的工作也由I2C總線根據分頻比的設置情況實現自動控制,不需要人為干預,非常方便。

1.3 邏輯控制部分

??? ZL10036芯片內有13字節的寄存器空間,用戶可以通過對這些寄存器進行寫操作實現對芯片的控制和芯片工作參數的設置。還可以對這些寄存器進行讀操作以監視芯片的工作。

??? 下面對ZL10036的13個寄存器的功能和設置做一個簡單和必要的介紹,圖3是ZL10036寄存器映像表。

?

????字節1:芯片地址字節,用于總線對芯片尋址。

??? 字節2,3:PLL頻率合成器15位可編程分頻器分頻比的控制位。

??? 字節4:LEN為射頻旁路功能使能位;BG0和BG1為基帶后置濾波器增益控制位;BA0和BA1為基帶前置濾波器增益控制位;RFG為RF數字控制增益的控制位。

??? 字節5:R0~R4為參考分頻器分頻比的設置位;C0和C1為電荷泵最大電流控制位;P0為通用輸出端。

????字節6:RSD為基帶濾波器電阻轉換使能位。為了改善I、Q兩通道的帶寬和相位的同步,基帶濾波器使用了電阻轉換技術(resistor switching technique),濾波器中使用不同的電阻值把濾波器基帶帶寬分成了三個子帶,當帶寬設置正好處于3個子帶的2個交點處時,帶寬的準確性可能會下降。這個問題可以通過使用RSD位禁止電阻轉換來解決:每當芯片上電時,RSD位默認為0,電阻轉換可用,芯片根據用戶設置的帶寬自動選擇合適的電阻值,然后用戶置RSD為1,禁用電阻轉換,使其固定在已選值。

??? 字節7:BF1~BF6用來調節基帶濾波器的帶寬,其取值為0~62(63無效),與BR0~BR4(見字節13)共同確定基帶濾波器帶寬;P1是通用輸出端。

??? 字節8~10:其上電值分別為0xDB、0x30、0xE1,初始化時應按硬件的要求分別置為0xD3、0x40、0xE3。

??? 字節11:初始化時要用0x5B、0xF9寫入兩次,寫入的順序可以改變。

??? 字節12:僅供測試用。

??? 字節13:TL為緩沖本振輸出選擇位,此位為1,用于測試目的的本振信號會從LOTEST腳輸出,此位上電值為0;CLR位是控制邏輯重置位;BR0~BR4,取值為4~27(其他數值無效),與BF1~BF6(見字節7)共同確定基帶濾波器帶寬;PD為芯片節電模式控制位。

2 ZL10036的應用實例

2.1 硬件設置

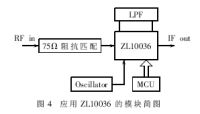

??? 在本文涉及的實際應用中,使用ZL10036作為核心芯片構建了一種可用于通信系統的射頻至基帶轉換器。由于ZL10036芯片的集成度非常高,應用中對芯片的硬件設計涉及比較少,也相對比較簡單,主要是接入鎖相環路中的無源低通濾波器以及振蕩電路。另外,射頻輸入端要提供 的阻抗匹配。這些外圍電路的接法可以參照ZARLINK公司提供的數據手冊,其模塊簡圖如圖4所示。

的阻抗匹配。這些外圍電路的接法可以參照ZARLINK公司提供的數據手冊,其模塊簡圖如圖4所示。

?

???? ZL10036使用了40腳的QFN封裝,體積很小,高頻端的布線必須考慮射頻干擾。芯片的底部有一個散熱支架(thermal paddle),具有很高的熱傳導率,裸片(die)散發的熱量可以通過支架高效傳出;同時支架對地的連接電阻很小,不會影響芯片工作。ZL10036芯片工作時具有相當高的能量密度,如果多余的熱量不能有效散發,芯片會迅速被加熱至超過正常工作的極限溫度125℃,影響芯片的性能甚至燒毀。所以,為了確保良好接地散熱,芯片焊上后,應再從背面滴注焊錫。另外,為了減小版圖尺寸,采用0402封裝的電容電阻元件。

2.2 軟件設置

??? 在通過I2C總線對芯片控制寄存器進行寫操作時,主控制器(MCU)發出正確的地址信號(地址字節值的確定參見文獻[1])后,ZL10036給出應答,在下一個時鐘信號來臨時開始寫入數據。每寫完一個字節,ZL10036都會發出一個應答信號,主控制器收到應答信號后可以發出結束信號終止寫操作,也可以繼續對下一字節進行寫操作,當寫完12個字節后,如主控制器繼續發出寫入數據,則ZL10036將忽略這些數據字節。

??? ZL10036還提供了非常方便的寄存器子尋址(Register Sub-Addressing)方式,當需要改變的是某些寄存器的值時,并不需要把所有的寄存器都重寫。每一對編號為相鄰的偶數、奇數的寄存器對可以被單獨尋址,如字節2、3或者4、5等。例如,要改寫字節7的值,必須先用C$($代表一位16進制數)的數據尋址到字節6,同時芯片用C$重寫字節6。注意,只要是C開頭的數據字節,芯片即自動尋址到字節6。對于所有的字節對,寫入的順序可以是任意的,用戶可以根據需要自定。

??? 軟件的主體是把計算好的(或者是芯片要求的)值按一定的順序寫入芯片的12個寄存器。在本應用中外部晶振采用10MHz,參考分頻器的分頻比取32,頻率合成器的初始工作頻率取為1000MHz,可編程分頻器的分頻比為3200,基帶濾波器的帶寬取為16MHz。由這些值根據芯片數據手冊中的公式[1]得到如下的寫入數據和順序(寫入順序不是惟一的):

??? (1)首先對芯片尋址(地址為0xC2);

??? (2)順序寫入字節2(0x0C)、3(0x80)、4(0x9F)、5(0x44);

??? (3)用0xC0、0x24寫字節6、7;

??? (4)用0xC8重寫字節6(硬件要求,見字節6的說明);

??? (5)用0xD3、0x40寫字節8、9(此2值為硬件要求);

??? (6)用0xE3、0x5B寫字節10、11;(此2值為硬件要求);

??? (7)用0xE3、0xF9重寫字節10、11;(硬件要求重寫11字節);

??? (8)用0xF0、0x45寫入字節12、13。

2.3 單片機控制程序

??? 本應用采用51單片機作為微控制器(MCU)對ZL10036進行控制和設置,其中單片機與ZL10036的I2C接口連接采用軟件模擬的方式。所謂軟件模擬,就是用單片機的I/O口來模擬I2C總線的工作時序,從而達到能夠訪問帶I2C總線接口器件的目的[5][6]。單片機的任意兩個輸出端與ZL10036的12腳SCL、13腳SDA分別相連即可,本應用中選用P3.3和P3.4。采用軟件模擬的方式模擬I2C總線的通信時,最重要的是確保典型信號的時序要求,如開始信號、數據傳送、應答信號和停止信號等,具體參見文獻[6]。下面給出本應用的51單片機控制程序。

IIC_WRITE:?SETB?P3.3??;先使I2C總線

??? ??????? SETB?? ??P3.4??;處于空閑狀態

??????? ??? NOP

??????????? CLR???P3.4??;開始信號

??????????? NOP

??????????? CLR?? P3.3;SCL拉低,避免誤傳數據

??? ??????? MOV?? R1,#0FH;準備16字節的循環傳送

LOOP:????? MOV?? DPTR,#DATA;傳送的數據首地址送入數據指針

??????????? MOV?? A,@DPTR;數據送入累加器

??????????? LCALL WRITE_BYTE;長調用寫一個字節數據的子程序

??????????? INC DPTR;數據指針指向下一個傳送

??????????? DJNZ R1,LOOP;數據循環

??????????? CLR?? P3.3;拉低SCL,停止傳送數據

??????????? NOP

??????????? CLR P3.4;拉低SDA,準備發送結束信號

??????????? NOP

??????????? SETB P3.3;拉高SCL,準備發送結束信號

??????????? NOP

??????????? SETB?? P3.4;結束信號

??????????? NOP

??????????? SJMP?? $;停止

WRITE_BYTE:MOV?? R0,#08H;八位循環控制

????GO_ON: NOP

??????????? CLR?? P3.3;準備傳送數據

??????????? NOP

??????????? RLC?? A;A移位,把待傳數據放入C

??????????? MOV?? P3.4,C;放數據到數據線

??????????? SETB? P3.3;置SCL高,使數據穩定傳輸

????????????DJNZ? R0,GO_ON;循環傳送

??????????? CLR?? P3.3;發第九個時鐘信號,

??????????? NOP;準備接收應答信號。

??????????? SETB? P3.3

????????????NOP

???? WAIT:?JB??? P3.4,WAIT;等待應答信號

?????????? ?CLR?? P3.3;釋放SCL

??????????? RET

??????????? ORG?? 0D40H;存放數據單元

???? DATA:?DB 0C2H,0CH,80H,9FH,44H,0C0H,24H,0C8H,0D3H,40H,0E3H,5BH,0E3H,0F9H,0F0H,45H

??????????? END

2.4 測試結果

??? 測試中選用芯片頻率合成器產生的本振頻率為1318MHz,把頻率為1288MHz的輸入射頻信號下變頻至30MHz的基頻信號。采用的測試儀器是HP公司的8566A頻譜分析儀。

??? 由于頻率合成器產生的本振功率很小(典型值為-60dBm),下變頻的幅值也較小,所以該應用主要關注信噪比。經過頻譜儀的測量,頻率合成器的本振信號和中頻輸出信號的信噪比都令人滿意,均為25dB左右。通過對樣機的測試實驗,系統其他的主要性能指標,如頻率準確度、鎖相環的捕獲性能、帶寬等都達到了設計要求。

??? ZARLINK公司的ZL10036芯片是一款工作在950~2150MHz頻段的高性能高集成的接收機芯片。它直接給出了RF到基帶的解決方案,大大簡化了接收機的結構設計,縮短了產品開發周期,降低了成本。普通的解調芯片,如MAX2701內部不集成本振模塊,本振需要從外部引入,而ZL10036的最大的特點就是把一般需要兩片芯片分別實現的射頻至基帶轉換和PLL頻率合成功能集成至一片芯片中,不但提高了集成度,也極大地方便了用戶。此外,ZL10036內部的可調帶寬的基帶濾波器和寄存器控制系統也獨具特色,目前,在數字衛星系統以及通信系統設備中得到了越來越廣泛的應用,尤其與ZARLINK公司的配套芯片(如ZL10313)配合使用可以提供一套完整的數字衛星信號的解調方案。

????本文介紹了一種將ZL10036用于基帶轉換接收機的設計。主要圍繞ZL10036的應用技巧介紹了該系統射頻模塊的硬件和軟件設計。對射頻至基帶轉換系統的實測結果也取得了較好的一致性,參數都達到了系統設計的指標要求。

參考文獻

[1] ZL10036 Digital satellite tuner with RF bypass data sheet.Zarlink Semiconductor Inc.Copyright.2004-2005.

[2] 張厥盛,鄭繼禹,萬心平.鎖相技術.西安:西安電子科技大學出版社,1994.

[3] 陳文煥.電荷泵鎖相環的基礎研究.成都:電子科技大學碩士學位論文,2005.

[4] 李 多,陳雅琴,馮正和.MAX2701及其在衛星接收機中的應用.電子技術應用,2003,(9).

[5] 陳光東.單片微型計算機原理與接口技術.武漢:華中理工大學出版社,1999.

[6] 凌六一,伍 龍.基于軟件模擬的51單片機IIC總線的實現.電子技術,2004,(5).