FPGA(Field Programmable Gate Array,現場可編程門陣列)是一種高密度可編程邏輯器件,它支持系統可編程,通過寫入不同的配置數據就可以實現不同的邏輯功能。使用FPGA來設計電子系統,具有設計周期短、易于修改等明顯特點,特別適合于進行科學實驗、樣機研制和電子產品的小批量生產。

本文針對FPGA器件,用EDA工具軟件Max+P1usⅡ,設計了一種出租車的計價器,它可以以十進制數的形式,直觀地顯示出租車行駛的里程和乘客應付的費用,具有一定的實際應用價值。

1 系統設計要求

所要設計的出租車計價器,要求能夠顯示里程數和乘客應付的費用,其中里程數精確到0.1km,乘客應付的費用精確到O.1元,顯示必須以十進制的形式來進行。出租車的計費標準為:起步價6元,里程在3 km以內均為起步價;里程在3~7 km之間時,每行駛1 km增加1.6元;超過7 km時,每行駛1 km增加2.4元。

2 系統設計方案

該系統的設計可以采用分立元件來搭建,也可以通過單片機來設計,而使用可編程FPGA來設計,具有設計周期短、易于修改等明顯特點,而且隨著可編程邏輯器件和EDA軟件的飛速發展,越來越多的電子系統采用FPGA來設計,一旦該系統達到一定的量產規模,也比較容易轉化為ASIC芯片設計。因此,基于FPGA來設計一個出租車的計價器。本系統在EDA工具軟件MAX+plusⅡ中,采用硬件描述語言Verilog HDL和原理圖設計相結合的方法,進行各個模塊的設計,最終將各個模塊組成整個系統。

出租車能夠顯示行駛的里程,可以通過車輪的轉動產生脈沖,然后通過計數器對脈沖進行計數來實現。假設出租車每行駛2 m就產生一個脈沖。由于里程數要精確到O.1 km,也就是100m,因此每經過50個脈沖就要輸出一個新的脈沖信號,這里稱為100 m脈沖信號,作為里程計數器的時鐘信號,可以通過一個模為50的計數器進行分頻而得到。

里程計數器可以用一個三位BCD碼計數器來實現,最大能顯示到999。以前兩位為整數,第三位為小數,也就是最大能顯示里程99.9 km,因為出租車都在市區和近郊活動,三位BCD碼計數器是可以實現里程計數的。里程計數器每計數1 km還會周期性地輸出一個脈沖信號,稱為1 km脈沖信號,可以通過一定的組合電路來實現。

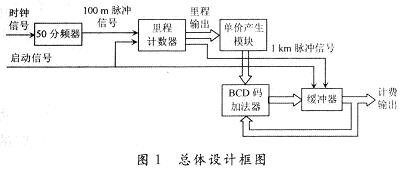

系統最核心的部分就是計費如何實現。這里就需要設計一個BCD碼的加法器,在起步價的基礎上,根據行駛里程的不同,依據計費標準,每增加1 km加上一個單價,單價的產生可以用Verilog HDL編寫程序來實現。系統的總體設計框圖如圖1所示。

2.1 單價產生模塊

單價產生模塊的Verilog HDL源程序如下:

其中輸入信號bai和shi就是里程計數器輸出的兩位整數里程,輸出信號jia就是根據計費標準而產生的單價,以三位BCD碼的形式輸出,以前兩位為整數,第三位為小數。即里程在3 km以內時,jia=0;里程在3~7 km之間時,jia=016(1.6元);超過7 km時,jia=024(2.4元)。

用Verilog HDL編寫程序來實現模塊功能的優點在于,當出租車的計費標準發生變化時,可以很容易地通過改寫程序來完成新的設計,比起硬件電路的修改要方便得多,這也是用Verilog HDL來實現模塊功能的重要優勢。

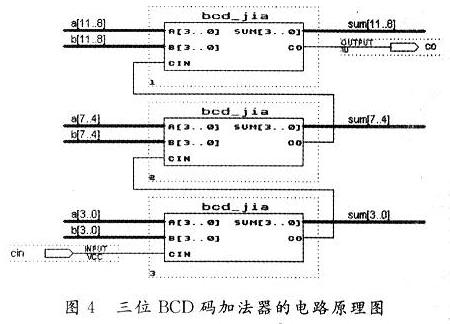

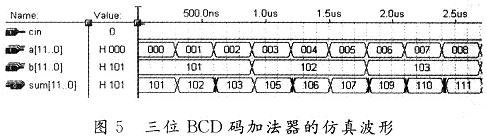

2.2 三位BCD碼加法器

系統中用到了三位BCD碼加法器,可以實現三位十進制數的加法運算。加法器輸出的結果就是乘客應付的費用,這里同樣以前兩位為整數,第三位為小數,也就是最大能顯示99.9元。三位BCD碼加法器由三個一位BCD碼加法器級聯而成。

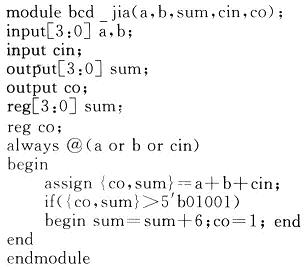

一位BCD碼由四位二進制數組成,四位二進制數的加法運算會產生大于9的數字,必須進行適當的調整才會產生正確的結果。一位BCD碼加法器的Verilog HDL源程序如下:

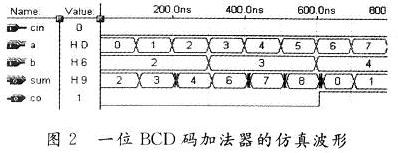

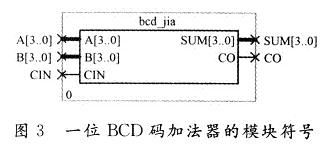

一位BCD碼加法器模塊的仿真波形和生成的模塊符號如圖2和圖3所示。

本模塊中A和B為輸入的一位BCD碼,CIN為低位來的進位信號,CO是本片向高位產生的進位輸出信號,SUM是兩個數相加的和。三位BCD碼加法器由三個本模塊級聯而成,其電路原理圖和仿真波形如圖4和圖5所示。

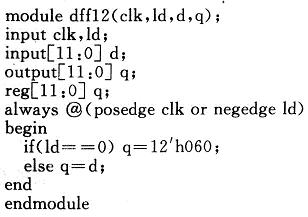

2.3 緩沖器模塊

三位BCD碼加法器輸出的結果通過緩沖器以后,反饋到輸入端重新作為一個加數,在1km脈沖信號的作用下,每來一個脈沖就和單價相加,形成連續累加的功能。緩沖器還有一個控制輸入端LD,LD=O時,在1km脈沖的作用下,輸出起步價6元;LD=1時,在1km脈沖的作用下,輸出和輸入相等。緩沖器的Verilog HDL源程序如下:

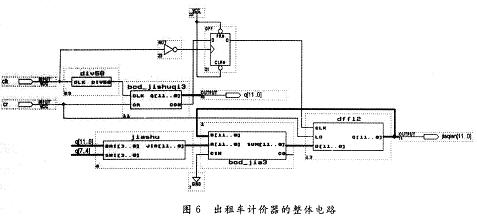

2.4 整體電路

將各個模塊按照輸入輸出關系連接成整體電路如圖6所示。

在整體電路中,clk為最原始的時鐘輸入端,cr為異步清零端,q[11..O]輸出里程,jiaqian[11..O]輸出乘客應付的費用。

3 系統仿真驗證

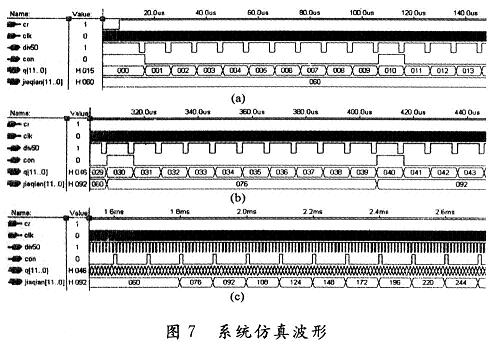

整體電路的仿真波形如圖7所示。

從系統仿真波形圖7(a)中可以看出,當清零端cr=O時,里程數立刻清零,乘客應付的費用顯示三位十進制數060(起步價6元),表示乘客剛上車。當清零端cr=1時,出租車開始行進,里程和費用都開始計數,里程顯示三位十進制數,前兩位為整數,第三位為小數,也就是每行駛100 m計一次數。

從系統仿真波形圖7(b)中可以看出,行駛到3 km時,費用由6元增加為7.6元,行駛到4 km時,費用由7.6元增加為9.2元,在3~7 km之間時,每行駛1 km增加1.6元。

系統仿真波形圖7(c)中顯示了每行駛1 km后,費用逐漸累加的情況。系統仿真波形完全驗證了預期的設計要求。

4 結 語

通過仿真驗證表明,本文所設計的出租車計價器能夠正常地顯示行駛的里程數和乘客應付的費用,符合預定的計費標準和功能要求。基于FPGA的設計,集成度高、設計周期短。尤其是當計費標準發生變化時,容易通過改寫Verilog HDL源程序來完成新的設計。