自2002年美國聯邦通信委員會授權可以無執照使用超寬帶(UWB) 無線電技術以來,大多數采用該技術的商業應用(如無線USB),都是基于用于高數據速率傳輸的頻域調制技術(如OFDM)。UWB這種成熟的技術還可用于納秒級的超短脈沖數據傳輸。這種被稱為脈沖無線電(IR)的系統可通過調制諸如位置或者振幅等脈沖參數來傳輸信息。同時,通過測量脈沖的傳輸時間,還可以進行精確到厘米的測距。這為物流(包裹跟蹤)、制造、搜救(如與救火隊員的通信與定位)或智能導游等不同領域內的大量新型位置感知應用開辟了廣闊的新天地。

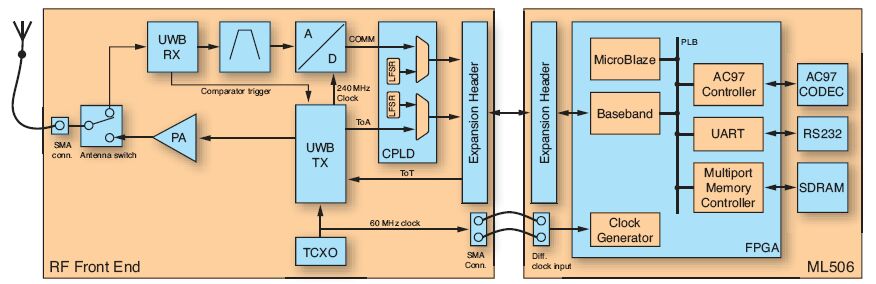

圖1:該系統由非定制的賽靈思ML506板與定制的UWB子板連接而成

歐洲的PULSERS二期是一項由業界主導的UWB無線電技術合作項目,參與的重要行業和學術組織有30家,旨在設計和實施一種可實現每秒百萬比特的數據傳輸速率、測距精度達4厘米的IR-UWB通信和測距系統。該系統由一整套相同的自主節點組成,每個節點都可以與網絡中的其他節點通信并確定與其之間的距離。每個節點由一個定制UWB子板與一個現成的賽靈思ML506開發板上(見圖1)連接而成。Virtex-5 SXT架構的卓越性能與MicroBlaze軟處理器的靈活性相得益彰,使得我們在單個FPGA內即可部署整個基帶信號鏈及所有高級系統層。

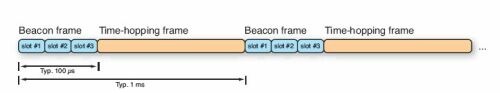

圖2:由三個信標槽組成的周期信標幀夾雜在跳時幀之間

IR-UWB通信和測距

該系統使用支持四種可能的時間位移(4-PPM)的簡單脈沖定位調制來傳輸信息,其中每個脈沖編碼兩個數據位。如圖2所示,脈沖將分組為幀并在預定義的信標幀和跳時幀組成的柵格中傳輸。每個信標幀包含三個相同的可讓客戶用來進行測距或者通信的信標槽。我們原本計劃將跳時幀用于基于跳時編碼的高數據速率傳輸,不過我們將在此后的產品使用該技術,而現在所有的數據傳輸只在信標幀中進行。

我們現在用雙向測距的方法進行測距。雙向測距是通過測量從發送測距請求到從遠程節點(見下表)收到回復的時間延遲來實現的。測距請求一般在信標槽1中發送,而測距回復則一般返回到信標槽3中。這給予了遠程節點一個完整的信標槽間隔(信標槽2,大約33微秒)來處理收到的測距請求并計劃輸回的測距答復。

系統架構

超寬帶子板上帶有脈沖發射器和非相干接收器ASIC,這是我們專門采用IHP的0.25微米SiGe:C BiCMOS技術為該項目設計的。

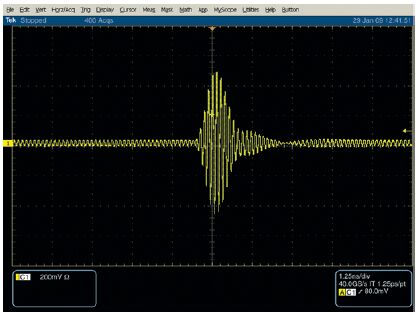

如圖3所示,用來產生UWB脈沖的發射器ASIC能夠對所產生脈沖的振幅和位置進行調制。其包括的3.84GHz計數器可以精確地計劃輸出脈沖的傳輸時間并測量所接收脈沖的到達時間。

圖3:UWB脈沖由7.68GHz的載波和高斯包絡構成

接收路徑在接收器ASIC中分為兩支。帶寬相對較窄(120MHz)的第一個分支主要用于通信和不太精確的脈沖計時,而精確的脈沖計時則通過采用全脈沖帶寬 (750MHz)的第二個分支來完成。傳入的脈沖由該分支上的高速比較器來加以探測。其輸出結果可觸發運行在發射器ASIC內部的3.84GHz計數器的讀出。因此,每個接收到的脈沖到達時間可以260皮秒分辨率進行測量,也即空間分辨率大約為8厘米。

子板與Virtex-5 FPGA內的基帶模塊通過兩條120MHz的數據總線進行通信。通信(COMM)總線負責傳輸ADC樣本,而到達時間總線負責傳輸與收到的脈沖相關的高分辨率時間戳。兩條總線都會通過XC95144XV CPLD,雖然并非必需,但其仍不失為一個出色的調試工具。我們可以設定CPLD在通往FPGA的總線上輸出一系列偽隨機數字。然后我們利用CPLD輸出來調節FPGA的輸入時序并驗證總線線路的完整性。如果在不了解傳輸數據序列的前提下驗證總線線路將會非常困難。

在FPGA 內部,基帶模塊(見圖4)同時負責對發出的脈沖進行編碼并解碼收到的脈沖。而基帶模塊的傳輸相對簡單,主要包括外部(CRC)和內部(卷積)編碼。接收部分的實施還另外涉及一個信道估計器和一個定制的Viterbi解碼器,因而要占用更多的資源。基帶模塊通過處理器局部總線(PLB)接口與處理器系統相連接。

圖4:基帶模塊的接受(頂部)和傳輸鏈。

計算出單程信號傳輸延遲,再乘以光速后,就得到了A和B之間的距離。

3.84GHz時鐘的260皮秒時間分辨率為可實現大約8厘米的空間分辨率。不過,由于無線信號在兩個節點之間被傳輸了兩次,因而可以4cm的分辨率確定距離。

在知道自身與三個非共線參考節點的距離之后,移動節點可計算出其2D位置。而使用4個非共面的參考節點,甚至可確定出其3D位置。

作者:森海塞爾電氣股份公司研發工程師Guy Eschemann,[email protected];IMST GmbH項目經理Heinz Ludiger,[email protected];IMST GmbH資深科學家Birgit Kull,[email protected]