1 引言

隨著存儲技術的不斷進步,Flash Memory的存儲容量越來越大,讀寫數度越來越快。性能價格比越來越高。但是,NAND Flash本身存在缺點,歸納起來有兩點:讀寫控制時序復雜和位交換(o、1反轉)問題。NAND Flash器件能夠復用指令、地址和數據總線,從而節省了引腳數量,但引腳不僅承擔著數據總線的功能,還承擔著地址及指令總線的功能,所以造成接口控制時序復雜。位反轉的問題更多見于NAND Flash,NAND Flash的供應商建議使用NAND Flash的同時使用EDC/ECC校驗算法。

本文實現的NAND Flash控制器放置在CPU和NANF Flash器件之間,實現了NAND Flash的無粘接接口,可以大大簡化CPU對NAND Flash的操作時序,提高CPU的使用效率。ECC功能可以保證存儲數據的準確性,ECC模塊和主控模塊相對獨立,在不需要ECC功能的時候,只需不使能ECC模塊,方便靈活。

2 控制接口電路的功能特性

整個控制接121電路分為兩大功能模塊:第一個功能模塊為主控制器模塊,該模塊簡化NAND Flash的接口時序,可以為NAND Flash設計一個無粘接接口(Glueless Inter一face),從而使得對NAND Flash操作的時序復雜程度大大降低,使得NAND Flash接口映射為一個類似于SRAM的無粘結接口。第二個功能模塊是ECC模塊,該模塊對512個字節能糾正單比特錯誤和檢測雙比特錯誤,但對單比特以上的錯誤無法糾正。對兩比特以E的錯誤不保證能檢測。

兩個功能模塊相對獨立,ECC功能模塊位于主控制器模塊與NAND Flash芯片之間,可以選擇工作與不工作,主控制器模塊的所有命令都會通過ECC模塊傳給NANDFlash芯片。當令ECC模塊不工作時。ECC模塊就相當于連接主控制器模塊與NAND Flash芯片的導線;當ECC模塊工作時。只會在豐控制器模塊的操作中加入一些步驟,并不會打亂主控制器模塊的操作時序。

3 主控制器

3.1寄存器和緩存配置

主控制器的外部接口類似于SRAM的,然而SRAM只有讀和寫兩種主要操作。而NAND Flash除r頁編程與讀操作之外還有ID讀取、重置、塊擦除和狀態讀取等操作,在不改變接口的情況下只能采用與NAND Flash類似的寫控制字的方式。主控制器有16字節寄存器組,可以從I/O總線上讀取指令和地址。指令寄存器采用存儲器映射(Memory Mapped Register)的編址方式,也就是說,寄存器的地址統一編入內存空間,從0xFF0到OxFFA。

3.2主控制器的實現

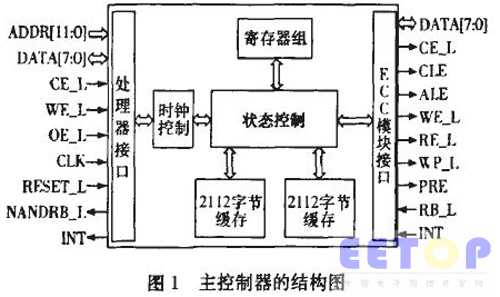

主控制器的結構框圖見圖1。下面分別討論時鐘控制模塊和狀態控制模塊的設計實現。

(1)時鐘控制模塊。對于這種讀寫使能都是低電平有效的芯片,采用占空比為1:1的時鐘進行讀寫操作對提高數據的存取速度并不劃算。比如,進行讀取操作時,RE_L至少要保證低電平35ns才能保證數據被正確讀取,RE_L上升為高電平后只要保證數據再被保持10ns的時間就行,這樣加上5ns的余量,時鐘周期至少也要為80ns。為r保證數據能夠被正確讀取,并盡量提高讀取速度,我們采用16.7MHz即周期為60ns,占空比為1:2的時鐘。這種情況下,低電平持續時間為40ns,35ns數據確信被讀取后,仍有5ns的余量,高電平有20ns時間,也很充裕,既保證了數據的正確讀取。又充分發揮了器件的性能。

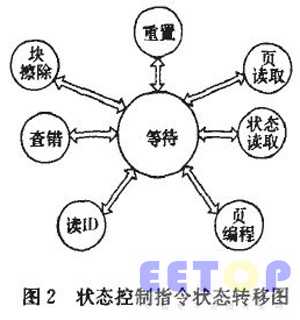

(2)狀態控制模塊。如圖2所示,主控制器執行可控制

NAND Flash進行重置、塊擦除、頁讀取、查錯、讀ID。頁編程和狀態讀取指令的操作,不支持對NAND Flash的隨機讀寫操作。當地址輸入為0xFFA時,指令寄存器中的命令字就會被讀取,確定下一步要執行的指令,然后轉移到相應的狀態。

4 ECC模塊

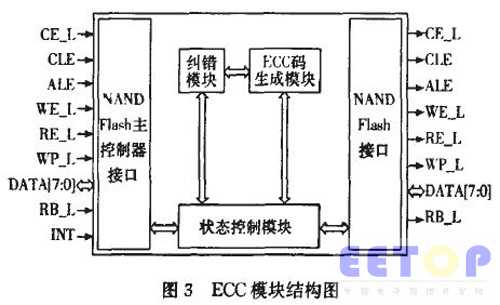

NAND Flash器件都受位交換現象的困擾,在某些情況下一個比特位會發生反轉。本節論述了專用校驗算法ECC(Error Correction Code,簡稱ECC的設計實現過程。ECC模塊被置于NAND Flash器件和主控制器之間,ECC模塊從主控制器接收各種信號,不需要工作時直接將收到的信號傳給NAND Flash。需要工作時截取主控制器的控制信號,加七自己的操作后再傳給NAND Flash。ECC模塊結構見圖3。

(1)校驗碼生成模塊。ECC校驗碼生成模塊有96比特(12字節)的運算寄存器供運算時暫存數據,分成四組每組三字節的寄存器,這些寄存器保存著奇偶校驗值(也就是各位的異或值),每當數據送人時這些寄存器的值就更新一次。這些奇偶校驗標志的計算基于每字節數據的順序位置及數據本身。

(2)糾錯模塊。當NAND Flash進行讀操作時,讀出的數據將會被ECC碼生成模塊重新計算ECC碼。當主控制器讀完一頁的所有2 010字節數據后,ECC模塊開始讀取事先寫入的FffX2校驗碼,這些校驗碼按字節移人查錯模塊的移位寄存器中。當3字節校驗碼移入寄存器后,查錯模塊將其與新牛成的ECC碼做異或運算并確定錯誤類型及位置,同時將錯誤信息存入一個14位的寄存器中。

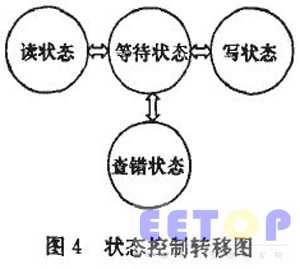

(3)狀態控制模塊。ECC模塊的狀態控制部分控制整個ECC模塊的工作時序,見圖4,同時根據當前的狀態信息輸出狀態信號。對于讀操作,計算一次ECC碼需要512字節,因此每次至少要讀出512字節的數據。為簡單起見,我們只對N趟蛔Flash進行整頁的讀操作,總線上傳輸前2 048字節數據時,ECC模塊計算ECC碼,傳后12字節數據時,ECC模塊將其存下,待數據傳輸完畢后進行校驗,將存下的E(℃碼與計算出的ECC碼進行按位異或,確定數據的正確性。對于寫操作,與讀操作類似,寫操作也要以整頁為單位進行。數據一邊傳入NAND Flash,ECC模塊同時計算ECC碼。當主控制模塊傳人第2 010字節數據后,ECC模塊接管數據總線,將自己計算出的ECC碼傳人NAND Flash。對于查錯操作,當主控制器下0x23指令時進入該狀態。將每頁2 048字節數據共產生的8字節錯誤信息,包括錯誤的位置及種類傳送給主控制器,對于其它操作指令直接傳給NAND Flash芯片。

5 控制接口電路的驗證

對塊擦除指令、頁讀取指令、頁編程指令、重置指令進行功能仿真。地址0XFFA為指令寄存器,0x6代表塊擦除,0x0代表頁讀取,0x8代表頁編程,0xF代表重置。仿真結果如圖5~圖8所示。通過和NAND Flash器件要求的時序圖對比可以看出,控制器輸出的信號完全符合器件的要求。

6 結束語

本文在分析了NAND Flash產品特性的基礎上,給出了NAND Flash控制接口電路的設計方案和驗證結果。本文的創新點是采用同步設計和FSM設計方法,控制接口電路能夠正確地將以SRAM時序輸入的塊擦除、頁讀取、頁編程、ID讀取、重置、狀態讀取操作指令轉化為NANDFlash器件要求的操作時序,大大簡化了NAND Flash的讀寫控制時序。另外,接口控制電路還能實現ECC功能,具有512個字節中發現2比特錯誤、糾正l比特錯誤的檢錯糾錯能力。接口控制電路的各個指令操作功能在Xilinx的Spartarr3 Board上得到了驗證,工作最高頻率達到100MHz。