基于FPGA的PCI總線接口硬件調(diào)試策略

西安電子科技大學(xué) 陳重

摘要: Signal TapⅡ邏輯分析器集成到QuartusⅡ設(shè)計(jì)軟件中,能夠捕獲和顯示可編程單芯片系統(tǒng)(SOPC)設(shè)計(jì)中的實(shí)時信號狀態(tài),這樣,開發(fā)者就可以在整個設(shè)計(jì)過程中以系統(tǒng)級速度觀察硬件和軟件的交互。Signal TapⅡ可支持多達(dá)1024個通道,采樣深度高達(dá)128KB,每個分析器均有1O級觸發(fā)輸入/輸出,從而增加了采樣的精度。

Abstract:

Key words :

在FPGA的設(shè)計(jì)流程中,完成設(shè)計(jì)輸入以及成功綜合、布局布線,只能說明設(shè)計(jì)符合一定的語法規(guī)范,而并不能保證其滿足設(shè)計(jì)人員對功能的要求,因而需要通過仿真對設(shè)計(jì)進(jìn)行驗(yàn)證。仿真驗(yàn)證的目的是為了發(fā)現(xiàn)設(shè)計(jì)的問題,而一旦發(fā)現(xiàn),就需要千方百計(jì)地通過調(diào)試找到問題所在,這其實(shí)也是設(shè)計(jì)中比較困難的。

隨著FPGA可編程器件容量的不斷增大和設(shè)計(jì)復(fù)雜度的日益提高,功能調(diào)試已經(jīng)成為一個很繁重的任務(wù)。為了使設(shè)計(jì)的產(chǎn)品盡快投入市場,設(shè)計(jì)人員需要一種簡易有效的測試工具,以盡可能縮短測試時間,提高測試效率。傳統(tǒng)的邏輯分析儀在測試復(fù)雜的FPGA設(shè)計(jì)時,會面臨以下幾點(diǎn)問題:

(1) I/O引腳有限。設(shè)計(jì)中器件的選擇依據(jù)設(shè)計(jì)規(guī)模而定,通常所選器件的I/O引腳數(shù)目和設(shè)計(jì)的需求是恰好匹配的;

(2) I/O引腳難以引出。設(shè)計(jì)者為減小電路板的面積,大都采用細(xì)間距工藝技術(shù),這在不改變PCB板布線的情況下引出I/O引腳非常困難;

(3)外接邏輯分析器有可能改變FPGA設(shè)計(jì)中信號的原來狀態(tài),因此,很難保證待測信號的正確性;

(4)傳統(tǒng)的邏輯分析器價格昂貴,會增加設(shè)計(jì)成本。

1 Signal Tap硬件調(diào)試原理

為了盡快使設(shè)計(jì)的產(chǎn)品投入市場,就要盡可能地縮短設(shè)計(jì)驗(yàn)證所耗費(fèi)的時間。為此,Altera公司推出了一種新的調(diào)試工具。這種型號的Sig-nal TapⅡ的邏輯分析器具有無干擾、便于升級、使用簡單、價格低廉等優(yōu)點(diǎn),可滿足FPGA開發(fā)中硬件調(diào)試的要求。

Signal TapⅡ邏輯分析器集成到QuartusⅡ設(shè)計(jì)軟件中,能夠捕獲和顯示可編程單芯片系統(tǒng)(SOPC)設(shè)計(jì)中的實(shí)時信號狀態(tài),這樣,開發(fā)者就可以在整個設(shè)計(jì)過程中以系統(tǒng)級速度觀察硬件和軟件的交互。Signal TapⅡ可支持多達(dá)1024個通道,采樣深度高達(dá)128KB,每個分析器均有1O級觸發(fā)輸入/輸出,從而增加了采樣的精度。可以說,Signal TapⅡ?yàn)樵O(shè)計(jì)者提供了業(yè)界領(lǐng)先的SOPC設(shè)計(jì)的實(shí)時可視性,它能夠大大減少驗(yàn)證過程中所花費(fèi)的時間。目前,SignalTapⅡ邏輯分析器可以支持的器件系列包括:APEXT II,APEX20KE,APEX20KC,APEX20K,Cyclone,Ex-calibur,Mercury,Stratix GX,Stratix等。Signal TapⅡ?qū)⑦壿嫹治瞿K嵌入到FPGA中,圖1所示是Signal TapⅡ的嵌入式邏輯分析器結(jié)構(gòu)框圖。圖中,邏輯分析模塊可對待測節(jié)點(diǎn)數(shù)據(jù)進(jìn)行捕獲。并將數(shù)據(jù)通過JTAG接口從FPGA傳送到QuartusⅡ中顯示。使用Signal TapⅡ無需額外的邏輯分析設(shè)備,只需將一根JTAG接口的下載電纜連接到要調(diào)試的FPGA器件,Signal TapⅡ在對FPGA的引腳和內(nèi)部的連線信號進(jìn)行捕獲后,便可將數(shù)據(jù)存儲在FPGA的RAM塊中。因此,需要為采樣信號、觸發(fā)信號和待測信號預(yù)留一定數(shù)目的RAM塊。

2 使用Signal Tap的一般流程

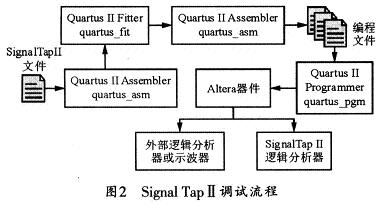

圖2所示是Signal TapⅡ的調(diào)試流程示意圖。使用Signal TapⅡ的一般流程,是在完成設(shè)計(jì)并編譯工程后,建立Signal TapⅡ(.stp)文件并加入工程,然后再配置STP文件,并將其編譯并下載設(shè)計(jì)到FPGA中,接著在QuartusⅡ軟件中顯示被測信號的波形,并在測試完畢后將該邏輯分析器從項(xiàng)目中刪除。

其Signal TapⅡ文件設(shè)置和采集信號數(shù)據(jù)的基本流程如下:

(1)建立新的Signal TapⅡ文件;

(2)設(shè)置采樣時鐘。采樣時鐘決定了顯示信號波形的分辨率,它的頻率要大于被測信號的最高頻率,否則將無法正確反映被測信號波形的變化。Signal TapⅡ通常在時鐘上升沿將被測信號存儲到緩存。

(3)設(shè)置被測信號。可以使用Node Finder中的SignalI TapⅡ?yàn)V波器查找所有預(yù)綜合和布局布線后的Signal TapⅡ節(jié)點(diǎn),添加要觀察的信號。邏輯分析器不可測試的信號包括:邏輯單元的進(jìn)位信號、PLL的時鐘輸出、JTAG引腳信號、LVDS(低壓差分)信號等。

(4)配置采樣深度,確定RAM的大小。Signal TapⅡ所能顯示的被測信號波形的時間長度為TX,其計(jì)算公式如下:

TX=NTS

式中,N為緩存中存儲的采樣點(diǎn)數(shù),TS為采樣時鐘的周期;

(5)設(shè)置buffer acquisition mode。buffer ac-quisition mode包括循環(huán)采樣存儲和連續(xù)存儲兩種模式。循環(huán)采樣存儲也就是分段存儲,即將整個緩存分成多個片段(segment),每當(dāng)觸發(fā)條件滿足時就捕獲一段數(shù)據(jù)。該功能可以去掉無關(guān)的數(shù)據(jù),使采樣緩存的使用更加靈活;

(6)觸發(fā)級別。Signal TapⅡ支持多觸發(fā)級的觸發(fā)方式,最多可支持1O級觸發(fā),設(shè)計(jì)人員可以只查看最重要的數(shù)據(jù)。

(7)觸發(fā)條件。Signal TapⅡ邏輯分析器可支持多個觸發(fā)位置以及外部觸發(fā)事件,可以使用Signal TapⅡ邏輯分析器窗口中的Signal Configu-ration面板來設(shè)置觸發(fā)器選項(xiàng),也可以設(shè)定復(fù)雜的觸發(fā)條件來捕獲相應(yīng)的數(shù)據(jù),以協(xié)助調(diào)試設(shè)計(jì)。當(dāng)觸發(fā)條件滿足時,可在Signal Tap時鐘的上升沿采樣被測信號。

3 使用Signal Tap調(diào)試PCI主設(shè)備控制器

Signal TapⅡ邏輯分析器的使用大大加快了PCI主設(shè)備控制器的調(diào)試進(jìn)程,例如在調(diào)試DMA傳輸后的中斷產(chǎn)生時,由于軟件檢測不到中斷而導(dǎo)致DMA傳輸結(jié)束后,可能會使計(jì)算機(jī)死機(jī)而不能正常結(jié)束(完整的流程是:DMA傳輸結(jié)束,產(chǎn)生中斷,并在軟件檢測到中斷后進(jìn)人中斷服務(wù)程序來處理中斷,然后清除)。

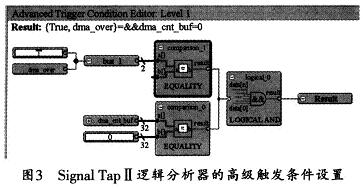

對中斷產(chǎn)生的條件進(jìn)行檢查時,32位的DMA計(jì)數(shù)器必須為0,而且DMA傳輸結(jié)束標(biāo)志信號必須有效,針對這一條件,使用普通的示波器和邏輯分析器根本無法跟蹤到,但是使用SignalTapⅡ邏輯分析器的高級設(shè)置,就可將這兩個條件作為觸發(fā)條件,從而檢測到中斷是否產(chǎn)生,其高級設(shè)置如圖3所示。

4 結(jié)束語

與傳統(tǒng)邏輯分析器相比,使用Signal TapⅡ邏輯分析器有以下優(yōu)勢:

(1)不占用額外的I/O資源。若使用傳統(tǒng)的邏輯分析儀觀察信號波形,則必須將待觀察信號引到空閑管腳,這樣,在器件管腳緊張的時候,Signal TapⅡ邏輯分析器的優(yōu)點(diǎn)就可以得到充分地體現(xiàn)。

(2)不占用PCB空間。若使用傳統(tǒng)邏輯分析儀,則需要從FPGA器件上引出測試管腳到PCB上,這樣會增加PCB走線難度;

(3)不破壞信號的完整性;

(4)傳統(tǒng)邏輯分析儀價格昂貴,而將Signal TapⅡ邏輯分析器集成在QuartusⅡ軟件中,無需另外付費(fèi);

因此,可以預(yù)見,Signal TapⅡ邏輯分析器將受到越來越多的設(shè)計(jì)工程師的青睞。

來源:電子元器件應(yīng)用

此內(nèi)容為AET網(wǎng)站原創(chuàng),未經(jīng)授權(quán)禁止轉(zhuǎn)載。