l 引 言

PowerPC是1993年IBM,Apple和Motorola公司(其半導體部門現在分拆為Freescale公司)聯盟的共同設計的。PowerPC技術以RISC(精簡指令集計算機)為基礎,該技術由IBM的POWER(性能優化的增強RISC)體系結構而來。因PowerPC芯片具有高性能和低功耗的特點,主要應用在嵌入式系統。MPC7410是新一代G4處理器,通過加入A1tiVec技術,處理能力達到4G FLOPS,而1.8V的低電壓操作大大降低了芯片的功耗,提高了系統的穩定性。MPC7410內部主頻最高為500 MHz,每個時鐘周期最多可以執行8條指令,其中包括4條矢量運算(A1tiVec)指令和2條整型指令。系統采用MPC7410為核心處理器搭建嵌入式系統硬件平臺。利用Tsi107芯片組的PCI接口連接以太網。網口是系統非常重要的通信接口,通常情況下操作系統映像的下載以及與外界的通信都是通過以太網口進行的。文中介紹了以太網接口硬件設計和VxWorks BSP的開發。

2 系統結構概述

整個系統結構框圖如圖1所示。

在系統中使用了Motorola公司的RISC處理器Pow—erPC7410作為核心處理器,該處理器具有高性能和低功耗的特點,外接一個2 MB L2作為二級緩存,以提高運算速度。以Tundra公司為PowerPC專門設計的橋芯片/存儲器控制器Tsil07作為北橋芯片,利用60X總線和MPC7410相接,用以把60X總線信號轉化為PCI總線信號,并管理FLASH和SDRAM。此設計充分利用60X總線高數據傳輸速率和優秀的連接性能,發揮了MPC7410的高可靠性和強大的處理能力,使該硬件平臺具有很高的性能。

3 Tsil07的PCI接口

Tsil07的PCI接口與PCI 2.1規范兼容。使用一個32位地址/數據復用線。在PCI總線和處理器或本地memory之間提供內部緩沖。處理器讀和寫操作分別有1個32 B緩沖,memory操作具有2個32 B讀緩沖和2個32 B寫緩沖。PCI總線使用中央仲裁方式,每一個master都有它自己的請求(REQ)和獲得(GNT)信號。可通過一個簡單的請求——獲得握手獲得總線的控制權。仲裁在前一個訪問時發生,故不會占用PCI總線的周期。

Tsil07為自身和另外最多5個PCI總線master提供總線仲裁邏輯,可通過設置PCI仲裁控制寄存器(PACR)的位15決定是否使能(置為1)或禁止(置為O)片內PCI仲裁器。在復位信號(HRESET)為高時采集SDMA9以確定片內PCI仲裁器被使能(低)或禁止(高)。

片內PCI仲裁器使用一個可編程的、兩級、round—robin仲裁算數邏輯,5個外部master的每一個,加上Tsi107使用PACR中的適當位被編成2個優先級,高或低。低優先級組在高優先級組中共同占用一個總線請求傳輸通道。系統中如果有N個高優先級設備和M個低優先級設備,則每一個高優先級設備最少會得到![]() 總線傳輸,每個低優先級的設備最少會得到

總線傳輸,每個低優先級的設備最少會得到![]() 總線傳輸。

總線傳輸。

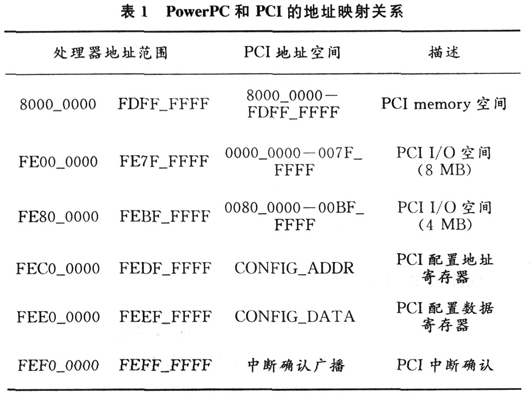

4 地址映射關系

根據Tsi107在電路中所起的作用它的工作方式可以分為2種,host mode和agent mode。在host mode,Pow—erPC是整個板子的主CPU,Tsi107管理整個系統的Memory和PCI總線。在agent mode,PowerPC系統是一個PCI設備,Tsi107負責和PCI主橋通信,管理這個PCI設備局部的memory。整個PowerPC系統受PCI主橋管理。在本系統中Tsi107工作在host mode。Tsil07在host mode時可采用2種地址映射方式,map A和map B。在復位時通過地址映射配置引腳SDBA0選擇地址映射方式。如果Tsi107工作在host mode并且SDBA0上拉,則Tsil07使用map B。建議不使用map A,使用map B時,PowerPC和PCI的地址映射關系如表1所示。

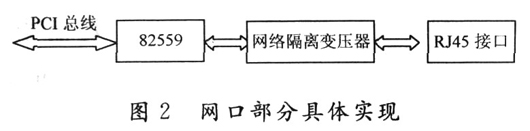

5 網口部分設計

網口部分的設計基于芯片組Tsil07控制的PCI總線,基本框圖如圖2。

網口部分主要由Intel 82559,網絡隔離變壓器和RJ45接口3部分組成。82559是一個高集成度、高性能、低功耗的10/100 Mb/s快速以太網控制器,符合LON設計規范。物理尺寸只有15 mm×15 mm,是一款高性價比芯片。82559有完整的PCI接口,既可作主設備又可作從設備,在系統上電對其進行配置時只能作為從設備,正常工作后可作為主設備。32位的PCI控制器使82559在PCI總線上執行高速的數據傳輸。并且PCI控制器可處理通信任務,因而減輕CPU的負擔。82559包含一個傳輸FIFO和一個接收FIFO,大小各為3 kB,在等待總線傳輸時可防止數據的流失。這將使82559利用最小的幀間距傳送數據。82559可工作在全雙工和半雙工模式。82559連接一個E2PROM,E2PROM為硬件和軟件提供上電初始化。在82559芯片上集成了MAC(介質訪問子層)和PHY(物理層)的功能,通過片上的命令和狀態寄存器經由PCI總線和PowerPC通信。H1102是一個網絡隔離變壓器,82559通過網絡隔離變壓器驅動剛45網線接口,用來支持10/100BASE—T,實現與外界通信。

6 以太網的VxWorks BSP的開發

BSP即Board Support Package,板級支持包,是對目標系統的底層支持軟件。對于具體的硬件平臺,與硬件相關的代碼都被封裝在BSP中,由BSP向上提供虛擬的硬件平臺,BSP與操作系統通過定義好的接口進行交互。BSP是所有與硬件相關的代碼體的集合,是介于底層硬件和上層操作系統之間的一層,主要目的是為了支持操作系統,使之能夠更好地運行于硬件系統。以下介紹了網口的VxWorks BSP的開發方法。

6.1 Tsil07的PCI接口的寄存器初始化

對Tsil07的PCI接口的寄存器初始化主要是對PCI命令寄存器,PCI狀態寄存器,PCI仲裁控制寄存器等和PCI相關的寄存器設置。因用戶手冊上對各寄存器的參數進行了詳細的說明,在此將不再贅述。

Tsil07中的32位配置寄存器地址是0x8000_00nn,nn是寄存器的相對偏移地址。對配置寄存器的訪問采用間接方式,將配置寄存器的地址寫到CONFIG_ADDR端口,則配置寄存器的內容將在CONFIG_DATA端口獲得。CONFIG_ADDR端口的地址為:OxFEC0_0000~OXFEDF_FFFC,CONFIG_DATA端口的地址為0xFEE0_0000~0xFEEF_FFFF。

6.2 82559的PCI接口的寄存器初始化

對Tsil07的PCI接口的寄存器初始化包括對PCI命令寄存器,PCI狀態寄存器,Cache行大小(CLS)寄存器等寄存器的設置,以便能夠找到PCI設備82559,使Power—PC能夠對該設備進行訪問。

PCI定義了3個地址空間:PCI memory空間,PCII/O空間和PCI配置空間。PCI memory空間,PCI I/O空間采用直接訪問。PCI支持2種類型的配置訪問,typeO和type 1。AD[31:O]信號表示地址時根據配置訪問的類型使用不同的形式,地址的低兩位表明配置訪問的類型——type O(AD[1:O]=ObOO)或type 1(AD[1:O]=Ob01)。2種地址形式都表明了一個具體的設備和該設備的一個具體的配置寄存器。typel 0用于在本地PCI總線上選擇一個設備,type 1通過一個PCI—to—PCI橋傳遞配置請求到另一個PCI總線。系統采用type O配置,如圖3所示。

為訪問配置空間,必須向CONFIG_ADDR寄存器寫入一個32位的值,用于定義目標PCI總線、該總線上的目標設備和設備中要訪問的配置寄存器。對CONFIG_DATA寄存器的一個讀或寫操作將使主橋將該訪問轉化為一個PCI配置周期(CONFIG_ADDR中的使能位被設置并且設備編號不是0b1_1111)。

對于map B,處理器可在地址空間0xFEC0_0000~0xFEDF_FFFF中使用任何地址訪問CONFIG_ADDR寄存器。盡管系統可以使用0xFEC0_0000~OxFEDF_FFFF中的任何地址,但一般使用地址0xFEC0_0CF8。為簡化CONFIG_ADDR的地址通常被稱為CF8。處理器可在地址空間0xFEE0_0000~0xFEEF_FFFF中的任何地址訪問CONFIG_DATA寄存器。最常用的地址為0xFEE0_OCFC~0xFEE0_0CFF。為簡化起見,一般指為CFC。

對于type O配置,Tsi107把CONFIG_ADDR寄存器的設備編號轉化為惟一的IDSEL信號,它們之間有一一對應的關系。功能編號和寄存器編號將不加改變的復制到AD[10:2],AD[1:O]在type O配置時為0b00。

6.3 中斷的實現

Tsil07的EPIC(可編程中斷控制單元)支持5個外部中斷。IRQ[O:4]信號代表了外部中斷,它們被5個IRQ向量/優先級寄存器(IVPRO—IVPR4)控制和初始化。外部中斷可被設置為電平或邊沿觸發。軟件通過對向量/優先級寄存器的寫操作為每一個中斷源設置優先級,優先級的值在O~15之間,15最高。EPIC單元通過麗向處理器核申請中斷。當處理器通過對EPIC單元中的中斷響應寄存器(IACK)進行讀操作以響應中斷請求時,EPIC返回一個8位的中斷向量到處理器,然后處理器處理該中斷。處理器對EPIC單元的結束中斷(EOI)寄存器進行寫操作時,中斷處理完成。

對EPIC的初始化主要是設置各中斷源的優先級和中斷向量的設置。包括對特征報告寄存器(FRR)、全局配置寄存器(GCR)、偽向量寄存器(SVR)、外部和內部中斷寄存器等的設置。

7 結 語

搭建以MPC7410為核心處理器的嵌入式系統硬件平臺,闡述以太網接口硬件設計和VxWorks BSP的設計方法,使以太網接口在系統中能正常通信。