文獻標識碼: A

文章編號: 0258-7998(2015)03-0048-03

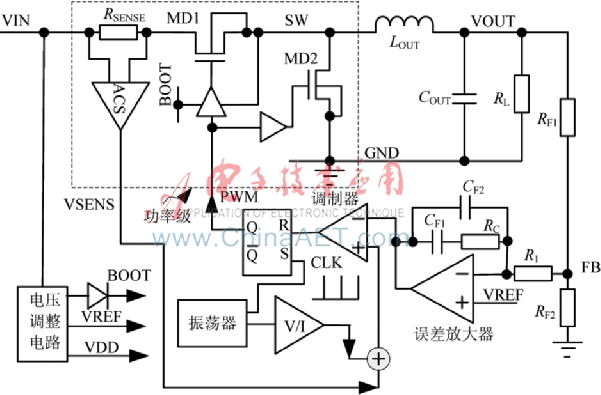

當前,數字多媒體、視頻廣播設備、個人導航設備(PND)、車載電源設備的使用越來越廣泛, 為這些設備提供電源管理,常需要具有高壓大電流高轉換率效的DC-DC轉換器。為了減小設備體積和重量,電源模塊必須最小化,因此,實現轉換器的高轉換效率以及高集成度成為一種趨勢[1-2]。考慮到電壓控制模式和非同步轉換器的一些缺點,更多的系統選擇使用同步電流模式DC-DC轉換器;圖1為典型電流模同步BUCK轉換器的電路框圖,圖中陰影部分為轉換器的功率級,而電流控制模式BUCK DC-DC轉換器中功率級的設計是最重要的功能模塊之一,亦是轉換器設計的難點所在,原因在于:功率級中作為開關的功率晶體管導通電阻會影響系統轉換器的效率,在大負載電流條件下,功率開關晶體管的導通電阻還會影響芯片的熱設計,一般來講,功率開關的導通電阻與其寬長比成反比,但大尺寸器件會導致更大的芯片面積,增加芯片的成本,缺少市場的競爭力,怎樣能夠在減小導通電阻和芯片面積之間找到合適的折中點是功率晶體管設計的關鍵;其次,功率晶體管在版圖設計時的寄生效應也會影響轉換器的性能,功率晶體管的版圖優化是功率級設計的一個重要部分;最后,電流模轉換器需要對電感電流進行檢測,設計合適的低功耗電感電流檢測電路亦是功率級設計的難點。

基于上面的考慮,本文將以電流模式控制同步降壓型DC-DC轉換器為例,設計輸入電壓最大為18 V、典型輸出電壓為5 V、能夠提供3 A負載電流的功率級。

1 同步功率晶體管設計

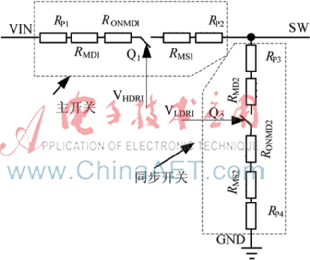

對于單片高壓大電流集成DC-DC轉換器,功率級設計極具挑戰性,特別是高壓功率開關采用LDMOS晶體管,在大電流下需要考慮以下幾個方面: DMOS晶體管會寄生雙極性晶體管,當晶體管流過一定的電流,晶體管的漏極和源極電壓會增加到擊穿電壓,然后漏源電壓將回跳到一定的低值[3-4];其次,在負載電流比較大時,芯片封裝時引線產生的寄生電阻[5]將不能忽略不計,如圖2所示,RP1~RP4為芯片封裝引線產生的寄生電阻,為了能夠減小其寄生電阻,在芯片封裝時,PAD與封裝管腳之間引線要避免過長;圖2中,RONMD1為主功率開關導通電阻,RONMD2為同步開關的導通電阻; Q1和Q2是由驅動電路控制的理想開關。

主開關的等效直流導通電阻RHS如下式所示:

RHS=RP1+RMD1+RONMD1+RMS1+RP2(1)

其中:RMD1和RMS1分別為主開關功率晶體管版圖設計時漏極和源極金屬連線產生的寄生電阻,該電阻主要由金屬連線的物理設計決定。

同步開關的等效直流導通電阻RLS如下式所示:

RLS=RP3+RMD2+RONMD2+RMS2+RP4(2)

其中:RMD2和RMS2分別為同步開關功率晶體管版圖設計時漏極和源極金屬連線產生的寄生電阻,該電阻主要由晶體管的物理設計決定。

主功率開關和同步開關晶體管一般選用N溝道LDMOS晶體管,原因在于N溝道LDMOS晶體管的電子遷移率大于P溝道LDMOS晶體管空穴遷移率,對于相同大小的導通電阻,LDNMOS晶體管的面積僅為LDPMOS晶體管面積的1/2~1/3[3],本文設計主開關和同步開關等效直流導通電阻RHS和RLS約為88 m?贅。

2 電感電流檢測電路

電流模式DC-DC轉換器中,電感電流的檢測是智能功率芯片非常重要的功能之一,因此也衍生了多種電感電流檢測的方式[6]。

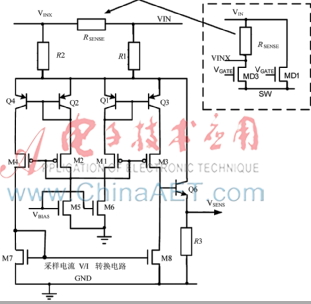

本文對電感電流檢測的方式采用間接檢測方式,圖3給出電路結構,當主開關功率(MD1)晶體管導通時,MD1的漏極電流等于電感流過的電流,為了避免直接檢測MD1電流會導致消耗更大的功耗,不利于系統的效率提高,本設計采用等比例檢測主開關MD1的漏極電流,然后通過在比例晶體管MD2的漏極連接一個較小的電阻將比例電流轉換成電壓VSENS,這樣的優點在于:采樣電流的功耗較低,由于采樣電阻連接在晶體管的漏極,電流的比例系數精確。下面給出VSENS的計算公式:

![D36NGQ]I$O4[1330H)CN]9N.png D36NGQ]I$O4[1330H)CN]9N.png](http://files.chinaaet.com/images/2015/06/02/6356887264579500002583135.png)

其中,M為功率晶體管電流采樣比例系數,在本設計中,檢測電感電流技術如圖1所示,MD1的寬長比是MD3的寬長比的49倍,即M=49。由RSENSE=2 ?贅電阻把采樣的電流轉換成電壓,并通過圖3所示的電路把該采樣的電壓進行放大,該放大系數設計為R3/R1,2=5倍。

3 同步功率晶體管驅動電路設計

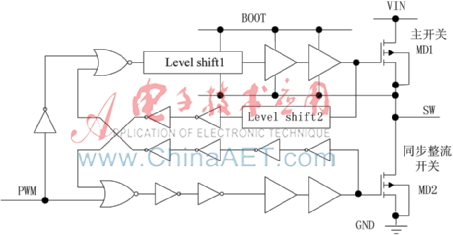

在降壓型DC-DC轉換器中,主開關晶體管使用N溝道LDMOS晶體管,為了能夠驅動該功率開關晶體管,需要集成片上自舉電路才能驅動LDNMOS功率晶體管。

由于轉換器采用同步工作模式,主開關和同步整流開關交替導通,為避免主開關和整流開關同時導通可能造成的功率晶體管的損壞,以及損失轉換器的效率,同步驅動電路還需要采用死區時間控制邏輯電路,詳細電路圖如圖4所示。當同步整流開關關閉時,同步整流開關管的寄生二極管導通,但死區時間不能太大,否則會導致由于寄生二極管導通時間過長,造成轉換效率降低。

功率級的輸入電源電壓范圍為5~18 V,功率開關晶體管的柵源電壓為5 V。由于信號PWM為0~VDD(低電平為0 V,高電平為5 V)的脈沖寬度調制信號,為了對主開關MD1的驅動,脈沖寬度調制信號的電平需要轉換為SW~VBOOT;為了能夠把0~VDD電平轉換成低電平為SW,高電平為VBOOT,必須使用電平移位器(圖4中level shift1);為了能夠實現死區時間的控制,還需要把SW~VBOOT轉換為0~5 V電平,使用圖4中level shift2。另外,功率器件LDNMOS有比較大的柵電容,因此, LDNMOS前級反相器采用反相器鏈進行驅動。

4 轉換器功率級版圖設計考慮

由于降壓型DC-DC轉換器的主開關MD1位于電源和輸出之間,故MD1的背柵與源極相連,而不與襯底電位相連,因此,在版圖設計時,該LDNMOS背柵下面需要N型埋層(NBL)作為隔離。功率晶體管的版圖設計還需要考慮以下幾個方面:

首先,確定功率晶體管面積,根據前面轉換器負載電流對功率晶體管的需求,采用SMIC 0.35 ?滋m DPTM BCDMOS工藝技術,其LDNMOS的導通電阻每平方毫米為16.5 m?贅(常溫25 ℃),本文設計的功率晶體管的面積:MD1為0.5 mm2,MD2為0.5 mm2。

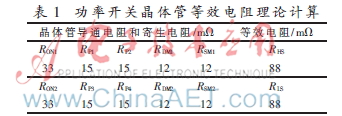

其次,盡可能減小功率晶體管的金屬連線和封裝引線所產生的寄生電阻,下面分別考慮如下:根據所選用的工藝,采用頂層加厚鋁線來減小金屬連線寄生電阻,同時對頂層金屬精心布線來優化功率晶體管的寄生電阻;一般來講,對于設計負載電流大于1 A以上的DC-DC轉換器,PAD與封裝管腳一般采用多根金絲,設計經驗1根金絲(1密爾直徑)能夠承受約1 A電流,不同金絲直徑其電阻亦不一樣,特別是設計負載電流大于2 A以上的轉換器,由于導通電阻很小,引線寄生電阻在式(1)、(2)中占有的分量不能忽略不計,本設計采用4根1密爾金絲作為封裝引線。當前,封裝引線采用銅線技術趨于成熟,而銅線的電阻率比金線電阻率小,而且還有價格優勢,因此采用銅線封裝越來越受歡迎。本設計采用上述設計思想,計算得到的功率管的理論值如表1所示。

最后,對主開關和同步開關需要良好的隔離,避免互相干擾;在芯片版圖中,功率器件和模擬電路需要隔離環,衰減開關噪聲對內部模擬電路的影響。

5 功率級測試結果

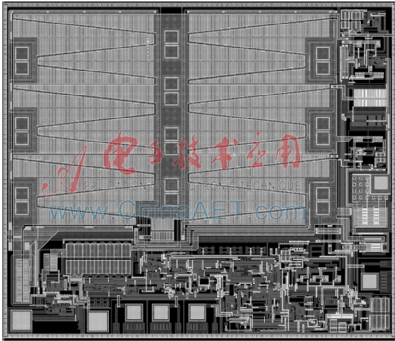

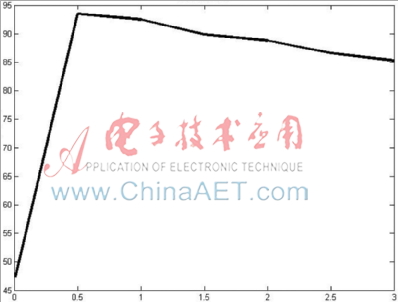

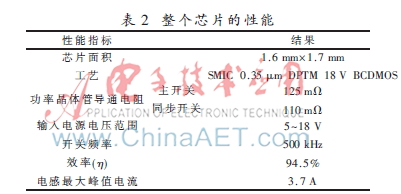

對前面所述功率級設計,應用到電流模降壓型DC-DC轉換器,采用SMIC 0.35 m DPTM BCD工藝流片,芯片面積為1.6 mm×1.7 mm,電流模降壓型DC-DC版圖結構如圖5所示。通過對芯片進行電氣測試,測試條件:外接電感4.7 ?H,輸出電容采用22 ?滋F陶瓷電容,輸入電源電壓為12 V,轉換器開關頻率為500 kHz,輸出電壓設置為5.0 V,輸出能夠提供3 A負載電流;圖6給出了輸出為5.0 V,在輸入電源電壓為12 V,不同負載條件下的效率曲線;表2給出功率級測試的結果,測試結果發現,功率開關導通電阻均大于表1的理論設計值,原因在于:表1給出的導通電阻為常溫計算值,而實際測試時,由于在大電流條件下,芯片溫度的上升導致導通電阻增加。

6 結論

本文采用0.35 m DPTM 18 V BCDMOS工藝技術設計電流模降壓型DC-DC轉換器功率級,該功率級設計包括功率晶體管設計,并給出了功率晶體管的等效導通電阻,電流檢測電路設計以及功率晶體管的驅動電路設計,最后給出了DC-DC轉換器功率級的版圖設計考慮。該功率級電路已經應用于DC-DC轉換器中,測試結果表明:在轉換器輸入電壓為12 V、輸出5.0 V時,輸出電流為3 A;其轉換效率最大可以達到94.5%。

參考文獻

[1] LEE C F,MOK P K T.A monolithic current-model cmos DC-DC converter with on chip current-sensing technique[J].IEEE Journal of Solid-State Circuits,2004,39(1):3-14.

[2] Deng Haifei.Monolithically integrated boost converter basedon 0.5 m cmos process[C].IEEE Int.Symp.On Power Semiconductor Devices & ICs,2004:169-172.

[3] MORROW P,GAALAAS E.A 20-W stereo class-D audiooutput power stage in 0.6 ?滋m BCDMOS technology[J].IEEE Journal of Solid-State Circuits,2004,39(11):1948-1958.

[4] HOWER P L.Safe operating area-a new frontier in LDMOSdesign[C].Proc.14th Int.Symposium on Power SemiconductorDevices and ICs,2002:1-8.

[5] BERKHOUT M.An integrated 200-W class-D audio ampli-fier[J].IEEE Journal of Solid-State Circuits,2003,38(7):1198-1206.

[6] FORGHANI-Z H P,RINCON-M G A.Current-sensing techniques for DC-DC converters[C].Proc.of IEEE MWS-CAS.2002:557-580.