文獻標識碼: A

文章編號: 0258-7998(2015)04-0053-03

0 引言

MEMS陀螺接口電路的數字集成化已經成為MEMS陀螺發展的一個最熱門的方向,所以高性能模數和數模轉換器對于數字陀螺接口電路的集成就變得格外重要[1]。如圖1所示,在一個數字陀螺的經典系統結構中,DAC擔負著將DSP處理后的數字信號轉換為模擬信號的作用,然后將模擬信號反饋給陀螺,從而實現閉環數字控制的功能,用來保證整個系統的穩定。相對于傳統的耐奎斯特數模轉換器而言,Sigma-Delta數模轉換器能夠實現更高的精度,這對于提升MEMS數字陀螺系統的整體性能而言具有非常重要的現實意義[2]。此外,針對于多位量化數字調制器的內部DAC不匹配導致的非線性問題,對DWA模塊進行了改良設計,并且通過FPGA驗證,得到了預期的結果。

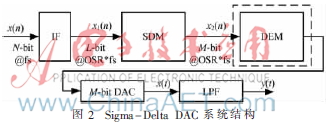

1 Σ-ΔDAC結構

一個典型的Σ-Δ DAC的系統結構如圖2所示。輸入數字信號x(n)是經過耐奎斯特頻率fs采樣得到的。數字插值濾波器的主要功能是對數字信號進行二次采樣,從而提高數字信號的采樣頻率,x1(n)的位數L大于或等于x(n)的位數N。信號x1(n)通過Sigma-Delta數字調制器進行量化來降低輸出精度,并抑制量化噪聲。當輸出的位數M>1時,內部M位DAC由于器件之間存在失配誤差,會產生非線性問題[3]。因此需要采用動態單元匹配技術(DEM)減小內部M位DAC的非線性[5-7]。

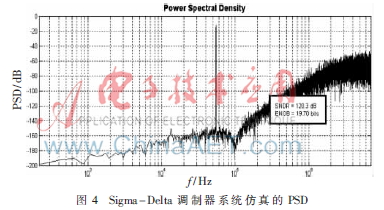

綜合分析各個結構的優缺點,折中考慮后,本文中的Σ-Δ數字調制器最終采用了三階四比特量化的單環前饋結構(CIFF)。圖3為NTF經過零點優化后的最終結構,經過零點優化的結構其量化噪聲能夠顯著降低,并且穩定性也得到顯著提高。圖4為系統結構的仿真結果。當輸入信號為頻率為50 kHz、歸一化信號幅度為0.5的正弦波,系統的采樣頻率為12.8 MHz時,得到輸出功率譜密度(PSD)。在100 kHz的信號帶寬內,系統的SNDR能夠達到120.3 dB,有效位數達到19.7位,滿足數字陀螺的性能要求。

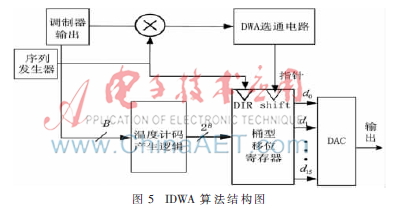

2 改進型DWA

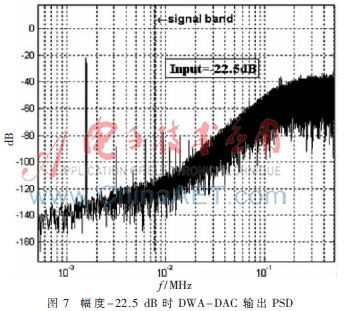

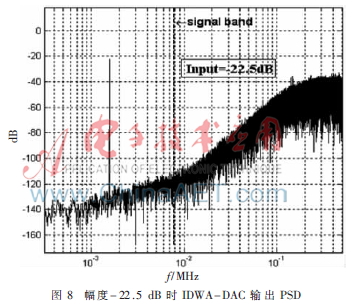

動態元單元匹配技術(DEM)是一種對D/A轉換器中溫度計碼線性化處理的方法,而數據加權平均(DWA)由于具有整形效果明顯、硬件實現簡單、節省硬件開銷等特點而最為常見。向調制器輸入小幅度的信號時,數字調制器的輸出代碼值將大部分集中在中間值及其附近,這相當于連續向內部DAC輸入固定直流值。因此,動態匹配單元的誤差將會周期化,即在基帶內產生噪聲。本文使用的改進的DWA(IDWA)的基本思想是通過增加單元DAC的數量[8],使得單元DAC的數量大于調制器的量化等級,以此來解決上述問題。圖5是IDWA的算法結構圖。圖6 是IDWA中的單元選擇邏輯(ESL)模塊框圖。IDWA與傳統DWA模塊相比還具有一些優點。首先IDWA系統反饋回路中的輸入以及求和端均可以使用B位有符號信號,而不必為DWA中的B+1和B+2位有符號信號;其次是在DWA系統反饋回路的反饋信號中,不必使用求余算法,降低了系統結構的復雜性。在Matlab中建立DWA-DAC和IDWA-DAC系統,進行仿真對比。當向兩種系統輸入幅度為-2.5 dB、頻率為20 kHz的信號時,都能完成失配誤差整形,產生的雜波被整形到高頻處。但如果幅度降低到-22.5 dB時,情況會變得不同。圖7和圖8分別是輸入幅度-22.5 dB時的DWA-DAC輸出功率譜和IDWA-DAC輸出功率譜。由圖中可以看出DWA-DAC輸出功率譜信號帶寬內出現了寄生雜波,產生的失真將會降低調制器的動態范圍,而相同條件下的IDWA-DAC仍然能夠很好地完成失配誤差整形,保證了帶寬內的信號精度。因此通過對比可以發現,當向數字調制器輸入小幅度信號時,相比于典型的DWA算法,IDWA算法能夠有效提高調制器的動態范圍。

3 仿真結果

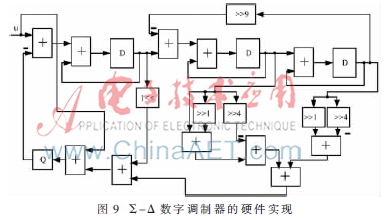

本文中Sigma-Delta數字調制器的硬件實現如圖9所示,其中的各個參數都采用了CSD編碼優化,可以大幅度地減少硬件的消耗。

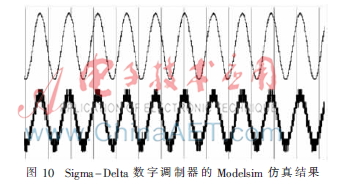

對調制器進行Verilog代碼實現,整個系統在modelsim下的仿真結果如圖10所示。從波形上可以看到,此結構實現了多位量化Σ-Δ數字調制器的功能。

4 FPGA驗證結果

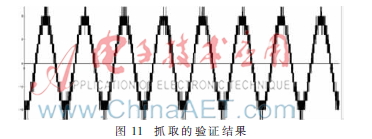

最后利用FPGA進行Σ-Δ數字調制器的綜合和驗證,本文使用的FPGA芯片是Xilinx公司Spartan3E系列XC3S500E產品。經過綜合后輸入頻率50 kHz的正弦波,采樣率為12.8 MHz,經過FPGA處理之后,圖11為利用Chip Scope Pro抓取的波形。將Σ-Δ數字調制器輸出數據從FPGA中導出,對導出的數據進行FFT運算,二次諧波小于-140 dB,三次諧波小于-135 dB,最大信噪失真比能達到120 dB,有效位數能達到19位以上,滿足設計要求。

5 結束語

本文設計了一款三階四位量化的Σ-Δ數字調制器,并且對DWA結構進行了算法改進。最后利用FPGA驗證了設計的正確性,達到了設計要求,實現了預期的設計目標。

參考文獻

[1] LIN L,LIU D,CUI J,et al.Digital closed-loop controller design of a micromachined gyroscope based on auto frequency swept[C].IEEE International Conference on NEMS,2011(6):654-657.

[2] GE F,LIU D,LIN L,et al.Fast self-resonant startup pro-cedure for digital MEMS gyroscope system[C].The 7th IEEEInternational Conference on NEMS,March 2012:669-672.

[3] RODJEGARD H.A digitally controlled MEMS gyroscope with 3.2 deg/hr Stability[C].Digest of Technical Papers.IEEE Transducers’05,The 13th International Conference on Solid-State Sensors,Actuators and Microsystems,June 2005(1):535-538.

[4] Li Bingxin.Design of multi-bit sigma-delta modulators for digital wireless communications[D].PhD dissertation,Royal Institute of Technology,2003:40-45.

[5] WELZ J,GALTON I.Necessary and suffcient conditions for mismatch shaping in a general class of multibit DACs[J].IEEE Trans.CircuitsSyst.II,Analog Digit.Signal Process.,2002,49(12):748-759.

[6] Sun Nan.High-order mismatch-shaped segmented multibit Σ-Δ DACs with arbitrary unit weights[J].IEEE Transac- tions on Circuits and Systems I,Feb.2012,59(2):295-304.

[7] GALTON I.Why dynamic-element-matching DACs work[J].IEEE Transactions on Circuits and Systems II,2010,57(2):69-74.

[8] VADIPOUR M.Techniques for preventing tonal behavior of data weighted averaging algorithm in sigma delta modulator[J].IEEE,Circuits and Systems II,2000,47(11):1137-1144.