文獻標識碼: A

文章編號: 0258-7998(2015)02-0065-03

0 引言

隨著圖像采集、傳輸和處理技術的發展,在很多領域中對圖像數據實時采集后的傳輸和處理提出了更高的要求,尤其是高分辨率、高頻幀相機的廣泛使用,對高帶寬的需求更加迫切,傳統的總線技術PCI、PCI-X、AGP等已很難勝任,而串行總線PCIe,由于利用時鐘恢復和高速差分信號克服傳統并行總線中的諸多限制,達到了更高的數據傳輸速率,因此一定程度上滿足了高數據帶寬的需求。PCIe總線使用數據包進行端到端的數據傳輸,理論上PCIe 1.0能達到2.5 Gbps/lane,2.0能達到5.0 Gbps/lane,但由于采用8b/10b編碼以及數據包頭和控制數據包的占用,有效數據速率會低于理論值的80%[1-2]。

利用PCIe總線的高帶寬優勢,設計了一種基于PCIe總線的多路實時傳輸系統,采用Bus Master DMA方式實現與PC之間的高速傳輸,以滿足多路圖像數據實時采集后傳輸和處理的高帶寬需求。

1 系統結構及工作原理

基于可編程邏輯器件FPGA的設計相比ASIC具有更好的靈活性和可配置性,因此本文所設計的基于PCIe總線的多路實時傳輸系統采用了Xilinx XC6VLX240T FPGA來實現。本系統主要包括PCI Express Core(EP)、DDR3 MIG模塊、PCIe Bus Master DMA(BMD)模塊以及DDR3讀寫控制模塊四部分,結構如圖1所示。

本系統的主要工作原理是由DDR3緩存相機采集PC處理后的圖像數據,通過PCIe總線實現與PC之間高速數據傳輸。兩路相機采集后的圖像數據經相機接口模塊前期處理后傳入DDR3讀寫控制模塊,由MIG模塊存入DDR3,然后DDR3中的數據被讀入發送緩存,同時PCIe BMD模塊發送MSI報文給PC使其配置BMD相應寄存器,BMD模塊會讀取發送緩存中的數據組成存儲器寫請求報文經PCIe總線傳給PC。對兩路圖像數據進行基于對象的特征提取后,PC配置BMD相應寄存器使其發送存儲器讀請求報文,然后PC端將處理后的圖像數據組成CPLD數據包發向PCIe EP Core,BMD模塊會將收到的CPLD TLP中的有效數據存入接收緩存,最后DDR3讀寫控制模塊讀取接收緩存中的數據,存入DDR3以待DVI 接口模塊讀取輸出顯示。結構圖中FIFO除了緩存的作用外主要是解決位寬及跨時鐘域的問題[3],而DMA FIFO接口模塊的作用主要是負責BMD模塊與FIFO間的信號連接及控制。

2 主要模塊設計

本系統的設計主要是DDR3讀寫控制模塊和PCIe BMD模塊的設計,而PCI Express Core(EP)和MIG可以通過Xilinx CORE Generator按需求的配置生成,其中PCIe配置成×4、gen2,利用Virtex6集成的PCIe IP實現,MIG配置成DDR3控制器、400 MHz。

2.1 DDR3讀寫控制模塊

DDR3讀寫控制模塊由讀寫控制模塊和仲裁模塊兩部分組成,如圖2所示。

讀寫控制模塊通過UI接口與MIG連接,按照MIG的時序要求進行讀寫操作。并且為了讀寫管理方便,將DDR3按容量劃分為兩份,分別用于存儲采集的兩路源圖像數據和經PC處理后用于輸出的圖像數據。

仲裁模塊主要負責多個設備訪問DDR3時的總線切換。由于本系統不同設備讀寫DDR3所用時間不同,為避免采用輪詢機制所帶來的帶寬利用率的降低,采取仲裁機制,負責對各個設備的訪問請求做出應答和總線的切換,效率更高[4],原理如圖2所示。設計時,為避免幾個設備同時請求帶來不確定性,仲裁模塊采用Round Robin仲裁模式,使得各設備能公平得到響應機會。綜合考慮帶寬利用率和實時性,將十行以內圖像像素點的讀寫時間作為時間寬度,保證本系統的高效可靠。

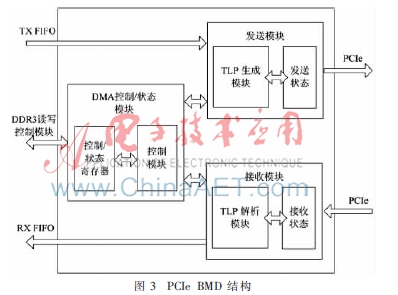

2.2 PCIe BMD模塊

PCIe BMD模塊主要由三部分構成,包括DMA 控制/狀態模塊、發送模塊以及接收模塊,結構如圖3所示。

2.2.1 DMA控制/狀態模塊

DMA控制/狀態模塊包括控制/狀態寄存器和控制模塊。控制/狀態寄存器主要寄存BMD模塊的控制及狀態信息。PC端采用數據包的形式將配置需求通過PCIe總線傳輸到EP端,BMD接收模塊識別配置數據包(有效數據大小為1DW的存儲器寫請求TLP),并根據TLP的地址段將數據寫入相應的控制寄存器。PC端也可以發送讀控制/狀態寄存器的請求,接收模塊識別到該類數據包(請求數據大小為1DW的存儲器讀請求TLP)后,產生CPLD請求,發送模塊將根據該TLP的地址讀取對應控制/狀態寄存器的值,生成CPLD TLP發向PC端。

控制模塊根據控制/狀態寄存器的配置值發送相應的控制信號給發送及接收模塊,還與DDR3讀寫控制模塊相連,控制原圖像數據的讀取和處理后圖像數據的寫入,并配合讀取操作發送MSI請求[5],使PC配置BMD模塊相應的控制寄存器以進行存儲器寫請求TLP的發送。

2.2.2 發送/接收模塊

發送模塊作為BMD模塊的發送部分,主要負責在接收模塊收到讀寫控制/狀態寄存器的請求后完成報文的發送,在發送模塊收到MSI請求后MSI TLP的發送,以及根據PC端所配置的寄存器參數進行存儲器讀/寫請求TLP的發送,其中存儲器寫請求TLP的有效數據來自TX FIFO。

接收模塊主要負責接收各種數據包并作出相應操作:當收到配置數據包時,將有效數據寫入對應控制寄存器;當收到讀控制/狀態寄存器的請求,通知發送模塊讀取對應控制/狀態寄存器值組成CPLD TLP發向PC端;當收到CPLD TLP,其中的數據段就是發送模塊發送的存儲器讀請求TLP所請求的數據,然后對這些數據進行校驗并讀入RX FIFO等待存入DDR3。

2.2.3 PCIe BMD全雙工模式

對于本系統與PC之間的數據傳輸,單一時間段內只進行讀或者寫比較簡單,但為了滿足系統需要以及傳輸效率的提高,大部分情況下,需要讀寫數據同時進行。對于發送模塊而言,則需要合理安排存儲器寫請求TLP和存儲器讀請求TLP的發送,這里采用動態加權循環調度算法(Dynamic Weighted Round Robin,DWRR)。普通的加權循環調度算法(Weighted Round Robin,WRR)是通過設置兩個計數器分別記錄當前寫請求和讀請求已經發送的個數,并根據傳輸特性給兩者配置相應的權重值。傳輸開始后,當某一請求次數達到它的權重值,則將該請求的計數器清零,再跳轉到另一請求,如此循環往復直到傳輸結束。由于讀請求的周期數要遠小于寫請求,如果讀寫請求的權值設置好后就保持不變,讀請求的過快發送會快速消耗PCIe EP CORE的發送緩存從而造成擁堵,使發送模塊長期處于等待狀態,降低傳輸速率。本系統根據這一特性對WRR算法進行了優化,開始階段由于發送緩存為空,為了充分利用總線,將讀請求權值設為發送緩存大小3/4,寫請求設為其1/4,優先發送讀請求,再發送寫請求,然后根據寫請求個數達到權值后發送緩存的可用數設置讀請求的權值,當發送緩存的可用數小于寫請求權值一半時,重新設讀寫請求權值都為1,使讀寫請求逐個間隔發送直到讀請求優先完成,再發送剩余的寫請求。在這過程中讀寫請求權重值根據發送緩存的可用數動態變化,調整讀寫請求的發送組合,在保證讀取速率的情況下盡量減少了擁堵時間,從而提高整體傳輸速率。

3 設計實現及測試驗證

本設計采用Xilinx XC6VLX240T FPGA定制開發板作為開發平臺,并結合對應的驅動程序和處理程序進行測試驗證。

3.1 設計實現

整個設計采用Xilinx ISE14.7作為FPGA的開發工具,利用Verilog HDL進行程序設計。根據圖1的結構圖在頂層模塊中例化各個模塊,并進行相應的優化。為了滿足測試驗證的需求,頂層模塊中還需要例化ChipScope測試核。設計完成后,通過ISE綜合、映射、布局布線,最后生成可供下載的bit文件。綜合后整個設計占用Register資源9 317(3%),占用LUT資源11 214(7%),占用Bram資源12(2%)。

3.2 測試驗證

將開發板與PC主板的PCIe插槽相連接,下載bit文件,結合ChipScope軟件進行測試。兩路相機參數同為1 920×1 080,60 FPS,DVI顯示參數也為1 920×1 080,

60 FPS。DDR3 SDRAM時鐘400 MHz,物理位寬64 bit,讀寫控制時鐘200 MHz,數據位寬256 bit。PCIe配置成×4,gen2。理論上,DDR3的讀寫速率和PCIe的傳輸速率滿足多路圖像的采集和輸出要求。根據仲裁模塊的設計,測試時間寬度分別為1、2、4、8行圖像像素點讀寫時間下的性能,其中7.5 KB對應一行圖像像素點的數據量。PCIe BMD單工情況下的測試結果如表1所示,并將表1的測試結果換算為gen1×8模式,與文獻[6]的結果進行對比,如圖4所示。

對比測試結果,文獻[6]在gen1×8模式時的最高傳輸速率為寫1 311 MB/s,讀1 002 MB/s,而本傳輸系統在相同模式下能達到的最高傳輸速率為寫1 632 MB/s,讀1 557 MB/s,相比文獻[6]寫入速率提高24.5%,讀取速率提高55.4%,并且表現出傳輸數據量越大,傳輸速率越高,超過60 KB之后趨于穩定。如果PCIe BMD一直工作在單工模式,是不能滿足每秒寫入和讀取900 MB數據量的要求,因此本系統中PCIe BMD只在每幀圖像的開始和結束像素行傳輸時工作在單工模式,其余時間工作在全雙工模式。對于PCIe BMD的全雙工方式,發送模塊采用WRR算法和DWRR算法的測試結果如圖5所示。

對比該測試結果,可以看出對于不同數據量的傳輸,采用DWRR的傳輸速率都高于WRR,寫入速率最大提高3.4%,讀取速率最大提高9.6%,最高傳輸速率能達到寫1 478 MB/s,讀1 438 MB/s,保證了圖像數據傳輸到PC后有充足的時間進行運算處理,滿足本系統的傳輸需求。根據PCIe BMD單雙工測試結果,綜合考慮整個系統的傳輸效率、總線切換頻率及實時性,傳輸系統仲裁模塊中的時間寬度設為4行圖像像素點的讀寫時間為佳。

4 結論

大數據量采集后的高速傳輸對于一個采集系統而言至關重要,高性能的傳輸系統能為大數據量的存儲、處理等后期各種操作提供保障。本文設計了一種基于PCIe總線的多路實時傳輸處理系統,并且通過FPGA驗證了該系統的可行性。實際測試表明該系統能達到單工寫1 632 MB/s、讀1 557 MB/s和全雙工寫1 478 MB/s、讀1 438 MB/s的傳輸速率,完全滿足本系統高速數據傳輸的需求,并且對于其他高速傳輸系統的設計有一定的借鑒作用。

參考文獻

[1] PCI express base specification revision 2.1[S].PCI-SIG.,Mar 4,2009.

[2] KAVIANIPOUR H,BOHM C.High performance FPGA-basedscatter/gather DMA interface for PCIe[C].IEEE NSS/MIC,2012,N19-3,1517-1520.

[3] LI H,LIU Y A,YUAN D M,et al.A wrapper of PCI express with FIFO interfaces based on FPGA[C].IEEE ICICEE,2012,145,525-529.

[4] 樊博,王延杰,孫宏海,等.FPGA實現高速實時多端口圖像處理系統的研究[J].液晶與顯示,2013,28(4):620-625.

[5] 雷雨,任國強,孫健,等.基于PCIE的高速光纖圖像實時采集系統設計[J].電子技術應用,2013,39(10):136-138.

[6] 侯杭呈,王憶文,李輝.一種基于PCI Express總線的DMA高速傳輸系統[J].微電子學,2013,43(3):383-386.