文獻標識碼: A

文章編號: 0258-7998(2014)11-0043-04

0 引言

傳統的視頻采集系統僅支持PAL和NTSC幾種制式的視頻數據,這些模式很難清晰地抓拍到目標快速變化的瞬時圖片,而很多高幀頻的攝像頭只是對圖像進行了簡單的采集,并未處理和壓縮。為了改善視頻圖像數據的信道傳輸和存儲速度,降低對信道寬度以及存儲空間大小的要求,本文設計了一種多接口、高速率傳輸的圖像壓縮系統。該系統不直接存儲圖像數據,而是由FPGA采集數字化后的視頻圖像數據,通過DSP將采集的數據進行編碼壓縮,然后再將編碼壓縮后的數據通過PCI高速傳輸給計算機,最后再通過計算機對圖像進行解壓縮并顯示。

1 總體結構設計

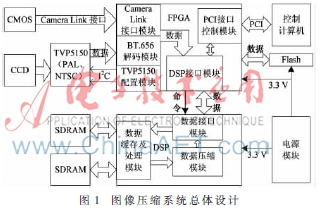

本設計結合FPGA處理速度快、DSP運算能力強等優點,提出了如下方案:通過FPGA模擬I2C總線時序,對模擬視頻采集芯片TVP5150進行配置,并接收TVP5150輸出的ITU-R BT.656格式的圖像數據;同時,采用了Camera Link 接口,接收標準數字相機輸出的圖像數據。在FPGA完成對視頻數據的采集并經內部FIFO緩存后,將數據打包并行傳輸給DSP,DSP對圖像進行JPEG2000標準的壓縮,壓縮幀頻不低于60幀/s,壓縮比不小于20:1;壓縮后的數據通過PCI總線傳輸給控制計算機,然后通過計算機對圖像進行解碼顯示。

圖像壓縮系統的整體結構如圖1所示,主要包括圖像采集模塊、FPGA控制模塊、DSP壓縮模塊、PCI接口模塊、電源和時鐘管理模塊。

視頻采集模塊使用了型號為PNT-698的CCD模擬攝像頭,該攝像頭幀頻為25 Hz,場頻為50 Hz,像素為720×576,輸出為PAL制式圖像信號,信噪比大于48 dB,并可以實現自動增益控制以及自動白平衡調整,輸出接口標準為BNC。

2 硬件平臺的搭建

2.1 視頻接口協議設定

視頻接口由8路并行數據和1路時鐘信號組成,時鐘為像素時鐘,時鐘周期T=1/1 728fN,fN為行頻率,單位是Hz,fN=1/625(一幀圖像為625行),脈沖寬度t=18.5±3 ns,數據保持時間為td=18.5±3 ns。

視頻傳輸協議是以幀為單位傳輸,一幀圖像的傳輸格式如圖2所示。為了與標準電視圖像掃描方式相兼容,采用隔行掃描,每幀625行,每行1 728 B。其中第1行~第23行和第311行~第336行為場消隱信號,主要針對視頻數據場結束后掃描位置的重新定位,偶數場共288行(23~311),奇數場共288行(336~624)。

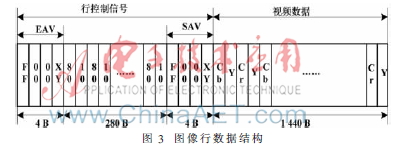

圖像解碼芯片TVP5150采用了同步信號嵌入數據內部的輸出方式,所以需要對行數據結構進行研究。行數據結構如圖3所示,一行共1 728 B,前288 B為行控制信號,后1 440 B為圖像數據。行控制信號包括行開始標志SAV(Start of Active Video),長度為4 B;行結束標志EAV(End of Active Video),長度為4 B;行消隱信號280 B。SAV信號和EAV信號都由4 B組成,分別為FF、00、00、XY,前3 B為固定數,最后1 B XY表示該行數據在整幀圖像中的位置信息。XY字節包含奇偶場標志、行消隱狀態信息、場消隱狀態信息。

視頻圖像數據為YCbCr 4:2:2格式,Y表示一個像素的亮度,Cb、Cr表示一個像素的色差信號,一個像素2 B,每行共720個像素,共1 440 B。視頻數據格式為CbYCrYCbYCrY……CrY,因此可以理解為每個像素均有各自的亮度信號Y,但是共用一組色差信號Cb和Cr。在解包數據時,需要將它們分開,若需要顯示,可以將YUV格式轉換為RGB格式。

2.2 FPGA與DSP接口設計

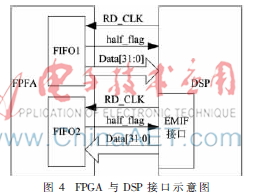

FPGA完成圖像數據的接收后,經過格式變換及濾波將圖像數據傳輸給DSP進行壓縮。壓縮打包完成后,又需要將數據回傳給FPGA,通過FPGA控制PCI接口時序,將數據最終上傳給計算機。為了滿足圖像數據高速、雙向、實時的傳輸,在DSP與FPGA之間設計了兩個高速的FIFO緩沖。

本系統中選用Spartan3系列的XC3S1400AN作為核心處理器[1],其內部儲存資源豐富,內部Flash 16 Mbit, Distributed RAM(分布式RAM)176 Kbit,Block RAM(塊RAM)576 Kbit。為了節約成本,同時考慮到系統的傳輸速率及可靠性,在FPGA內部IP核中創建了內部FIFO,數據寬度為32 bit,存儲容量為3 M×32 bit。采用了獨立的讀時鐘(RD_CLK)和寫時鐘(WR_CLK),數據達到半滿,半滿標志位置1(half_flag=′1′);達到滿,滿標志置1(full_flag=′1′)。

FPGA和DSP的接口如圖4所示,視頻數據采集、處理完成之后,FPGA通過FIFO的滿標志查看FIFO是否已滿,如果未滿,則將32 bit圖像數據在寫時鐘的邏輯控制下寫入到FIFO;將半滿信號連接到DSP的中斷引腳,半滿信號置高,會觸發DSP的DMA進程,將FIFO中的圖像數據讀走[2]。同理,DSP通過EMIF外設接口將FPGA作為其外部存儲空間,壓縮后的數據通過DMA寫到FPGA內部的另一個FIFO,半滿信號觸發FPGA內部讀數進程,將數據讀走,通過PCI總線上傳到控制計算機。

2.3 DSP壓縮模塊設計

JPEG2000壓縮算法硬件實現復雜度比較高,其核心算法離散小波變換和EBCOT算法計算量特別大[3],同時要考慮到實時性要求,所以對CPU的處理速度以及緩存空間等要求很高。因此在本次設計中,選擇了TI公司C6000系列DSP中的TMS320DM642作為硬件平臺。該DSP計算速度超過每秒64億次,適合大數據吞吐量高速運算,比如在圖像處理領域。同時,DM642擁有豐富的外設接口,包括可實現與SDRAM、Flash等外部存儲芯片無縫數據連接的EMIF接口等,非常適合音視頻解碼、數字監控以及數字視頻服務等應用[4]。

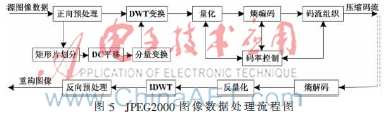

對圖像數據處理流程如圖5所示,源圖像先經過正向預處理后進行離散小波變換(DWT),然后對變換的小波系數進行量化處理和熵編碼,最后將熵編碼后獲得的圖像數據打包成壓縮數據包輸出。解碼則按照壓縮碼流中提供的各個參數將編碼過程進行逆向操作,最終將源圖像重構還原出來。

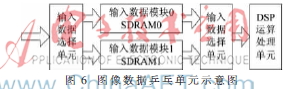

2.4 乒乓緩存設計

圖像傳感器單位時間內產生的數據是連續的,且數據量比較大,而DSP的編碼速率是變化的。為了防止在編碼過程中造成數據的丟失,需要在采集與編碼電路之間設計一組幀緩存電路。

常用的緩存電路主要有FIFO、雙端口RAM和乒乓緩存結構[5]。由于FIFO的存儲容量太小,不適合圖像視頻數據的大吞吐量緩存。雙端口RAM配備必須進行訪問仲裁控制,設計較復雜。乒乓緩存結構克服了它們所有的缺點,輸入的視頻數據流以幀為單位交替地寫入兩個不同的SDRAM存儲單元,在寫入其中一塊SDRAM的同時,將另一塊SDRAM中的數據讀出,并送到數據編碼單元進行運算。這樣數據的輸入/輸出都是不間斷的,非常適合流水線式操作,完成數據的無縫緩存和處理。

本設計中乒乓緩存結構如圖6所示,DSP接收到FPGA傳輸的圖像數據后,以幀為單位交替寫入兩塊SDRAM存儲器。與此同時,數據被交替讀出,輸出給數據壓縮單元進行編碼。數據流被嚴格有效地控制,不會出現丟數據或者誤碼,而且效率很高。選用MT48LC2M-

32B2作為外部高度SDRAM緩存器,讀寫速率可以達到6 ns,數據總線寬度為32 bit,容量為64 Mbit,而高頻數字攝像頭輸入的一幀圖像的大小為600×480×3=864 Kbit,完全可以滿足要求。

3 邏輯功能的實現

3.1 TVP5150解碼邏輯

TVP5150解碼芯片輸出的數據流中除了包含有效的視頻圖像數據之外,還包含行、場同步信號以及一些消隱數據。所以在視頻解碼時,需要根據同步信號以及ITU-R BT.656的標準格式將有效數據提取出來。

提取有效數據的流程圖如圖7所示,在時鐘的上升沿對TVP5150輸出的數據進行采樣,若連續出現“FF”、“00”、“00” 3個固定字節,則表明出現了定時基準;如果第4 B出現“80”,表示一場數據的開始,而且為偶場,接著讀取1 440 B圖像數據。同理,若第4 B出現“C7”,表示奇數場數據的開始,接著同樣讀取1 440 B有效圖像數據;否則,繼續等待定時基準的出現。

3.2 DSP編碼邏輯

DSP對圖像數據的編碼流程如圖8所示,上電復位后,DSP程序從Flash起始處加載并啟動,通過二次引導,最終將應用程序全部搬移到DSP內存中,然后跳轉到入口函數c_int00(),完成初始化配置,并等待FPGA的外部中斷觸發信號。FPGA采集到數據后,緩存到接口FIFO中,并以中斷的方式觸發DSP的DMA進程,DSP以DMA的方式將數據存儲到SDRAM中,若一幀圖像傳輸完畢,則觸發軟中斷,進入JPEG2000編碼子程序。編碼完成后,再次觸發DMA進程,將數據回傳給FPGA。 3.3 PCI傳輸接口邏輯

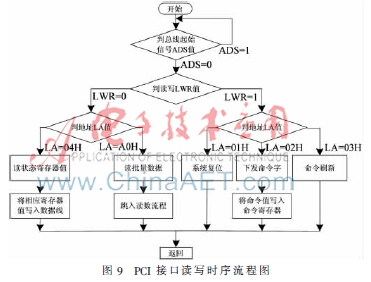

PCI接口主要用來下發上位機控制命令和系統參數,上傳編碼后的圖像數據。采用PCI9054芯片來連接本地總線和PCI總線,PCI總線協議由PCI9054芯片內部處理,只需對其進行配置,并完成硬件接口驅動程序即可,PCI9054工作在C模式,內部采用了DMA數據傳輸方式[6]。

PCI接口內部邏輯流程圖如圖9所示,先判斷總線啟動信號ADS,若該引腳電平由高變低,則啟動一次數據傳輸過程,然后判斷讀寫信號電平LWR,若LWR為1,表示PCI寫過程,否則為讀過程。PCI讀過程又分為讀狀態和讀數據,通過地址總線LA來判斷,讀過程中,若LA=04H,則為讀寄存器狀態;若LA=A0H,則為讀批量圖像數據。而寫過程中,若LA=01H,則為系統復位,立即執行,不寫入寄存器;若LA=02H,則為命令下發,需要將命令字寫入相應寄存器;若LA=03H,則為命令刷新,立即執行,不寫入寄存器。

為了使得數據不丟失,在PCI接口設計過程中調用FPGA的IP核添加了FIFO數據緩存器,位寬為32 bit,與PCI總線位寬相匹配,深度為4 KB。由于PCI數據總線是雙向傳輸,所以在FPGA內部增添了數據方向控制模塊,保證了數據有序地下發和上傳。

4 結果分析

為了比較壓縮前后圖像的質量,首先將未壓縮的圖片通過PCI接口傳輸給上位機并顯示,如圖10(a)所示,圖像大小為407 KB,格式為BMP。然后保持源圖片不變,將采集到的圖像數據傳輸給DSP編碼,編碼后傳輸給上位機,經上位機解碼后得到的圖片如圖10(b)所示,其大小為59.5 KB,壓縮比約為10:1;圖10(c)大小為15.2 KB,壓縮比約為26:1。同時,圖像數據通過PCI卡傳輸給上位機時最高速率達到了38 MB/s。

通過對比可知,壓縮比越高,峰值信噪比越低,主觀視覺的質量也會有所下降,局部細節有些模糊。總體來說,本次設計的新型圖像壓縮編碼系統實現了預計的功能。

參考文獻

[1] 邸麗霞.基于FPGA的高速圖像數據采集存儲系統設計[J].電視技術,2013,37(13):49-52.

[2] 李娟.基于FPGA的圖像預處理及顯示系統的設計[D].中國科學院研究生院,2011.

[3] 張曉娣,劉貴忠,曾召華,等.JPEG2000圖像壓縮編碼系統及其關鍵技術[J].電視技術,2001(8):13-17.

[4] 鄭紅,劉振強,李振.嵌入式DSP應用系統設計及實例剖析[M].北京:北京航空航天大學出版社,2012.

[5] 周如輝.實時視頻處理系統中乒乓緩存控制器的設計[J].電子元器件應用,2006(4):66-68.

[6] 原學山.基于PCI總線的圖像采集卡的設計與實現[D].成都:西南交通大學,2006.