文獻標識碼: A

文章編號: 0258-7998(2014)11-0075-03

0 引言

隨著數據存儲設備被廣泛應用于航空航天系統、醫療衛生、工業自動化等各行各業,對于圖像設備采集的控制及實時大容量高速存儲要求也越來越高。本文以Micron Flash為存儲介質,通過FPGA控制實現Camera Link高速接口通信,傳輸速率可達到100 MB/s,并設計高速數據的流水線式存儲方式,實現大容量高速圖像存儲與實時顯示。

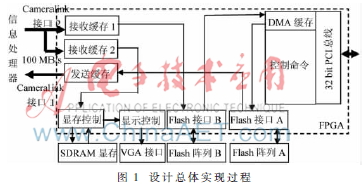

1 總體設計

設計的實現過程如圖1所示,上位機通過PCI總線下發圖像數據并將數據保存在Flash存儲陣列A中;上位機指令下發后,FPGA控制Flash A讀出存儲的數據并通過CameraLink1輸出接口發送至信息處理器;待信息處理器處理完數據,再通過CameraLink輸入接口2將數據寫入到SDRAM顯存和Flash存儲陣列B中,使能VGA顯示后,顯示控制循環讀取SDRAM中的圖像數據進行顯示;最后,上位機通過DMA傳輸將Flash陣列B中保存的數據快速上傳至上位機中以作后續處理。

2 高速數據存儲管理設計

2.1 Nand Flash

高速存儲陣列A/B單元的設計是分別以4片Micron Nand Flash芯片作為存儲介質,通過FPGA完成Flash芯片讀寫時序的控制[1]。Micron Flash MT29F128G08AJAAA內部含有兩個CE使能端,每個使能各控制兩個相互獨立的LUN(4 GB),總容量為16 GB。為便于地址管理,提高數據處理速率,單片MT29F128G08AJAAA內部塊操作順序為(CE1)LUN0、(CE1)LUN1、(CE2)LUN0、(CE2)LUN1,當無效塊檢測模塊檢測到壞塊時,當前每行4塊均認為是無效塊,不對其進行操作。

由于Flash芯片每次頁編程都需要350 s~560 s的頁編程時間,在此期間,不能對當前模塊進行操作,這嚴重制約著持續的數據寫入。由此可充分利用每個LUN相互獨立操作、互不影響的特點,采用流水線操作方式來復用編程時間,即當前LUN進入頁編程操作時,可以對剩下的3個LUN進行寫入頁寄存器操作,從而提高數據吞吐量[2]。假設Flash的讀寫周期為20 ns,將數據寫入到頁寄存器所需的時間為:8 192×20 ns=163.84 s,考慮端口復用寫入的地址、命令等時間約為10 s,因此對于單片Flash而言,連續寫完4個LUN共需時間為:4×(163.84+10) s=695.36 s,完成一次32 KB數據寫入所需總時間最多為695.36 s+560 s=1 255.36 ,即可粗略計算出單片Flash的平均寫入速率:32 KB/(1 024×1 255.36 s)=24.9 MB/s。該情況未考慮到第4個LUN寫完后,LUN1已經完成了頁編程操作,可繼續寫入,也就是說其持續的寫入速度大于24.9 MB/s。

2.2 高速數據的存儲

存儲器存儲的數據來源可分為兩類:一類是Camera-

Link2接口輸入的高速圖像數據,另一類是上位機通過PCI總線下發的圖像數據。兩類數據的存儲方式相同,PCI下發數據速率小于CameraLink2接口輸入的圖像數據速率,時序上只需要保證CameraLink2輸入的數據能寫入到Flash B即可滿足需求。

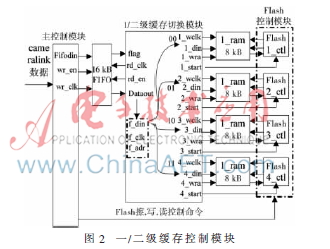

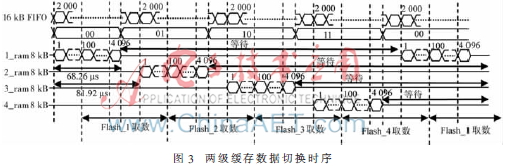

FPGA內部采用兩級緩存結構,通過流水線的操作方式實現100 MB/s 圖像數據的可靠存儲[3]。前一級采用一個16 KB大小FIFO構成的緩存,FIFO為16位,輸入時鐘為50 MHz;第二級緩存由4個8 KB的雙口RAM組成,輸入時鐘60 MHz,如圖2所示為緩存控制模塊圖。當一/二級緩存切換模塊通過flag標志判斷16 KB FIFO滿足已寫入2 000個字,f_adr地址開始累加并以60 MB/s速度從16 KB FIFO連續取出4 096個字,將數據賦給f_din,并模擬產生60 MHz的8 KB RAM寫時鐘f_clk。而每取完一次4 096個字數據量,f_fifo_adr清零,數據切換標志sw_flag自加1。數據流的方向就是通過sw_flag控制的,當sw_flag為00,01,10,11時,分別將f_din、f_clk、f_adr賦給1_ram 8 kB、2_ram 8 kB、3_ram 8 kB、4_ram 8 kB這4個ram二級緩存。當Flash控制模塊判斷取數標志1_start~4_start其中之一大于100時,主控制模塊控制對應的Flash進入寫操作。

由于一級緩存寫入速度50 MB/s,讀數速度60 MB/s,寫速度小于讀速度,不用當心溢出問題。考慮到取數據連續性,避免讀空現象出現,合理地選取取數判斷標志的大小是關鍵,而判斷標志的大小取決于連續取數的數量大小及寫/讀數速度。假設數據取空時經歷時間為t,取數判斷標志大小為flag,則由公式50t+flag-60t=0可知flag=10t。為滿足連續取出4 096個字,故t要大于4 096/60=68.26 s,即flag滿足大于682.6就可以避免取空現象,考慮留取一定的裕量,選取flag為2 000。同理,當flash1從ram8 kB取數時,由于取數速度50 MB/s小于寫數速度60 MB/s,有可能出現溢出現象,通過1_start標志判斷1_ram 8 kB滿足大于100,Flash1控制模塊連續從ram 8 kB中取走4 096字。為保證數據可靠高效的連續性傳輸,一/二級緩存數據切換的有序配合顯得尤為重要,如圖3所示為數據切換時序圖,從16 KB FIFO到ram數據傳輸過程為:當16 KB FIFO取數判斷標志大于2 000時,從16 KB FIFO以60 MB/s速度連續取出4 096數據存入1_ram 8 kB,需時68.26 s,ram平均取數速度取決于16 KB FIFO寫入速度(為50 MB/s,即81.92 s),在ram取數的過程中16 KB FIFO經過81.92 ?滋s之后已經再次寫入4 096個數據,16 KB FIFO剩余4 096+

2 000-4 096=2 000個數據量滿足取數要求,此時sw_flag自加1指向2_ram 8 kB,以此類推,4個ram循環地寫入數據。同理,在ram寫入數據的過程中,Flash1控制模塊判斷ram1取數標志滿足100時,連續取出4 096個字,當Flash1取走ram1中4 096個數據時,ram2已經滿足取數標志,Flash2開始從ram2中連續取出4 096個字,以此類推,Flash控制單元連續讀取4 096字寫入到Flash中進行頁編程操作,這樣就可實現連續的100 MB/s數據寫入。

2.3 圖像數據的發送

從PCI總線下發存入Flash A的圖像數據通過CameraLink1輸出接口發送至信息處理器,從Flash取數的過程和寫數的方式類似。設置4個8 KB的ram緩存,當接收到開始下發圖像指令后,FPGA控制4片Flash完成一次頁讀取操作,并將數據保存在8 KB緩存中,然后以60 MB/s的時鐘讀取緩存1中的數據存入16 KB FIFO。當讀完緩存1中的8 192 B數據后,依次讀取緩存2、3、4中保存的數據,同時以50 MB/s的時鐘讀取Flash中下一頁的數據。Flash以50 MB/s時鐘完成一次雙平面讀數過程所需時間為25 ns+8 192×20 ns+30×20 ns(命令、地址下發時間)=164 885 ns。以100 MB/s的速度讀取32 KB數據所需的時間為32×1 024×10 ns=327 680 ns>164 885 ns,也就是說在讀完剩下的3個緩存中的數據時候,第一個Flash已完成了一頁數據的讀取,并將數據存放在緩存1中。因此通過循環讀取4個緩存中的數據,即可實現持續的100 MB速度發送圖像數據。

3 圖像的實時顯示

3.1 VGA時序信號產生

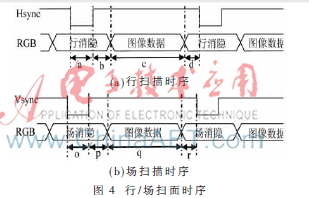

設計VGA圖像顯示控制需要注意時序的驅動,這是完成設計的關鍵,時序稍有偏差顯示必然不正常甚至會損壞顯示器[4]。如表1所示為1 280×1 024×60 Hz圖像顯示控制各階段時鐘點數,圖像時鐘頻率為108 MHz,其中Hsync信號用來控制“列填充”,可以分為a~d 4個階段,其中c段1 280點為有效顯示區,a段由112個點組成的同步信號負脈沖以及兩段行消隱期;Vsync信號用來控制“行掃描”,同樣也分為o~r 4個階段,其中q段1 024行為圖像顯示行,o段3個時鐘為場同步信號負脈沖以及兩段場消隱期[5-6]。

對于行同步信號,每行實際像素數為1 688,故行同步信號頻率為108 MHz/1 688=63.98 kHz,同理,場同步信號頻率為60.02 Hz[7]。如圖4所示為行/場掃描時序,結合圖4和表1,可以利用FPGA資源構建VGA時序。選取108 MHz的晶振作為脈沖計數器時鐘,當像素脈沖計數在小于112脈沖間,Hsync輸出低電平,其他時段輸出高電平。同時,當像素脈沖計數小于3時,Vsync輸出低電平,其他時段輸出高電平,對行場同步為低電平的標準,SYNC設計為Hsync和Vsync相與的結果,BLANK信號可做的比SYNC略寬一些。

3.2 顯示控制設計

如圖1所示,設計中采用高速SDRAM實現對圖像數據的高速緩存,從CameraLink接收的圖像數據分別存入兩個緩存,一個用于高速存儲于Flash B陣列中,另一個暫存在SDRAM中,用于實時顯示圖像。CameraLink接收的圖像數據以50 MHz×16 bit的速度存入FIFO1緩存中,當判斷FIFO1緩存數據量大于1 280個字時,FPGA控制SDRAM模塊以100 MHz×16 bit的速度從FIFO中取出數據存入SDRAM。當接收實時顯示圖像命令時,SDRAM以165 MB/s速度更新FIFO2中數據,VGA接口以108 MHz速度循環讀取SDRAM中所存儲的圖像數據,對顯示器的顯示內容進行更新。由于SDRAM寫入1 280個字所需時間為12.8 ?滋s,考慮到SDRAM讀寫操作分時進行,為保證SDRAM在寫數期間FIFO2數據不會被讀空,FIFO2每次讀取1 080字,所需時間20 s,滿足SDRAM讀寫轉換及刷新時間,同時VGA顯示能以108 MHz速度持續從緩存中讀取數據并顯示[8]。

4 測試結果與結論

試驗結果如圖5所示,采用圖像模擬器發送一幅1 280×1 024灰度圖像的方式對圖像存儲顯示的設計進行驗證,并通過DMA方式讀取存儲在Flash B陣列中的圖像數據至上位機中進行畫圖分析。試驗結果表明,高速圖像存儲卡能實時顯示圖像,且經過回讀數據分析,完整地保存下高速輸入的圖像數據。利用FPGA控制整個系統的工作時序,通過在內部設置多級緩存結構和流水線操作思想,實現了圖像數據在不同時鐘域之間的轉換,完成了高速圖像數據的存儲與實時顯示功能。本設計可實現持續的100 MB/s數據的實時存儲,滿足大多數光電設備中CameraLink數據的實時存儲要求。

參考文獻

[1] 楊柯,范海震.CameraLink接口的高速電子存儲系統設計[J].艦船電子工程,2012,32(5):110-118.

[2] 王熙.一個面向航空遙感高速的閃存存儲系統設計[D].合肥:中國科學技術大學,2012.

[3] 張海龍,馬鐵華,謝銳,等.基于雙閃存的大容量沖擊波超壓測試系統[J].電子技術應用,2013,39(11):85-88.

[4] 鄭佃好,張紅雨,張洪斌.基于ADV7125的嵌入式系統VGA接口設計[J].單片機與嵌入式系統應用,2011,11(8):37-41.

[5] 鄧春健,王琦,徐秀知,等.基于FPGA和ADV7123的VGA顯示接口的設計和應用[J].電子器件,2006,29(4):37-41.

[6] 廖永清,丁旭昌,付建國,等.基于FPGA的VGA圖像動態顯示控制器的設計與實現[J].電視技術,2011,35(17):52-54.

[7] 王亮,李正,寧婷婷,等.VGA漢字顯示的FPGA設計與實現[J].計算機工程與設計,2009,30(2):275-281.

[8] 周卓然,徐道連,呂鳳飛,等.基于FPGA的VGA圖像顯示系統的設計與實現[J].儀表技術與傳感器,2012(7):90-92.