文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2015.09.016

中文引用格式: 林俊明,鄭耀華, 鄭瑞青,等. 應用于移動手機的SOI線性射頻功率放大器的設計[J].電子技術應用,2015,41(9):60-62.

英文引用格式: Lin Junming,Zheng Yaohua,Zheng Ruiqing,et al. Design of linear RF power amplifier for moblie phones based on SOI technology[J].Application of Electronic Technique,2015,41(9):60-62.

0 引言

隨著信道容量急劇增加,通信系統采用多種調制方式相結合的非恒包絡調制技術,這對功率放大器的線性度提出了更高要求,為了適應當前低功耗及高效率的功率放大器的要求,本文就負載線和傳統功率放大器理論,設計了應用于1.95 GHz WCDMA發射機的線性功率放大器。

SOI(Silicon-On-Insulator,絕緣襯底上的硅)有著成為主流硅工藝的趨勢。SOI是近十多年的新型微電子材料,可以有效解決高電壓、高集成和低功耗的問題。SOI有著非常低的器件噪音和可以抑制浮體效應,對于像濾波器和選頻電路等對噪音要求非常嚴格的電路來說,這無疑是更好的解決方案。SOI工藝可以通過將疊加MOS器件的形式來解決其耐壓問題,而且它有著非常低的功耗和所有的器件都集成在一塊相互絕緣的硅襯底上,并有很好的隔離作用,因此SOI工藝是實現單片射頻功率放大器的一個很好的選擇。

1 電路設計

功率放大器一般輸出功率高而增益較低,為了輸出較高增益和兼顧整體功率放大器的效率與線性度并且實現較低靜態功耗,最終選擇電路的拓撲結構為三級AB類放大器結構,如圖1所示。

整個功率放大器除了輸出匹配網絡(OMN)和輸入匹配網絡(IMN),還有級間匹配網絡(MMN),級間匹配網絡可調整放大器之間的增益平坦度并使每級的效率最高。先設計輸出級,最后設計輸入級,且每級都必須無條件穩定。輸出匹配網絡將50 Ω變換成功率輸出級最優阻抗的共扼,此時的匹配并不是傳統的共扼匹配,因為最優輸出阻抗并不是輸出最大資用功率時的阻抗,這里的共扼只是為了消除MOS管的輸出電容。輸出匹配網絡決定了放大器的輸入反射系數,所以級間匹配將50 Ω的波源阻抗轉換到根據式(2)計算出來的阻抗,輸入級與波源共扼匹配而實現最大功率傳輸。第二級放大器的設計指標根據第三級的輸入1 dB壓縮點功率IP1 dB,3,設計本級的輸出1 dB壓縮點OP1 dB,2,要求滿足關系為:

式(1)的目的是在第二級的線性范圍內,保證第三級輸出也在線性范圍內,第二級的輸出匹配與輸入匹配思想與第三級的設計思路相同,這樣就可以保證每級都能達到預定的1 dB壓縮點輸出功率。

1.1 MOS晶體管的選擇與尺寸估算

MOS管的尺寸參數主要是柵寬與溝道長度,在能實現功能指標的情況下一般都選擇其最小的溝道長度,這是因為MOS器件的發展趨勢是每年按比例縮小的,因此設計也應該適應當前的MOS工藝。

傳統功率放大器輸出電流的基波項可為[4]:

式中Imax表示漏極允許通過的最大電流,Ion,max表示單位柵寬允許通過的最大電流,不過這里求得的柵寬是一個估算值,因此在設計過程中可以根據實際情況進行優化。

1.2 偏置電路設計

為了實現全集成電路設計,選擇在片內集成偏置電路,本文采用的偏置電路如圖2所示。通過合理調節MOS管M1和M2的寬長比,可以實現任意偏置電壓,不過在設計中應該選擇使功耗最小的設計方案。

對于圖2所示的電路,可得其漏極電流表達式為:

由式(11)~式(12)可知,通過合理調節MOS管M1和M2的寬長比,可以實現任意偏置電壓,不過在設計中應該選擇使功耗最小的設計方案。

1.3 輸出匹配電路

匹配電路的類型有L型、PI型和T型,在對Q值沒特定要求的情況下,可以選用元件最小的L型匹配網絡,通過使用雙L型匹配網絡還可以增加放大器的帶寬,不過其缺點是降低了電路的Q值。由于功率放大器的輸入端是調制信號,因此選取L型中高通匹配網絡,而級間匹配采用雙L型或者是T型匹配網絡,輸出匹配網絡使用L型中的高通匹配網絡,如圖1(b)所示。

2 電路仿真與討論

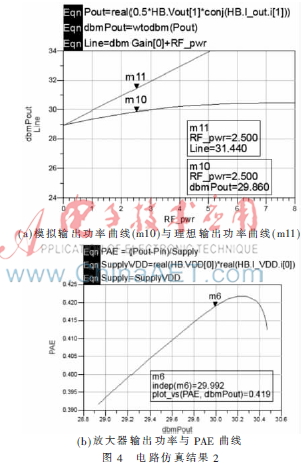

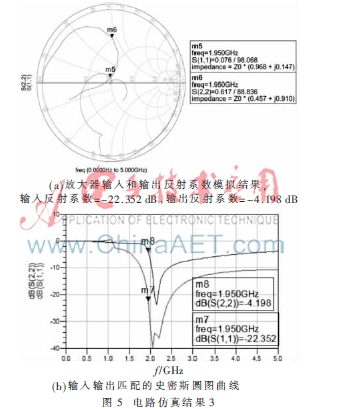

仿真軟體采用Agilent公司的ADS2011,其仿真結果如下:放大器穩定性分析仿真結果如圖3(a)所示,穩定因子在中心頻率處K=4.6>1,因此整個功率放大器在中心頻率處是無條件穩定的。對電路進行S參數仿真,如圖3(b)所示,功率放大器的正向增益為27.7 dB。根據功率增加效率的表達式,可以描繪輸出功率與PAE曲線,如圖4所示。圖4(a)中,標記m10和m11對應的輸出功率分別為31.440 dBm,29.860 dBm,輸入功率為2.5 dBm。結果顯示在輸出功率為30 dB時,PAE約為42%。功率放大器對輸入反射系數要求較高,因為輸出一般接的是天線,因此對輸出反射系數要求有所下降,因為功率放大器一般要求輸出大功率,這會造成輸出不匹配現象。圖5(a)顯示本設計的整體電路的輸入反射系數在中心頻率處為-22.35 dB,輸入和輸出反射系數的史密斯曲線如圖5(b)所示。

3 結束語

本文討論了SOI工藝的物理特性及其在MOS器件中的應用情況,并結合LoadPull技術和IBM公司0.18 μm SOI CMOS工藝,設計一種應用于1.95 GHz的WCDMA全集成功線性率放大器。功率放大器采用三級AB類放大器級聯結構,在工作電壓為2.5 V的情況下,CMOS射頻功率放大器無條件穩定,1 dB壓縮點輸出功率約為30 dBm,增益約為28 dB,最大功率附加效率(PAE)約為42%,最后通過仿真軟件給出模擬結果。

參考文獻

[1] LEE T H.CMOS射頻集成電路設計(第2版)[M].余志平譯.北京:電子工業出版社,2012.

[2] 林成魯.SOI-納米技術時代的高端硅基材料[M].合肥:中國科學技術大學出版社,2009.

[3] E.da Silva.High frequency and microwave engineering[M]. London:MPG Book Ltd,2001.

[4] CRIPPS S C.RF power amplifiers for wireless communica-tions[M].Second Edition.Artech House Publishers,2006.

[5] DAVIS W A,AGARWAL K.Radio frequency circuit design[M].Second Edition.United States of America:Wiley-IEEE Press,2001.

[6] RAAB F H,ASBECK P,CRIPPS S C,et al.Power ampli-fiers andtransmitters for RF and microwave[J].IEEE Trans-MTT,2002,50(3):822-824.