文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2015.10.009

中文引用格式: 趙新超,陳嵐,馮燕,等. 基于混合原型平臺的UART IP核設計與驗證[J].電子技術應用,2015,41(10):39-42.

英文引用格式: Zhao Xinchao,Chen Lan,Feng Yan,et al. Design and verification of UART IP core based on hybird ptototyping platform[J].Application of Electronic Technique,2015,41(10):39-42.

0 引言

隨著片上系統(System on Chip,SoC)設計復雜度的增加,驗證過程也變得更加復雜。傳統的軟硬件設計方法是在軟硬件劃分之后,軟件和硬件同步進行設計,直到硬件(指芯片或開發板)完成后才可以與軟件集成測試;如果此時發現軟件或者硬件設計中存在缺陷需要重新修改設計時,勢必增加設計周期,影響產品的上市時間。所以,當前迫切需要一種在硬件流片之前,便可以對SoC設計進行軟硬件協同驗證的方法。混合原型驗證便是很好的解決方案。

混合原型驗證是虛擬原型與硬件原型相結合的一種驗證技術,通常情況下,SoC設計由硬件設計和軟件設計兩部分組成,硬件設計主要采用寄存器傳輸級(Register Transfer Level,RTL)代碼實現,軟件設計主要在中央處理器(Central Process Unit,CPU)中實現,并通過加載Linux內核、編譯驅動和應用程序來控制硬件與外界進行交互。混合原型驗證是兩者功能相結合的一種驗證方法,可以進行軟硬件協同開發與調試。下面介紹混合原型驗證平臺的設計方法,并以UART IP核為例,詳細闡述其驗證過程和驗證結果,為IP核設計用戶提供一種新型的驗證方案。

1 混合原型驗證平臺

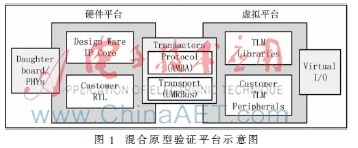

如圖1所示,混合原型驗證平臺由硬件平臺和虛擬平臺兩部分組成,兩者之間通過高速接口Transactors(XACTOR)互聯。其中硬件平臺基于HAPS(High-performance ASIC Prototyping System,HAPS)原型驗證系統實現,平臺中有一款容量高達450萬門的Virtex-6 LX760 FPGA(Filed Programmable Gate Array),可以為用戶提供較大容量的RTL驗證;虛擬平臺主要由一套完善的開發工具包組成,在添加虛擬模型時,通過引入已經搭建好的虛擬軟件開發包,為軟件開發人員將虛擬原型演變為一套現成可用的參考開發工具[1];XACTOR接口通過高速總線UMRBus(Universal Multi-Resource Bus)進行數據傳輸[2],UMRBus是一種高性能、低延時通信總線,它能為所有板載FPGA、存儲器、寄存器和其他資源提供連接功能,其傳輸協議基于AMBA(Advanced Microcontroller Bus Architecture)協議實現。

1.1 硬件平臺

HAPS原型驗證系統由一套HAPS-61高性能ASIC原型驗證平臺和一套復雜的支撐軟件組成,支撐軟件包括:Certify FPGA代碼分割工具、Synplify FPGA綜合工具、Xilinx ISE布局布線工具、Confpro下載工具以及Identify在線調試工具。HAPS-61原型驗證系統的主要特點包括:容納高達450萬門的門級電路;843個用戶I/O接口;12個外部差分時鐘輸出;一個100 MHz的晶振,2個PLLs能夠產生高達700 MHz的時鐘頻率;可配置的電源網絡;高速UMRBus數據傳輸。

1.2 虛擬平臺

與傳統RTL級驗證相比,虛擬平臺的驗證建立在電子系統級(Electronic System Level,ESL)之上,運用SystemC庫和TLM 2.0標準,可以進行快速的系統建模,仿真速度比RTL高很多。虛擬平臺是由一套虛擬軟件開發包(Virtualizer Development Kits,VDK)組成,可以提供軟件的調試、分析和仿真功能,憑借ARM Cortex處理器的高性能模型、基于AMBA協議的總線以及DesignWare IP,開發者可以方便地將其基于ARM處理器的設計分割到虛擬平臺和硬件平臺中。在虛擬平臺中單獨仿真時,通過搭建已經驗證好的TLM模型,用戶可以脫離硬件進行仿真;在與硬件進行協同仿真時,通過引入TLM Library,然后在TLM Creator中模擬PHY或測試設備,再把模擬好的I/O模型映射到基于FPGA的硬件原型HAPS上,最后通過HAPS端口連接真實的外部世界,從而實現軟件和硬件之間的協同開發,加快了系統開發進度。

2 UART IP核混合驗證方案

2.1 整體方案設計

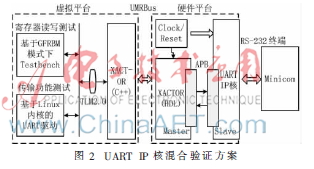

為了驗證已經設計好的UART IP核,構建如圖2所示的混合驗證方案。圖中,中間部分為HAPS硬件平臺,包含了全部FPGA硬件實現,其中UART IP核是自主設計的基于APB(Advanced Peripheral Bus)接口的待驗證IP核,XACTOR是由本系統提供的接口IP,兩端分別通過APB總線連接UART IP核,再通過UMRBus高速總線連接虛擬平臺;Clock/Reset是由HAPS提供的時鐘和復位模塊。左半部分為虛擬平臺,通過基于標準TLM2.0的XACTOR接口,用戶可以訪問硬件單元,從而實現基于事務級模型的協同仿真。虛擬平臺中事務級建模測試方法可以由2種方法實現:基于GFRBM(Generic File Reader Bus Master)模式的Testbench輸入和基于Linux內核的UART驅動加載,分別可以對硬件RTL中的寄存器讀寫功能和IP核數據傳輸功能進行測試。右半部分為連接RS-232串口的超級終端,通過Minicom工具來觀測IP核數據收發的正確性,進而協助虛擬平臺完成整個系統驗證[3]。

2.2 UART IP核設計

2.2.1 UART協議

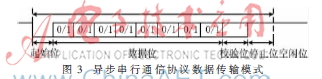

UART接口是計算機串行通信廣泛使用的接口,包含了RS-232、RS-422、RS-485等串口。本設計采用Verilog來開發符合RS-232標準的UART IP核。UART傳輸只需要兩條信號線(RXD,TXD)就可以完成數據的相互通信,接收與發送是全雙工實現。其工作原理是將傳輸數據的每個字符進行編碼,一位接著一位的傳輸,傳輸的速率由波特率時鐘控制[4]。其中各比特的意義如圖3所示。

起始位:低電平信號發起,表示傳輸字符開始;

數據位:起始位后緊接著數據位,位數由7~8位構成一個字符,由時鐘控制從低位開始傳送;

奇偶校驗位:數據位加上這一位后,得出“1”的位數為偶數或者奇數,以此來校驗數據傳輸的正確性;

停止位:可以是1位、1.5位、2位的高電平,是一個數據幀結束的標志;

空閑位:處于高電平狀態,表示當前線路上沒有數據傳送,若空閑位后出現低電平,則表示下一個數據幀的起始位。

2.2.2 功能模塊設計

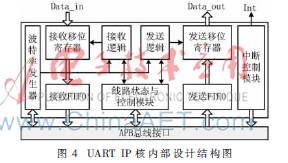

為了簡化IP核設計,在具備基本異步串行收發功能的前提下,去掉了Modem控制器功能模塊。IP核內部設計結構如圖4所示,主要由波特率發生模塊、線路狀態與控制模塊、接收模塊、發送模塊、接收FIFO模塊、發送FIFO模塊、中斷控制模塊等組成[5]。

各模塊之間的工作關系如下:當發送數據時,APB總線把數據寫入發送FIFO中,當發送移位寄存器是空時,先由發送邏輯根據線路狀態對數據進行配置,即在數據頭部加上起始位,在數據尾部加上奇偶校驗位和停止位,然后把數據壓入到發送移位寄存器中,最后在發送時鐘的控制下,通過Data_out線把數據發送出去;接收數據時,在接收時鐘的控制下,串行數據通過Data_in線逐位送入接收移位寄存器中,當檢測到停止位時,數據被轉換為并行數據并送入接收FIFO模塊中,并被總線讀取,后面進入空閑狀態,等待下一次任務。

線路狀態與控制模塊通過地址選通信號鎖存片選信號和地址信號,當片選信號有效時,鎖存讀、寫選通信號,當檢測到讀或寫的數據到來時,進行相關寄存器操作。

中斷控制模塊要求當任何中斷發生時,中斷使能寄存器根據中斷優先級的不同,允許對應的中斷發生。UART IP核的中斷申請可以分為4個優先級,從高至低的順序為:INT0(接收器狀態錯誤),INT1(接收數據準備好),INT2(發送器空),INT3(Modem控制中斷)。

2.2.3 構建UART IP核的FPGA工程

設計完基于APB接口的UART IP核后,為使虛擬平臺能夠通過UMRBus總線訪問IP核,需要把IP核添加到頂層文件包含UMRBus高速接口的FPGA工程中。該功能模塊是由例化的XACTOR實現,XACTOR是由本平臺提供的接口IP,主要通過AMBA協議實現軟件平臺與硬件平臺之間的數據傳輸,每一個XACTOR由一個CAPIM(Client Application Interface Module)組成,系統總共提供了5類XACTOR供用戶使用:APB、AHB、AXI、GPIO、INT。用戶需要根據自己設計的IP核接口類型,選擇對應的XACTOR添加到自己的工程中,然后修改相應的端口、時鐘、reset信號等,從而產生包含UMRBus高速接口的FPGA工程。

2.3 虛擬平臺設計

2.3.1 搭建虛擬平臺

本方案需要在虛擬平臺中創建虛擬模型,并分別搭建能夠對硬件RTL寄存器讀寫功能測試和對IP核數據傳輸功能測試的虛擬平臺。其中,對硬件RTL寄存器讀寫功能測試的虛擬平臺如圖5所示。圖中,i_GFRBM_TLM2作為事件發起方(Initiator),通過連接tlm2bus總線,可以與硬件平臺進行操作;i_ClockGenerator是虛擬時鐘產生模塊,為總線和Initiator提供時鐘單元;i_ResetGenerator是虛擬模型復位模塊,提供系統的復位功能;i_TlmTarget2UmrAMBA和i_IntInitiator2Umr是基于SystemC實現的并與硬件CAPIM相對應的XACTOR,通過標準的TLM2.0 Socket接口,實現軟件平臺與硬件平臺的數據交互功能。

2.3.2 設計腳本

虛擬平臺搭建完成后,需要在i_GFRBM_TLM2中寫入測試腳本訪問硬件寄存器,以測試IP核寄存器設計是否正確。在GFRBM模式下,Testbench采用標準的STL 2.0(Socket Transactor Language)語言實現,STL是由OCPIP(Open Core Protocol International Partnership)組織提出的標準Socket語言,主要由3個不同的子集組成:

(1)Basic commands:基于單指令任務的控制傳輸模式;

(2)Macro statements:采用短指令的突發傳輸序列;

(3)Behavioral statements:用戶自定義控制指令。

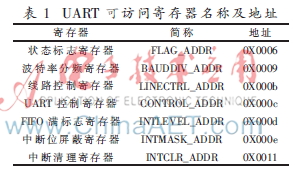

根據本設計需要,UART IP核可以被訪問的寄存器名字和地址如表1所示。

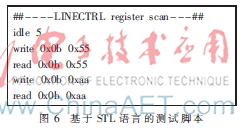

可訪問的寄存器確定完成后,采用STL語言編寫測試腳本,示例如圖6所示。

3 驗證過程與結果分析

混合原型驗證方案中,對IP核進行混合驗證之前,首先需要使用仿真器對RTL代碼進行仿真。當仿真通過之后,才可以在硬件平臺上進行混合原型驗證。硬件實現時,首先采用Certify工具進行代碼分割,再使用Synplify工具進行代碼綜合,然后使用ISE工具進行布局布線并產生可加載的.bin文件,最后使用Confpro工具配置硬件系統。當硬件系統配置完成后,按照圖2所示的方式進行連接,并啟動虛擬平臺開始混合原型驗證。

3.1 寄存器讀寫功能測試

在虛擬平臺中通過GFRBM模式對UART IP核進行寄存器讀寫訪問時,參照2.3.1節中搭建的虛擬平臺和2.3.2節中給出的測試腳本,分別采用固定值讀寫和隨機數讀寫兩種方式測試寄存器,結果如下:

(1)固定值讀寫測試:分別對表1給出的寄存器寫入固定值0x0000、0x5555、0xaaaa、0xffff,然后讀取該寄存器的值。經對比,讀出值與寫入值完全一致。

(2)隨機值讀寫測試:分別對表1給出的寄存器寫入隨機值$random, 然后讀取該寄存器的值。經對比,讀出值與寫入值完全一致。

3.2 UART數據傳輸測試

與寄存器讀寫功能測試不同,在測試UART IP核的傳輸功能時,首先仿照2.3.1節的方法,構建包含處理器IP核模型的虛擬平臺,然后在虛擬平臺中加載ARM?誖CortexTM處理器IP模型,并編譯UART軟件環境,包括操作系統、驅動以及應用程序等。測試時,首先在虛擬平臺中對IP核進行傳輸配置,包括傳輸速率、數據位、奇偶校驗等,并把發送數據通過IP核發送到TXD端口,再通過串口傳送到上位機超級終端進行顯示;接收數據時,超級終端發送數據至IP核的RXD端口,虛擬平臺讀取IP核接收的數據,然后把數據在虛擬平臺中打印出來,從而確定IP核傳輸功能的正確性。下面分別采用單端發送和回環傳輸兩種方法進行測試。

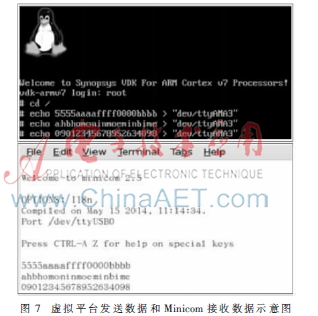

(1)單端發送測試:即從虛擬平臺發送數據,通過UART IP核傳送至超級終端Minicom,在Minicom中顯示發送的數據是否正確。虛擬平臺中,對UART IP核數據傳輸協議配置如下:傳輸速率9 600 b/s、8 bit數據、無校驗位、1 bit停止位,同樣在Minicom中配置相同的傳輸參數。經測試,Minicom接收的數據與發送數據完全一致。測試結果如圖7所示。

(2)回環測試:即從虛擬平臺發送數據,通過UART IP核傳送至Minicom,Minicom接收到數據后,再把接收到的數據發送至UART IP核,虛擬平臺讀取IP核接收的數據,然后在虛擬平臺顯示窗口進行收發數據對比,以此確定回環傳輸的正確性。同樣在虛擬平臺和Minicom中配置如下參數:傳輸速率9 600 b/s、8 bit數據、無校驗位、1 bit停止位。經測試,虛擬平臺接收的數據與發送數據完全一致,從而確定整個通路傳輸是正確的。

4 結論

本文介紹了基于虛擬平臺與硬件平臺相結合的混合原型驗證技術,并以UART IP核為例,對設計過程進行分析并對結果進行驗證。由于采用了混合原型驗證技術,使得SoC設計人員在開發早期便可發現設計的缺陷或故障,進而改進系統的功能和性能,降低開發風險。另外,本方案開發的IP核完全采用Verilog語言設計,移植性好,其接口采用標準的APB總線接口協議,所以不需要用戶進行修改,便可很好地應用于SoC設計中,具有較高的應用價值。

參考文獻

[1] Nithya Ruff.SoC設計:虛擬原型成為主流[J].電子產品世界,2013(1):25-27.

[2] UMRBus Communication System Handbook.2012,V3.14[DB/OL].http://www.synopsys.com.

[3] 吳君欽,李艷麗.一種SoC軟硬件協同驗證方法的設計[J].江西理工大學學報,2011,32(3):65-68.

[4] 朱勤,錢敏.嵌入式UART的設計及FPGA驗證[J].通信技術,2012,45(241):150-153.

[5] 董大成,張建東,史國慶.基于FPGA的UART IP核的設計與實現[J].計算機測量與控制,2012,20(8):2251-2253.