2017年我曾經基于Graphcore的CTO Simon Knowles的演講兩次分析了它們的AI芯片。最近,我們看到更多關于IPU的信息,包括來自第三方的詳細分析和Graphcore的幾個新的演講。基于這些信息,我們可以進一步勾勒(推測)出IPU的架構設計的一些有趣細節。

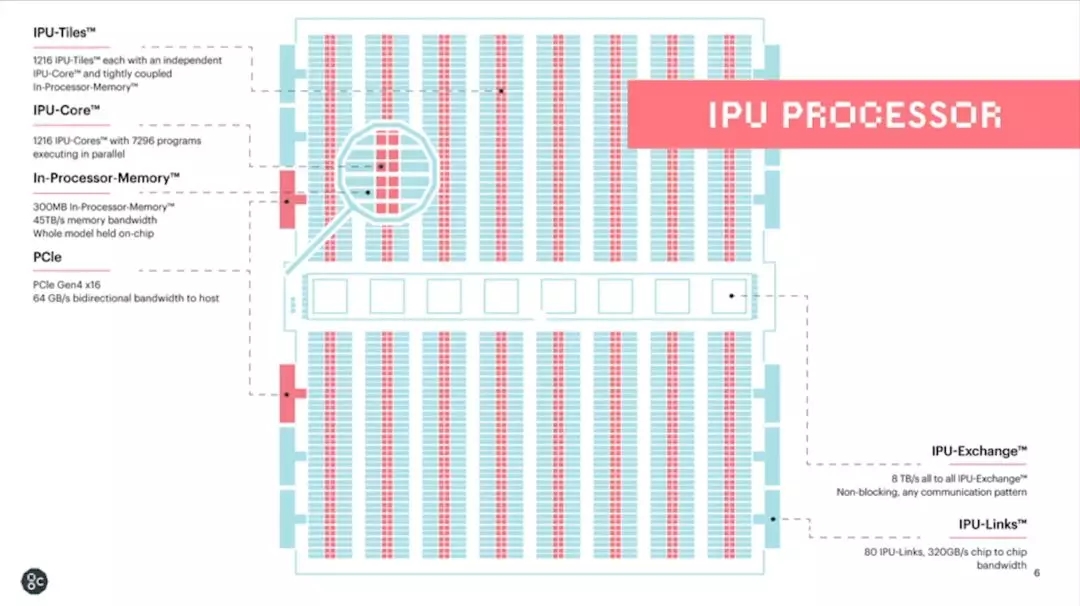

我們先來回顧一下IPU硬件架構中的一些關鍵點。IPU采用的是大規模并行同構眾核架構。其最基本的硬件處理單元是IPU-Core,它是一個SMT多線程處理器,可以同時跑6個線程,更接近多線程CPU,而非GPU的 SIMD/SIMT架構。

IPU-Tiles由IPU-Core和本地的存儲器(256KB SRAM)組成,共有1216個。因此,一顆IPU芯片大約有300MB的片上存儲器,且無外部DRAM接口。連接IPU-Tiles的互聯機制稱作IPU-Exchange,可以實現無阻塞的all-to-all通信,共有大約8TB的帶寬。最后,IPU-Links實現多芯片互聯,PCIe實現和Host CPU的連接。

▲source: Graphcore [3]

在我們做進一步討論之前,大家不妨先思考一下這個架構的優勢,劣勢和實現的挑戰。

對于一個同構眾核架構來說,一般不追求單個核的性能。因此,單個核的設計是比較簡單的,而芯片是通過把大量小核“復制”連接構成的。

這種架構的整體性能(特別是throughput)主要體現在大量處理器核同時工作形成的大規模并行處理能力。而主要的挑戰在于:

1. 算法和數據本身是否有足夠的并行性(Amdahl's law)

2. 要充分發揮眾核的效率,處理器核如何協同工作(通信,同步和數據一致性等問題)。

第一個問題的答案是肯定的。

目前的AI芯片主要是用于加速神經網絡計算的,其模型和數據都有很多并行性可以挖掘,這也是幾乎各類AI芯片需求成立的基礎。

以前,類似的眾核結構不是很成功,其主要原因也是沒有合適的應用,有錘子沒釘子。從這個角度來看,IPU并不是發明了錘子,而是找到了合適的釘子。

即便如此,不同的模型和算子的并行性特征是有很大差異,比如CNN和RNN,稠密矩陣和稀疏矩陣,基本的Convolution和Grouped/Separable Convolutions。要用一個架構高效支持所有應用是不可能的,必須在設計中進行權衡。

第一個架構設計的問題來了,Q1:采用什么樣的基本操作粒度?

而第二個問題則涉及多核/眾核架構的傳統挑戰,Q2:多核如何協同工作?

此外,盡量利用片上存儲進行計算的優勢是很明顯的。但是, 300MB的片上存儲對控制機制和芯片實現都是巨大的挑戰。下表是IPU和CPU,GPU的片上存儲的一些對比,大家可以感受一下。

▲Source:Citadel Tech Report[1]

而這種設計還有一個很明顯的問題就是,Q3:沒有外部DRAM,如果模型放不下怎么辦?特別是在模型越來越大的背景情況下,這個問題可能是大家關注最多的地方。

下面就從上述三個問題出發來討論一下IPU的設計。當然,如我多次所說,架構設計就是trade off,IPU的設計只能說是權衡的結果,而不一定是最佳方案(其實也不一定存在最佳方案)。因此,對于我們來說,思考和討論才是本文想達到的主要目的。

01

Q2:多核如何協同工作?

我想先討論第二個問題,因為IPU對這個問題的回答,實際上決定了IPU的編程模型,同時也對架構設計和芯片實現有重大的影響。

IPU采用了一個稱為BULK SYNCHRONOUS PARALLEL (BSP)的運行模式。這種模式把一次處理分成三步:

1. 本地計算(Computation):每個IPU-core進程都執行僅在本地內存上運行的計算。在此階段,進程之間沒有通信。前提是本地數據要準備好。

2. 同步(BSP Sync),在所有進程都達到同步點之前,任何進程都不會繼續進行到下一個步驟。除了同步點本身以外,此階段都不會進行計算或通信。

3. 通信(Exchange):進程交換數據, 每個進程可以向每個期望的目的存儲器發送消息(單向)。在此階段不進行任何計算。這里要指出的是,數據交換不是僅限于單個IPU,而是可以通過IPU-Link把數據發送給同一板卡或不同板卡上的其它IPU。

▲Source:Graphcore[4]

上圖給出了BSP模式的優勢,在我看來,這個模式最大的優勢就是簡單。

首先,使用這個模式,眾核設計中一系列頭疼的問題要么大大簡化,要么就基本不存在了。第一,通信是單向,只需要從源位置寫到目的位置即可,且通信的同時是不進行運算的,芯片的所有能源都可以用作通信,有利于保證通信的性能。如果不是這種簡化,很難想象IPU是如何實現8TB帶寬all-to-all通信的。同步機制也很輕松,只需要支持發送簡單消息即可,也沒有時序上的風險了。數據一致性的問題不存在了。

第二,這個機制中,處理器核只操作本地存儲器,這樣可以大大簡化處理器核的訪存設計。

第三,片上存儲在同一時間只有一個master在訪問,控制邏輯也可以大大簡化。這個應該也是IPU能夠實現這么多的片上存儲的原因之一。[1]中的實驗配置里,IPU可以工作在1.6GHz。考慮到IPU使用的是16nm工藝,如果不是大幅簡化了片上存儲和通信機制,整體達到這個時鐘頻率是相當困難的。

那么,缺點呢?也很明顯。

第一,計算和通信必須是串行的。我們經常看到的AI系統優化里提到計算時間掩蓋通信時間的策略,目的是支持計算和數據搬移并行執行,縮短整體消耗的時間。Graphcore對串行機制的解釋是,在Dennard scaling難以為繼的背景下,芯片工作的限制在于功耗,大芯片在實際工作時是不可能所有晶體管同時工作的(Dark Silicon問題)。

因此,他們把計算和通信串行來做,兩者都可以在功耗限制下發揮最高性能,整體時間來看并不比并行要差(詳見我之前的文章)。遺憾的是,要嚴格的比較串行和并行模式的實際性能是非常困難的,所以這里我們也只能留下個疑問。

第二,所有的處理器核(包括多芯片情況)都必須按照統一的同步點來工作,如果任務不平衡,就一定會出現處理器核空閑等待的情況。[2]中就給出了一個實際的例子,使用同一個板卡上的2個IPU實現BERT inference的情況。可以看出,開始由于無法平衡的分配任務,IPU0的利用率就比較低。

▲Source:Microsoft[2]

總得來說,BSP模式決定了IPU的硬件設計和編程方法,簡化了硬件設計難度的同時,給軟件工具帶來了更多的挑戰。這里插一張facebook的slides,大家可以參考一下。

回到主題,[1]中對IPU的片上和片間互聯做了大量討論和benchmark,具體數據也挺有意思,可以推測到一些實現細節,大家感興趣的話不妨看看。不過,在理解的IPU的基本設計思路之后,各種測試結果也就很容易理解了。

02

Q1:“采用什么樣的處理粒度?”

上述討論中,我們可以看到,在設計多核協同工作模式的時候,IPU選擇了一個粗粒度的模式。而在處理器核的設計中,IPU則選擇了細粒度和更高的靈活性。

從目前的資料來看,IPU-core是一個相對比較通用的處理器,支持6個線程,包括了一個Accumulating Matrix Product (AMP)單元,每周期可以實現64個混合精度或者16個單精度浮點數的操作。

但是,IPU-core訪問本地SRAM的端口并不寬,讀寫端口最大都是128 bit(據說有兩讀一寫三個端口)。因此,IPU-core的處理粒度的比較細的,不是Nvidia GPU的TensorCore這個粒度的,更不是NVDLA的處理粒度。

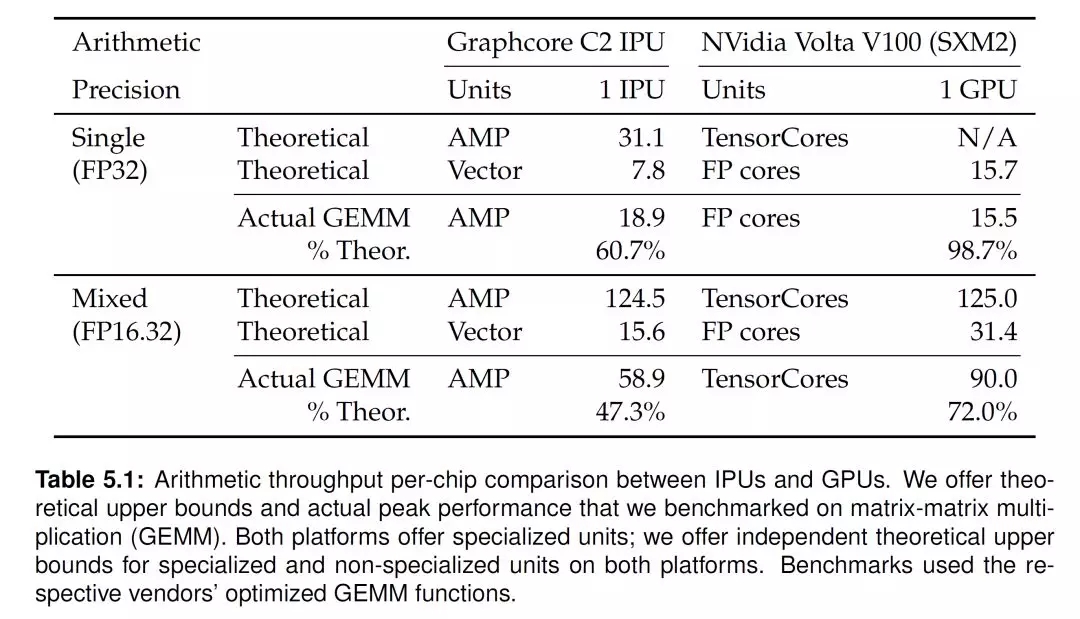

這也意味著在處理稠密矩陣運算的時候,IPU-core并不能最大限度的利用模型和數據的并行特征。[1]中所作的GEMM Benchmark也證實了這一點。單片IPU的混合精度處理能力是124.5T,和V100的TensorCore處理能力125T,是類似的。但實際IPU的GEMM運算效率只能達到50%左右,比TensorCore低不少。

▲Source:Citadel Tech Report[1]

同樣的原因,IPU執行傳統Convolution操作的效率也不算很高(參考[1]中的Benchmark)。

當然,這種設計的好處是處理器核有更好的通用性和靈活性。如果考慮稀疏模型,圖網絡,和一些特殊的Convolution運算,比如Grouped或者Separate Convolution的時候,這種細粒度的處理架構就會表現出相對優勢。這也可以從[1]中的ResNeXt網絡的Benchmark結果反應出來。

從最近Graphcore給出的Benchmark和宣傳來看,他們在努力擴展IPU的應用場景,或者說尋找IPU架構能夠發揮更大效率的應用和算法,比如金融領域。他們還提了個IPU thinking的概念,即在做算法的時候考慮充分利用IPU架構的特點。讓大家從GPU thinking轉換到IPU thinking可能是個很艱巨的任務。但與其和Nvidia正面競爭,試圖取代GPU,可能還不如多培育更適合自己的應用(新的釘子),找到能夠和CPU,GPU共存的空間。

03

Q3:“沒有外部存儲,如果模型放不下怎么辦?”

從設計之初,IPU就是想兼顧data center的training和inference的。而和其它的data center芯片(特別是training芯片)相比,IPU最大的一個差別就是沒有外部DRAM。在最近的NeurIPS 2019的一個講演中,Graphcore的Tom Wilsonk分享了利用IPU做BERT training和inference的示例,正好可以幫助我們分析這個問題。

總的來說,Graphcore的解決方式包括了幾個方面。

第一,是多芯片互聯。這個說起來很簡單,一個芯片放不下就多來幾個,但實現中對片間互聯機制的要求很高。前面介紹了IPU可以通過IPU-Link進行多芯片擴展,從[1]中可以看出,多個IPU芯片可以構成一個大的虛擬IPU(如下圖所示,最大8張卡16顆芯片)。虛擬IPU的編程模型和單個IPU是類似的,差別僅在于,數據交換階段,數據要發送到最遠的IPU需要更長的延時。更詳細的延時數據,大家可以在[1]中查到。

▲Source:CitadelTech Report[1]

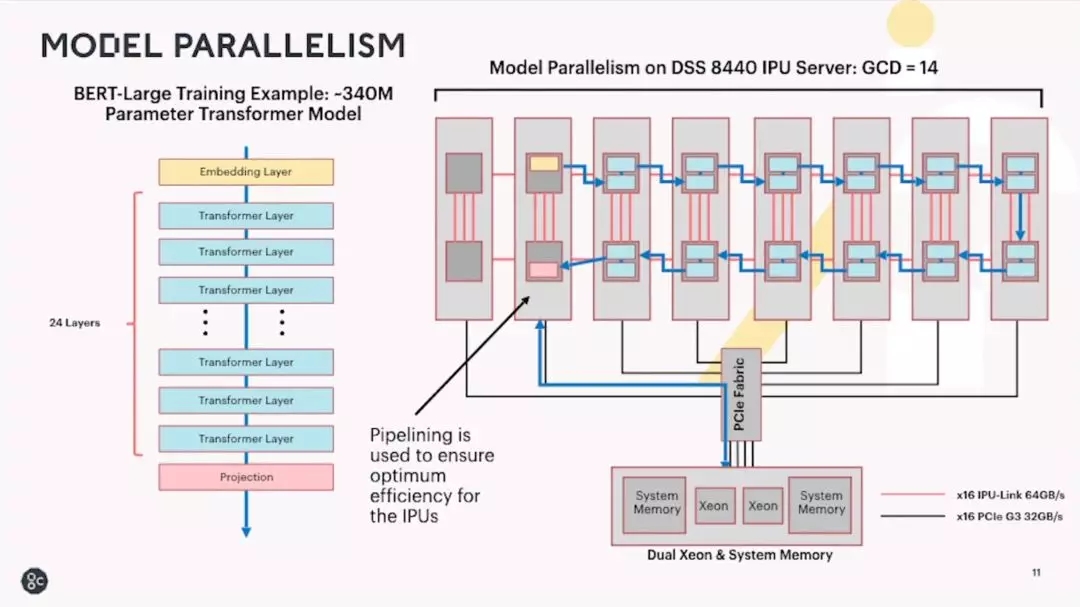

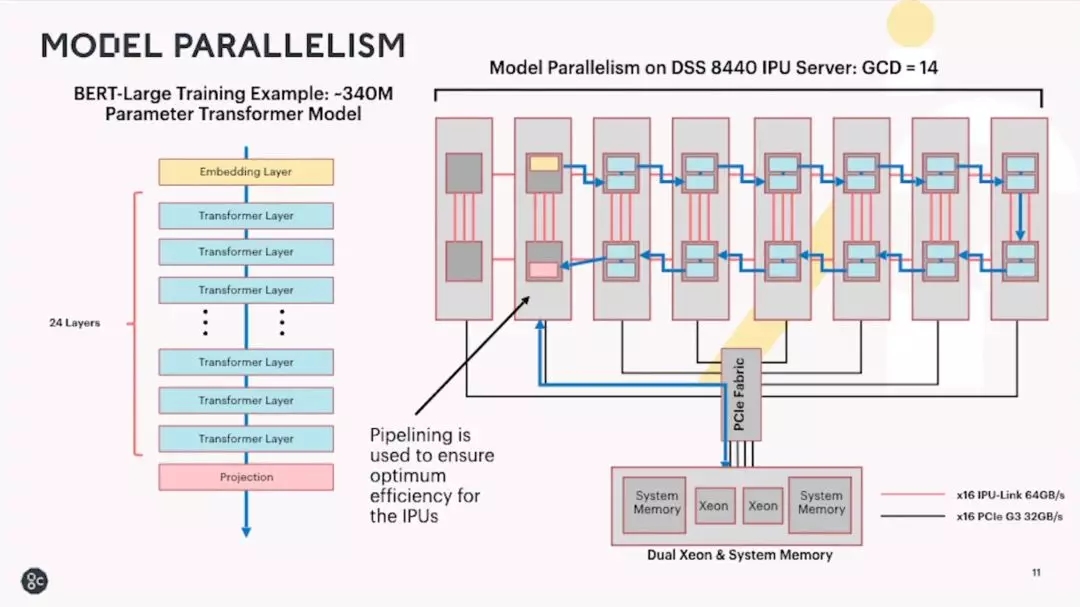

第二是模型并行,即把模型分布到多個核甚至多個芯片來執行inference或training。下面兩個圖分別是BERT模型的inference和training的配置。其中一路inference可以用兩顆IPU芯片實現(和[2]分析的類似),training則使用7張卡,14顆IPU芯片采用pipeline的模式實現。

▲Source:Graphcore[3]

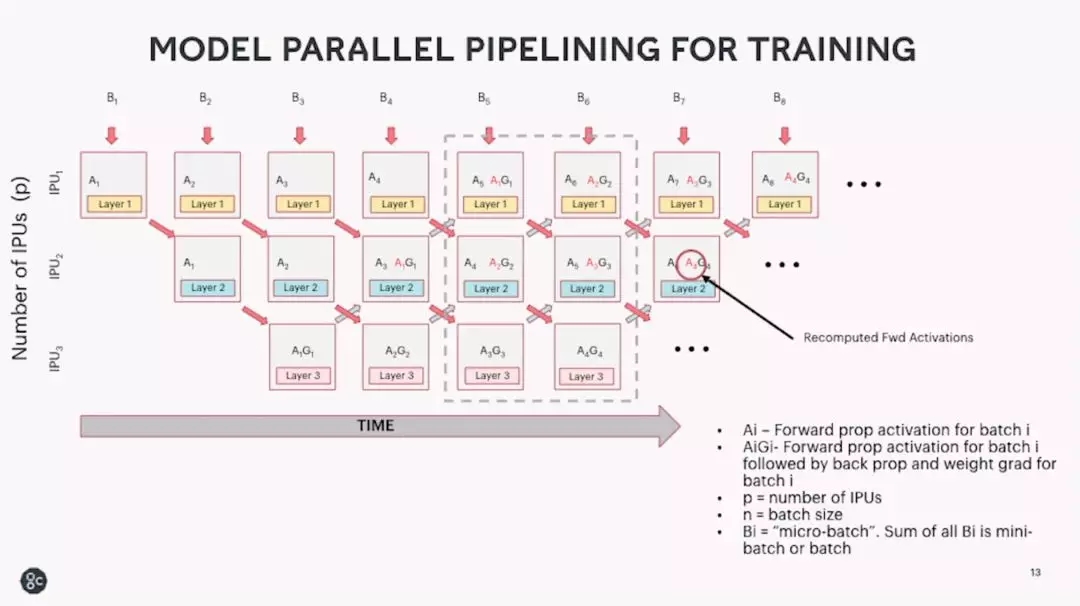

具體的training模型并行pipeline模式如下圖。這里還有一個trick,就是通過re-compute前向activation來減少存儲的需求。

▲Source:Graphcore[3]

從上述例子我們可以看出Graphcore解決存儲容量問題的一些思路。Benchmark我就不貼了,大家可以看[3]。

更近一步,一個有趣的問題是,Graphcore是否會在下一代產品中加上外部存儲的接口呢?如果要加的話,基于BSP的編程模型是否需要修改?片上通信是否也需要做比較大的改動以匹配外部存儲的數據帶寬呢?片上的處理器核數量或者SRAM數量是否要減少呢?等等。

感覺這個改動有可能會對IPU架構設計的基礎產生很大影響,也許并不是單純加個DDR/HBM接口這么簡單。或者,可以不改變基本的架構設計理念,而是通過chiplet的模式直接在封裝里擴展更多的IPU... ...

讓我們拭目以待吧。