在傳統的登納德縮放比例定律(Dennard scaling)大放異彩的日子里,我們經常會想起平面晶體管。其材料結構上的特性也被簡化為片狀電阻(只包含電阻電容等參數信息)。這樣就會導致其器件是平面二維的抽象概念,而為了理解MOS管的底層電路設計,我們大部分的假設和建模也都設計為2軸。

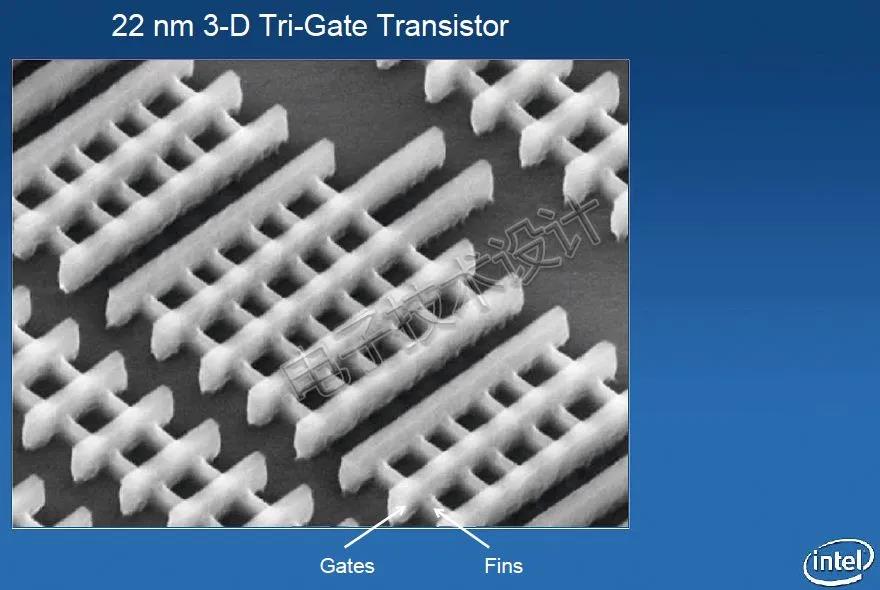

慢慢的思路開始發生轉變,二維設計開始被材料物理學特性所打破,越來越復雜的特性開始展示在科學家和工程師面前,最終MOS和三極管等器件誕生出了FinFET技術,一舉將二維平面帶入到“3D”時代。

圖1:來自Intel的原始三維FinFET。(圖片來源:Intel)

當然技術路線的更新換代往往還伴隨著名詞和術語的重新調整、修改和復用等。而現代的技術人員繼續使用“MOSFET”未免有失偏頗,畢竟其工藝和設計包括使用材料都截然不同(氧化物和高-K介質)。MISFET一詞會更準確,讀起來也比較容易,而且還有點像用來形容技術領域工程師的某個詞(譯者注:即MISFIT一詞,這是作者的自嘲,形容不太合群、格格不入的人)。

最近Nature期刊的一篇在線文章“Promises and prospects of two-dimensional transistors”提供了對半導體技術未來發展的見解,探討了硅基材料晶圓生產的終點。當然不僅是因為傳統FinFET逐漸失去動力(圖1),同時也因為未來的器件將足夠薄(單層或兩層),可以看成是二維的,不用說都知道,像硅這樣的傳統3D半導體在2D領域里效果不佳。

從材料學角度來看,還有一類被稱為過渡金屬二鹵化物(TMD或TMCD)的材料,從材料學角度來看,還有一類被稱為過渡金屬二鹵化物(TMD或TMCD)的材料,例如二硫化鉬(MoS2)、二硒化鉬(MoSe2)、二碲化鉬(MoTe2)、二硒化鎢(WSe2)和二硫化鎢(WS2)。

前面提到的Nature期刊文章的主要作者是UCLA加利福尼亞納米系統研究所的Xiangfeng Duan,以及中國湖南大學和韓國三星電子技術學院(SAIT)的研究人員,他們都指出TMD(過渡金屬硫化物)材料在未來二維半導體材料生產中具備廣泛的應用前景。

路線圖

Nature期刊的這篇文章是最前沿的研究,當然我們可以從其他的資料中看看現今的技術發展路線。

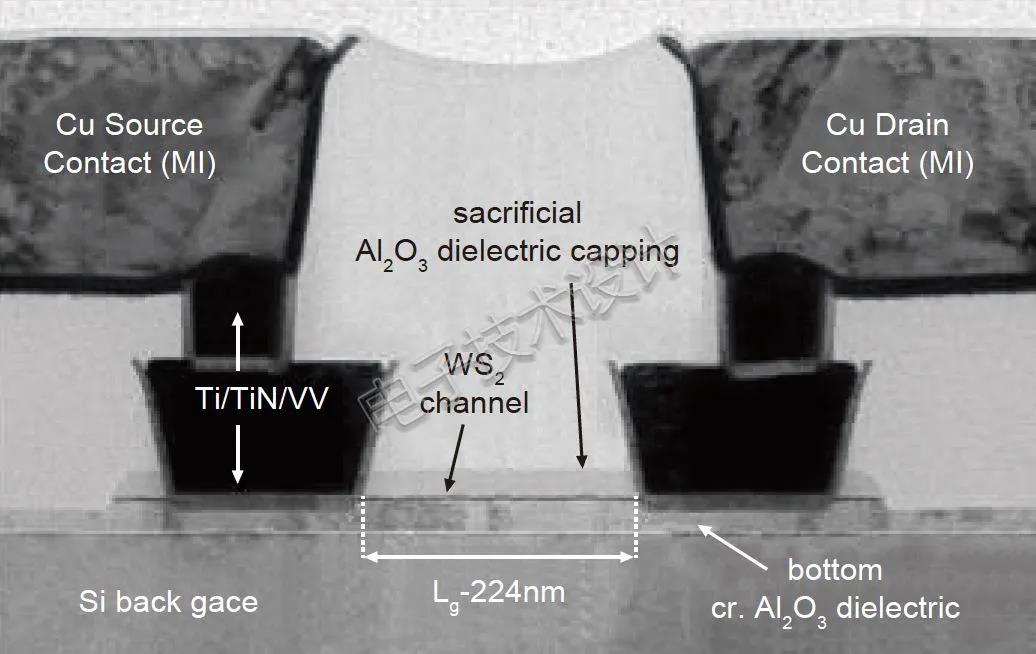

圖2:IMEC 通道晶體管。(圖片來源:IEEE)

在對未來的發展技術進行預測方面,微電子研究中心(IMEC)是最權威的機構之一。2020年12月舉行的國際電子設備會議(IEDM)從多個角度討論了從材料到“芯片結構”(可能特意避免使用“芯粒(chiplet)”一詞)縮放的前景和未來。

為了使標準單元邏輯將來縮小到4軌道單元以下,IMEC寄希望于采用二維材料的晶體管。IMEC在路線圖中定義未來的2D晶體管技術可以達到或超越“1nm”工藝節點,其展示了極性互補的堆疊“納米片”結構制成的CFET晶體管,擁有四個軌道單元,每個大約在1.5nm左右。IMEC還指出,在近十年間,大量的技術革新和信息流動帶動了整個產業發展。

IMEC正在尋找用于MOS管通道的新型材料WSi2(圖2),IEEE報道稱IMEC在300mm晶圓產線成功制造出了這種MISFET管芯片。

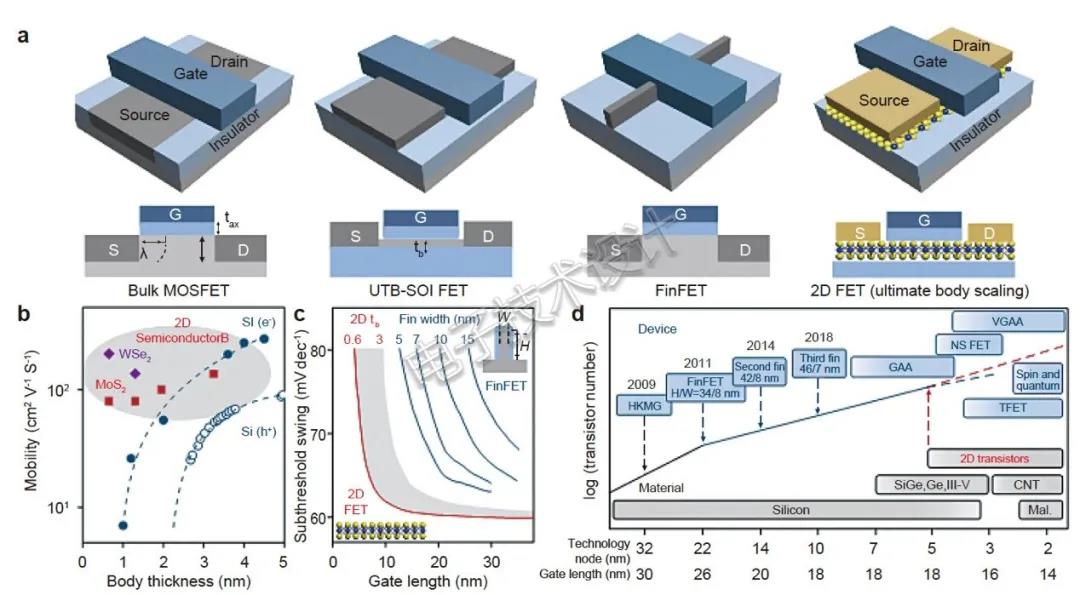

2015年發布的舊版International Technology Roadmap for Semiconductors(ITRS)最后預測,到2021年,硅CMOS晶體管的電流最大只有約1500?A/mm。Nature期刊引用了這篇文章,并重新預測了2021年的目標。圖3比較了舊版與最新的官方路線圖。

圖3:從體硅MOSFET到二維MISFET。(圖片來源:Nature)

ITRS已被能夠更全面描繪微電子技術發展的

International Roadmap for Devices and Systems(IRDS)所取代。舊的ITRS團隊長期以來一直使行業保持在繼有軌道上發展,但這并不是說不能對它進行調整以迎接新的挑戰。

最新版IRDS在2020年發布可謂相當及時。許多老朋友因為IRDS又重新聚在了一起,還是熟悉的模式,但是對舊工作組進行了一些調整。我們最感興趣的是深度摩爾(More Moore)和超越CMOS(Beyond CMOS)的路線圖。

我們可以從最新的深度摩爾來看一看預測結果是否正確,傳統CMOS的最大導通電流應略高于1700?A/?m。如果使用之前的ITRS路線圖,新材料驅動電流數字更讓人滿意,所以之前是低估了硅材料的實力。這里只是將新型二維材料與常規技術進行比較,因此數據非常接近。

到目前為止,一切都還說得通,但我們還是要了解IRDS BC(超越CMOS)技術人員是怎么想的。畢竟我們不想像從前的人一樣,想當然地就認為地球是平的。

一些人預測目前的技術會被淘汰,他們認為2028年將使用二維材料,這也是“1.5nm”節點的時間軸。

電流密度不會說謊

2D transistor review的作者提出,許多用于確定新材料適用性或衡量新材料發展進度的指標可能阻礙了半導體材料的發展。究其根本,還是性能決定一切,而不是看這些材料制造的器件的某些物理屬性是否能打破實驗室的世界紀錄。

許多用于確定新材料適用性的指標可能阻礙了半導體材料的發展,因為器件性能至關重要——很多材料制造出的器件的某些物理性質不可能打破實驗室的世界紀錄。

對于實際應用中的縮放技術,功耗、性能、面積和成本(P-P-A-C)缺一不可。只有在各種因素達到工程平衡的前提下,新的晶體管設計和材料才能投入批量生產。

電流驅動能力是衡量晶體管的重要性能指標之一,就是我們所說的飽和驅動電流,其基準測量值為,在半導體行業以μA/μm為單位來測量。Duan和合作者提到,其他常見指標,如遷移率(?)和接觸電阻(Rc),可能無法說清問題。具體地說,這兩個數據點有可能導致“模棱兩可甚至相互矛盾的結論”。研究人員列舉了一些報道,稱高遷移率或低接觸電阻并不能表明是高的驅動電流。

重點是什么?

這篇Nature文章認為耗費精力改善遷移率或接觸電阻沒什么意義,研究人員往往為了解釋晶體管獲得的電流密度而絞盡腦汁進行器件建模。Duan及其同事希望使用同一個指標來比較二維晶體管與傳統技術,以衡量下一代的高性能產品。不過,二維晶體管目前得到的最好數據是傳統硅晶體管的一半左右(或更少,具體取決于使用什么TMD材料)。

潛力與挑戰

縮小硅通道的問題在于,隨著厚度的減小(目前采用5nm技術,未來基體厚度將小于3nm),遷移率會迅速下降。因此,TMD二維材料將比硅更具競爭優勢,在1nm厚度以下可以輕松維持遷移率。

我們又在考慮遷移率了。奇怪吧?

我們來看一下硅。平心而論,這種半導體材料具有良好的特性,它的機制眾所周知,硅薄層中遷移率下降及其背后的原因大家都能接受。

人們對二維材料的認識還不全面。不過,材料層的厚度已漸漸接近單原子厚度,遷移率的值卻保持不變,這證明了人們對二維材料的理解大體正確。根據二維材料在未來技術節點中所具備的物理優勢來看,這樣的材料可以用于生產。

但是,IRDS路線圖中提出的2028年將開始采用二維材料,在這之前肯定仍然存在很多問題。

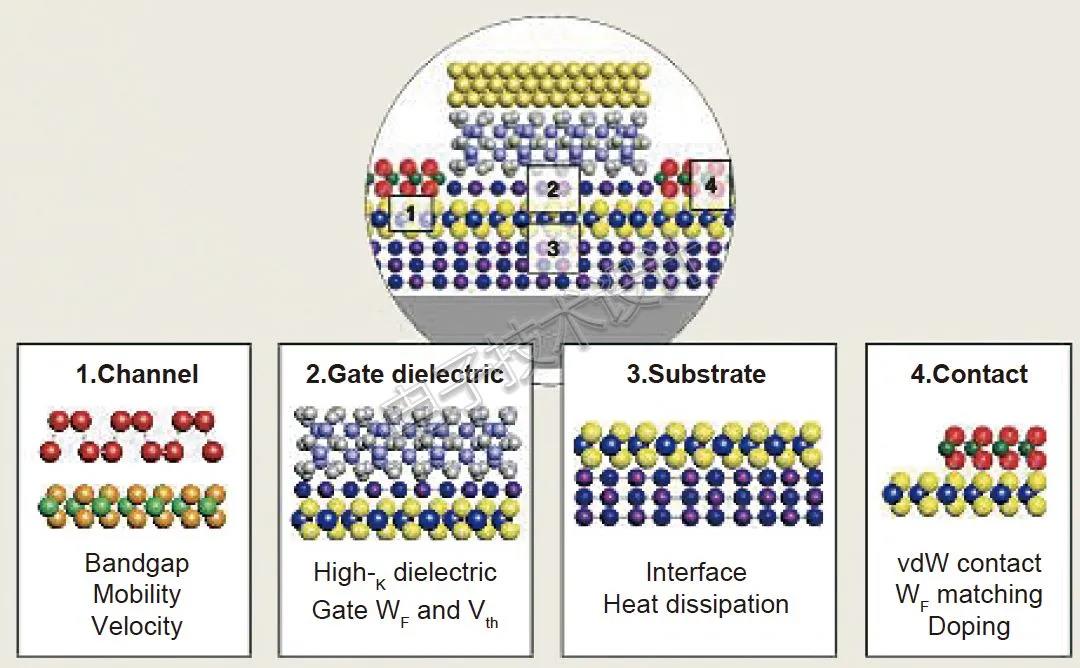

二維晶體管的最佳飽和驅動電流取決于四個主要因素:本征材料特性、接觸電阻、半導體-介質界面和散熱。圖4顯示了理想二維MISFET的四個關鍵要素。

在當前技術中,晶體管是利用重摻雜的源極和漏極區域來將接觸電阻降至最低的。但二維晶格不能用這種方法,因為它只有一個原子那么厚。新器件需要一種新方法。現在已經提出了幾種新的觸點技術,并對邊緣觸點法進行了演示,還涉及既有潛力又有趣但還未經驗證的橫向金屬-半導體異質結構。

Duan及同事則認為另一種有趣的新技術最有希望——直接的范德華(VDW)觸點,這種技術可提供干凈的界面和可調節的金屬半導體勢壘。Nature雜志的另一篇在線文章“2D Materials and Applications”更詳細地介紹了VDW觸點。

當所設計的器件厚度大約為一層一個至幾個原子時,設計的成功明顯依賴于是否選擇了合適的襯底材料。需要考慮的一個主要因素是熱性能,氮化硼(BN)具有較好的熱性能,還能提供較高的界面質量,這反過來有助于二維晶體高-K柵極電介質的集成。

圖4:理想二維MISFET的四個關鍵要素。(圖片來源:Nature)

盡管在關鍵領域已取得了很大的進步,但通道材料、觸點、電介質、熱界面和器件幾何結構未能同步得到優化。

要做的事還有很多,時間卻很緊。只有等到三星或臺積電宣布的那一天,才能真正知道誰是“1.5nm”工藝的最終贏家。值得一提的是,SAIT為此做出了重大貢獻。

接下來,Duan及其合著者研究了新材料“從實驗室進入代工廠”的情況。

盡管氮化硼所顯示的特性極其適用于生產300mm襯底,但在這種尺寸上沉積TMD多數時候都會產生多晶而不是所需的單晶材料。

許多二維材料與堆棧中相鄰層的粘合性較差,在加工過程中容易發生化學腐蝕,從而導致制造過程之中或之后發生層的剝落和器件故障。

我們暫且把這個主要的絆腳石放在一邊。問題已經夠嚴重了,就沒必要再散布悲觀情緒了。

代價幾何?

臺積電或三星將是未來新材料或新器件先進技術的踐行者,我們目前還不知道他們的計劃是什么,但是他們在工藝集成方面的卓越表現可能會推動二維晶體管的使用。

Nature文章的作者們意識到,二維晶體管需要“殺手級應用”才能投入生產——這是硅晶圓生產中資深玩家和巨額投資的老套了。作者認為,在可預見的未來,二維半導體不太可能完全取代硅。我不確定這里“可預見”指的是何時,因為2028年轉眼就會到來。

答案可能在于3D集成。與通常出現在“超越摩爾(More than Moore)”解決方案中的3D系統集成不同,這里指的是真正的單片式3D集成電路。“由于二維晶體本身具有自立性和無懸空鍵特性,因此非常適合多層集成。”采用二維器件的一個主要問題是襯底,將它們堆疊在傳統的硅前端可能可以克服這一挑戰。

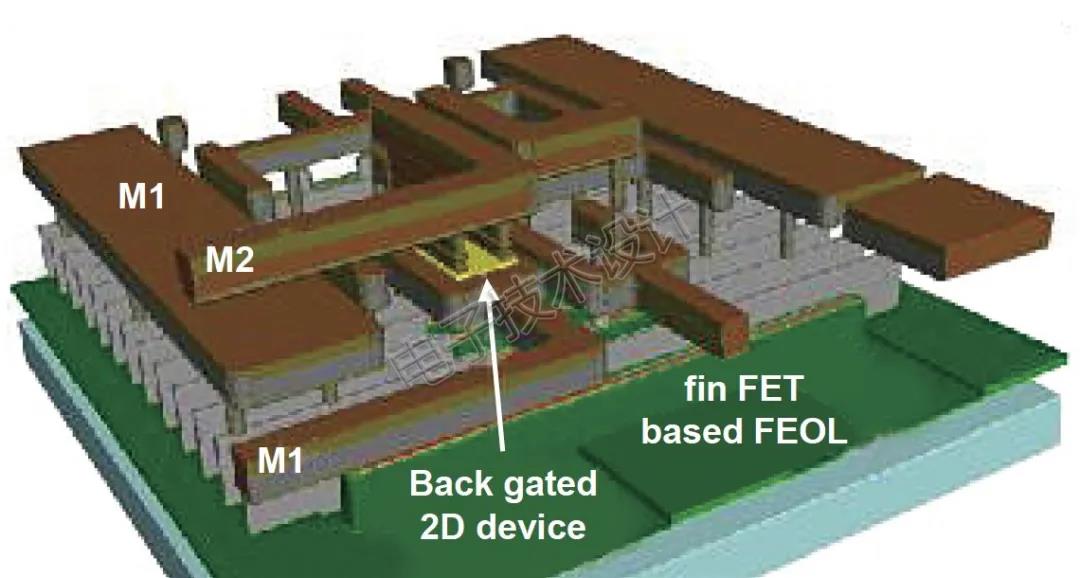

二維材料能夠在比硅前端更低的溫度下生產,而且二維材料可以采用目前的生產線后端(BEOL)金屬化工藝。除了能夠在同一晶圓襯底上提供有源電路層堆疊,集成到BEOL中還有另一個好處——就像IMEC所展示的晶體管那樣,二維通道的背柵功能可以直接集成進這個流程(圖5)。

圖5:集成到標準金屬化工藝中的IMEC背柵二維晶體管。(圖片來源:IEEE)

二維技術另一種可能的應用是柔性電子器件。柔性器件通常采用有機半導體,其性能比采用二維材料要低好幾個數量級。二維材料具有高性能和靈活性,“柔性、可折疊或適應不規則表面”的高速電路適合多種新的應用。

盡管面臨挑戰,Duan和他的合著者相信,從理論上講,沒有任何障礙可以阻止集成電路晶體管在工業領域使用二維材料。

未來使用二維晶體管看來是大勢所趨。如果在幾年前,這樣徹底的改變是不可想象的。

快速看一下技術路線圖和所做的預測可以發現,在未來幾年中,集成電路技術將發生巨大的變化,因此,二碲化鉬這樣的材料不斷被提及就并不奇怪了。

當然,總有很多大事情會超出人們的預期。接下來是什么?如果我們一直降低維度,那么二維將降到一維。其中一項技術預言就是一維的碳納米管晶體管。

必須承認,變化將是半導體技術領域永恒的主題。