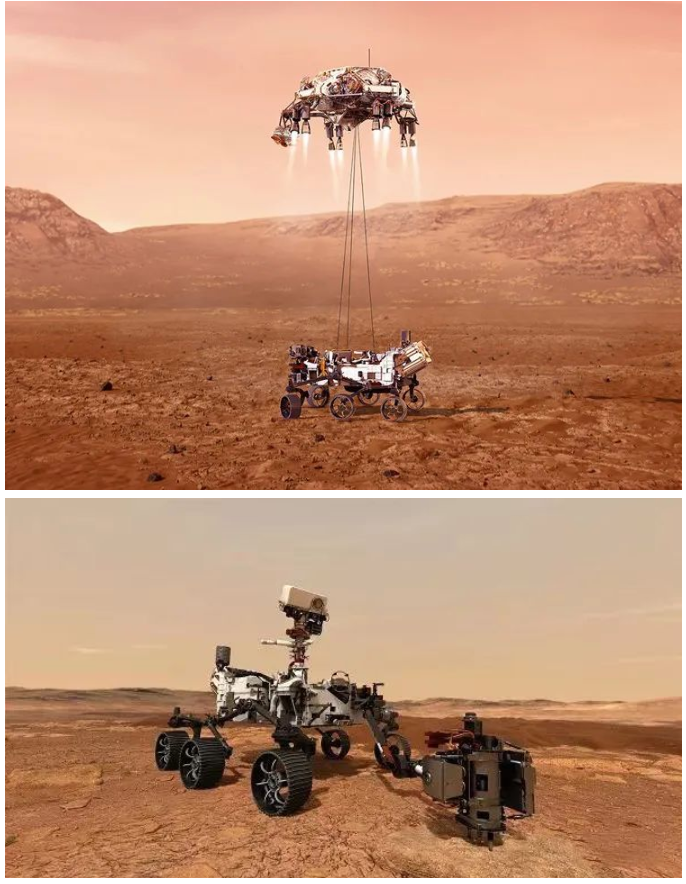

近期全球掀起一陣火星熱。美國太空總署(NASA)毅力號成功登陸火星,并公布火星照片后,更引起全球矚目。不過如此先進的太空探測任務背后,毅力號使用的卻是20 多年前技術的處理器,經過產品任務強化與優化后,成為本次任務成功的重要推手。

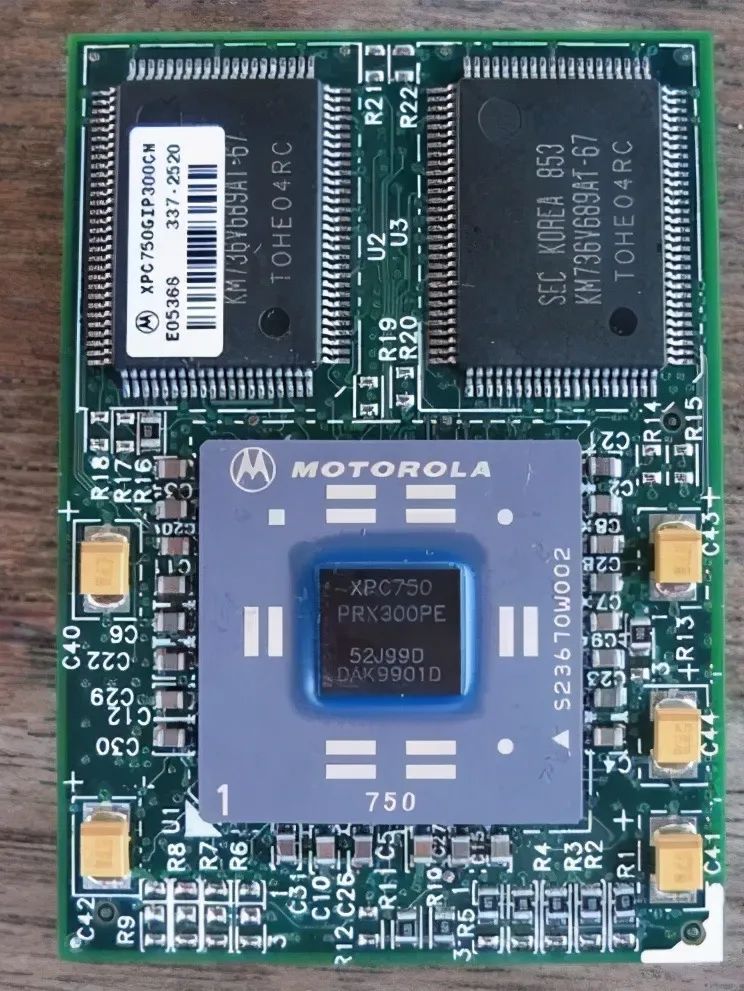

首先毅力號火星探測器搭載的機智號火星直升機,它使用的是民用、消費級芯片組高通驍龍 801處理器。這款處理器發布時間是2014年,與當前高通驍龍888處理器相比已經非常落后。然而毅力號使用的更是1998年生產的PowerPC 750處理器,那為什么毅力號會選用20多年前技術的處理器呢?

外媒報道,毅力號搭載的處理器型號為PowerPC 750 處理器,與1998年蘋果出品的iMac G3 電腦同款,對比蘋果最近推出的M1 ARM 架構處理器擁有最高主頻3.2GHz,晶體管數量達160 億個,PowerPC 750 處理器最高主頻速度僅233MHz,且晶體管數量也只有600 萬個,但單價仍高達20 萬美元(約130萬元)。

報道解釋,毅力號的PowerPC 750 處理器單價會如此昂貴,,并非因為性能超強大,而是必須應對未知的太空環境,因此對處理器進行抗輻射、耐寒冷功能等強化,美國航空航天局花費20萬美元由BAE系統公司進行定制生產 。此處理器雖然架構依舊,但結構強化與優化,導致價格昂貴,也非量產型處理器。它是由BAE Systems使用0.25或0.15um工藝制造的,管芯面積為130mm2。CPU本身可以承受200,000至1,000,000 Rads,溫度范圍為-55至125°C。

報道進一步指出,NASA 之所以選擇舊架構處理器的原因,在于舊架構處理器運作可靠度更成熟。因毅力號火星探測器較特殊,需要長時間穩定運行,因此執行主頻速度成其次,且毅力號一般運作并不需要太強大的運算能力。故就需求來說,舊架構PowerPC 750 處理器完全可以勝任。

而機智號火星直升機使用的驍龍處理器成本相對來說比較低,因為該直升機只會進行簡單的任務不參與重要任務。再加上保暖系統后機智號可以讓處理器保持在特定的溫度中,這樣不必花費太多錢進行定制又不至于太容易損壞。

▍航天級芯片普遍“一顆能買一套房”

實際上,航天級的芯片價格一直是非常嚇人的。美國Xilinx有一款宇航級FPGA,號稱具有10級抗輻射性能,屬于全球最機密的芯片之一。江湖傳言,這顆芯片的價格超過500萬元。

以下榜單芯片,堪稱芯片極品中的王中王;當然,由于筆者水平和眼界所限,榜單僅供參考,不過價格基本靠譜哦!

1、XQR5VFX130-1CF1752V

品牌:XILINX封裝:BGA用途:宇航級/抗輻射外形尺寸:裸片mm價格:》120萬說明:原廠的價格為3-4萬美元,有供應商報價400萬人民幣,但是據說都沒有辦法供貨。

2、XQR4VSX55-10CF1140V

品牌:XILINX封裝:CLCC用途:宇航級/抗輻射價格:》50萬說明:原廠的價格為2.5萬美元左右,現在的市場價格基本上翻了3-10倍左右,有人愿意出130萬以上的買價,可見芯片的不菲價值。

3、XQR2V6000-4CF1144H

品牌:XILINX封裝:BGA類型:宇航級/抗輻射價格:》80萬說明:原廠的價格為2-3萬美元,中國渠道市場報價大約在100萬人民幣左右,據說中國只有一個孤品了。

4、AT697F-KG-E

品牌:Atmel封裝:MQFP256用途:宇航級/抗輻射性能:86MIPS(Dhrystone的2.1)消耗功率:1W在100MHz價格:》60萬單元架構:SPARCV8高性能低功耗的32位體系結構說明:原廠報價在2-3萬美元,市場報價在50-70萬元之間。

5、TSC695F

品牌:Atmel封裝:MQFP256類型:宇航級CPU外形尺寸:裸模核心功耗:1.0W典型值價格:》45萬單元架構:SPARCV7高性能RISC架構整數單元性能:20MIPS/5MFLOPS(雙精度),在系統時鐘為25MHz質量等級:ESCC與9512/003和QML-Q或V帶5962-00540說明:原廠報價在2萬美元左右,市場報價在6-8萬美元。

▍航天器中的宇航級芯片設計有什么特別之處?

宇航級芯片是航天航空電子裝備的心臟,宇航級芯片必須具備抗輻照特性,其身價往往是我們生活中常見的消費級芯片的數十倍,甚至成百上千倍。那么,與消費級芯片相比,這些昂貴的宇航級芯片在設計階段有什么特別之處呢?知乎用戶@Forever snow 作出了詳細的解答。

1.宇航級芯片所處的空間環境

在航天器運行的空間環境中,存在著大量的高能粒子和宇宙射線。這些粒子和射線會穿透航天器屏蔽層,與元器件的材料相互作用產生輻射效應,引起器件性能退化或功能異常,影響航天器的在軌安全。引起器件輻射效應的主要空間輻射源包括地球輻射帶、銀河宇宙射線、太陽宇宙線和人工輻射。

其中,對芯片工作影響最為嚴重的輻射效應當屬“單粒子效應”。

據數據統計,從 1971 年到 1986 年間,國外發射的 39 顆同步衛星共發生了 1589 次故障,有 1129 次故障與空間輻射有關,且其中的 621 次故障是由于單粒子效應導致的。這些統計數據說明了航天應用中電子器件的主要故障來自于空間輻射,而單粒子效應導致的故障在其中占較大比重。

這些故障中,部分是永久性不可逆的,如發生單粒子鎖定導致芯片內部局部短路從而產生大電流燒毀器件。針對此類錯誤可以應用一些特定工藝或器件庫來避免。而太空中大部分錯誤是由于半導體器件的邏輯狀態跳變而導致的可恢復的錯誤,如單粒子翻轉導致存儲器存儲內容錯誤。

單粒子翻轉(Single-Event Upsets,SEU)指的是元器件受輻照影響引起電位狀態的跳變,“0”變成“1”,或者“1”變成“0”,但一般不會造成器件的物理性損傷。正因為“單粒子翻轉”頻繁出現,因此在芯片設計階段需要重點關注。這也是這篇文章的重點。

2.在芯片設計階段如何防護“單粒子翻轉”

(1) 選擇合適的工藝制程

在航天領域,并不是工藝制程越小越好。通常來講,工藝制程越小,抗輻照能力越差。因此,為了確保可靠性,一般會選擇較大線寬的制程,比如0.18um、90nm、65nm等,而不會一味追求摩爾定律的前沿制程。

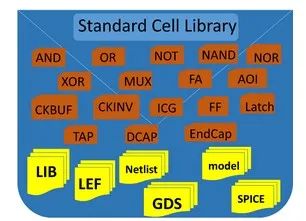

(2)加固標準單元工藝庫

標準單元工藝庫是數字芯片的基石。如果把數字芯片看做一個建筑,標準單元工藝庫就是構成建筑的磚塊。標準單元工藝庫包括反相器、與門、寄存器、選擇器、全加器等多種基本單元,每一個標準單元對應著多個不同尺寸(W/L)、不同驅動能力的單元電路,基于這些基本單元即可構成復雜的數字芯片。

鑒于數字芯片的超大規模,已經很難通過全定制電路結構的方式來設計,而直接對商用工藝庫進行加固則是設計成本最低的選擇。在制造廠商提供的標準單元庫基礎上結合抗輻照加固措施,使設計出來的輸入輸出單元庫具有抗輻照能力。加固之后的工藝庫需要晶圓廠流片驗證。

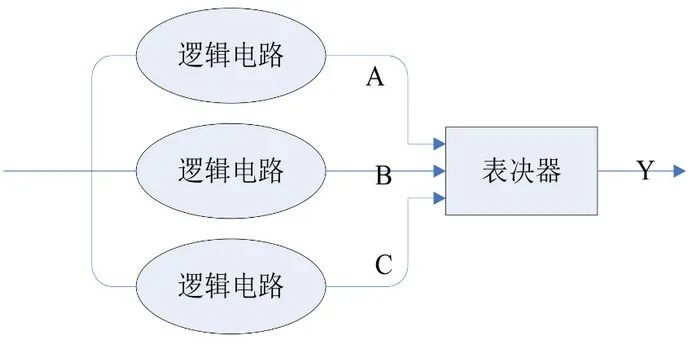

(3)設計冗余化

在抗輻照加固方法中,三模冗余(TMR)是最具有代表的容錯機制。同一時間三個功能相同的模塊分別執行一樣的操作,鑒于單粒子翻轉瞬時僅能打翻1路,“三選二”的投票器將會選出其余兩路的正確結果,增強電路系統的可靠性。三模冗余最顯著優點是糾錯能力強,且設計簡單,大大提高電路可靠性;但缺點也是顯而易見,會將電路增大3倍以上。TMR的方法較為靈活,可根據性能需求在寄存器級、電路級、模塊級等任意層次設計TMR,部分EDA工具也可自動插入。

錯誤檢測與糾正電路(Error Detection And Correction,EDAC)也是一種簡單高效的防護單粒子翻轉的電路設計方法。EDAC 主要依據檢錯、糾錯的原理,通過轉換電路將寫入的數據生成校驗碼并保存,當讀出時靠對校驗碼進行判定,若只有一位出錯系統則自動糾正并將正確的數據輸出,同時還會進行數據的回寫從而覆蓋原來出錯的數據。EDAC盡管糾錯能力強大,但是需要糾錯、譯碼電路,因此結構較為復雜,不適宜用于高性能的數據通道中。EDAC也可用于糾正多bit出錯的情況,但是糾錯電路會更加復雜。

權衡TMR和EDAC的優缺點,通常會在邏輯電路設計中使用TMR,在存儲器讀寫電路中使用EDAC。

(4)模塊獨立化

單粒子翻轉頻繁出現,必須考慮到翻轉發生之后不影響芯片的整體功能。因此,在架構設計中需要盡可能確保模塊之間保持較強的獨立性,盡可能具備獨立的復位功能,使得在單粒子打翻信號值之后,一方面出錯電路能夠盡快通過復位信號恢復正常;另一方面,確保其他正常工作的模塊不受影響。此外,還需增加異常檢測電路,發現異常即可對電路進行復位。

雖然上述方法可以很好地防護單粒子翻轉效應,但是也給邏輯綜合、布局布線帶來很多困擾,在芯片物理實現過程中需要小心謹慎應對。除上述方法外,還可引入Muller C單元、雙互鎖存儲單元結構(DICE)對晶體管級電路進行防護,也可在版圖階段使用環形柵替換條形柵。

▍總結

為何毅力號繼續使用主頻僅有233MHz的PowerPC 750處理器?網友認為233MHz已經足夠飛行控制部分,這也是最重要的部分。而多媒體、通信肯定用的高端cpu,多系統備份。復雜度越高可靠性是下降的,航天器主要考慮的還是可靠性問題,芯片性能并非第一位,輻射是航天級芯片需要面臨的最重要問題。那么,你認為如何呢?

更多信息可以來這里獲取==>>電子技術應用-AET<<