在一般工業中,可制造性設計(Design for Manufacturability,DFM)是指一套應用于產品設計階段的方法,其在設計的早期階段,就考慮產品制造過程中的困難、要求和約束等,使得最終產品具有良好的可制造性和成品率,能以最低成本、最短時間、最高質量被制造出來。

在集成電路中,DFM主要是針對集成電路制造工藝面臨的嚴峻困難,通過前段和后段的設計手段來部分解決或緩解工藝制造的困難,提高電路制造后的功能成品率(FuncTIonal Yield)和參數成品率(Parametric Yield)。

隨著集成電路工藝進入納米尺度,集成電路制造面臨日益嚴重的挑戰。例如,采用193nm波長光源的亞波長光刻導致硅片圖形嚴重畸變,化學機械拋光工藝導致互連線在高度方向發生嚴重偏差,工藝擾動的影響日益嚴重等。

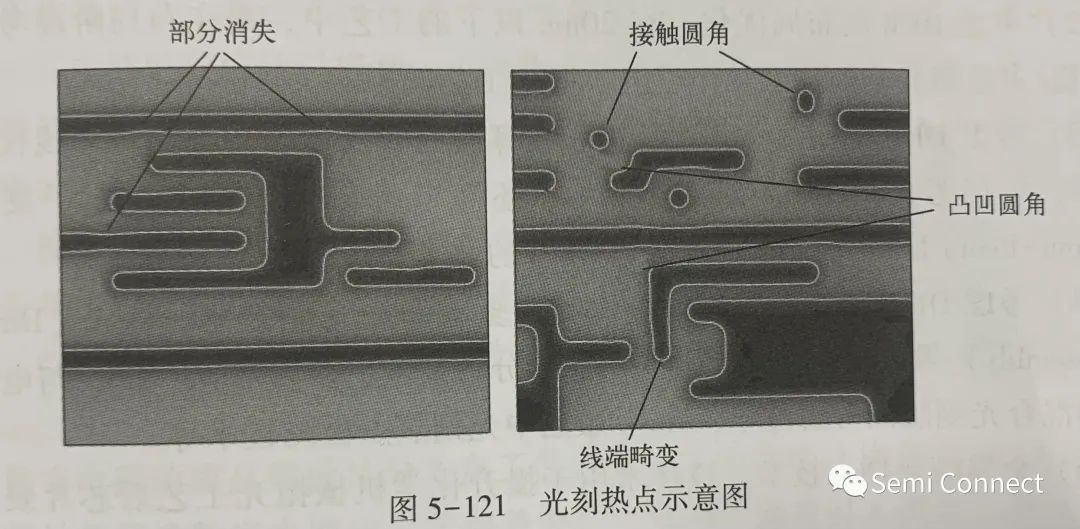

在亞波長光刻工藝中,即使采用分辨率增強技術(ResoluTIon Enhancement Technology,REF)后,光刻中依然容易在互連線頂端和拐角處出現“圓角”形變(Round-off),在線段中出現部分消失(ParTIal Disappearance)等畸變現象,如圖5-121所示。這些可能產生畸變圖形的設計版圖(Pattern)稱為光刻熱點,在設計時應盡量避免此類圖形,而在流片前要用光刻熱點檢查工具進行徹底排查。

金屬啞元插入(Dummy Filling)對化學機械拋光(Chemical Mechanical Polishing,CMP)工藝后芯片表面形貌影響如圖5-122所示。插入金屬啞元后,芯片表面平整性明顯優于插入啞元前。但引入金屬啞元會增加寄生電容,降低電路性能。因此,在芯片哪些位置插入啞元、插入多少啞元、確定啞元形狀等是啞元填充工具需要解決的關鍵問題。上述光刻熱點檢查和金屬啞元插入技術均屬于常見的DFM技術。

總體而言,DFM技術是針對傳統設計流程的擴充和優化,其通常包括如下技術。

(1)考慮DFM的標準單元設計技術。該技術不僅需考慮標準單元本身的可制造性,而且應考慮相鄰單元邊界附近光刻的相互影響。在考慮DFM的標準單元綜合技術中,除需滿足傳統設計規則外,還需兼容大量新增的DFM設計規則;甚至為提高成品率,標準單元行間隙(Line-Gap)也需進行優化。為了兼容多重曝光和自對準雙重曝光等新的光刻工藝,滿足日益緊張的布線通道約束,輸入/輸出的位置(Pin Access )也需進行仔細優化。

(2)考慮DFM的布局優化。在20nm以下的工藝中,需在布局階段考慮雙重/三重/多重曝光光刻技術和化學機械拋光工藝的影響。

(3)考慮DFM的布線優化。傳統布線算法一般僅考慮布通率、總線長等優化目標,而在考慮DFM的布線優化中,還需考慮與多重曝光、電子束光刻(Electron-Bean Lithography)等新光刻技術的兼容性。

(4)考慮DFM的掩模版優化。例如,多重曝光光刻技術、DSA(Directed Self-assembly)等新光刻工藝中的版圖圖形分解技術、多重曝光、DSA與電子束光刻的混合光刻版圖分解技術、Mask版圖中光刻熱點檢測技術等。

(5)金屬啞元插入技術。該技術用于提升化學機械拋光工藝后芯片表面的平整性。

(6)冗余通孔技術(Redundant Via)。該技術用于提升通孔的可靠性。

當集成電路進入納米尺度后,部分DFM技術已進入芯片代工廠(Foundry)的參考設計流程(Reference Flows)中,是設計者必須考慮的設計環節之一。在可見的未來,DFM技術會隨著新的制造工藝和設計技術的出現而不斷擴充和發展。集成電路設計者需在具有DFM功能的電子設計自動化(Electronic Design AutomaTIon,EDA)工具的協助下,在設計階段充分考慮工藝制造中的困難,這樣才能有效提升流片后芯片的成品率。

更多信息可以來這里獲取==>>電子技術應用-AET<<