0 引言

最近準備采用Xilinx FPGA進行多機通信,即主FPGA芯片將采集到的不同層的圖像數據流分別輸出給對應的4塊從FPGA芯片中,主從FPGA之間的連接機制采用星形拓撲結構。經計算,圖像數據流接口速率需要數百兆比特/秒,因此需要調研FPGA支持的常見IO接口標準,及每種接口的應用場合。

1 常見IO接口標準

Xilinx FPGA提供和支持高性能、可配置、多樣化的接口標準。主要的可配置屬性為On-chip terminaTIon(輸入端/輸出端的內置片上端接電阻),output strength(輸出驅動器的電流驅動能力),slew rate(電壓壓擺率)等。

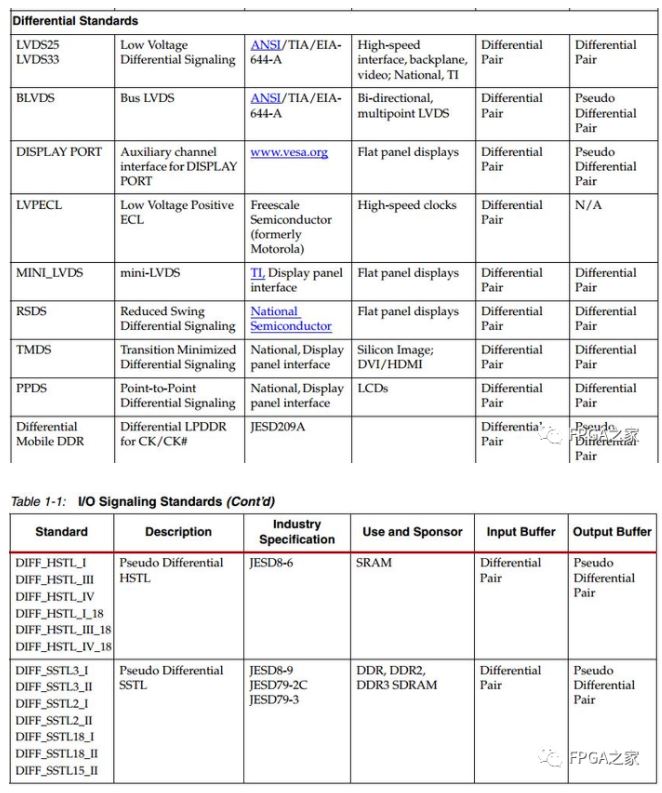

常見IO接口可分為單端IO接口和差分IO接口,詳細的IO標準參見下圖1。單端IO接口和差分IO接口均滿足高速接口傳輸,區別在于應用場合不同。

Xilinx FPGA芯片不同的Bank支持的IO接口標準范圍略有所不同,但是同一Bank必須使用同一output drive voltage (VCCO)。

1.1 端接電阻

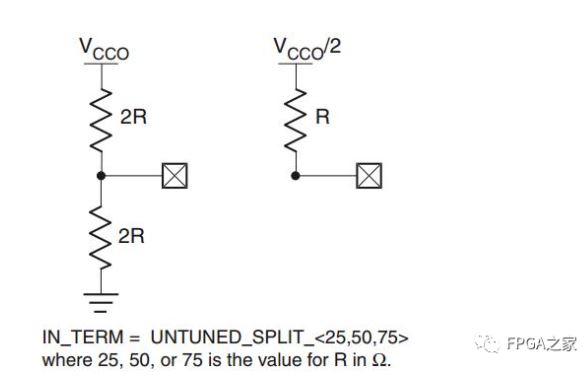

由上圖2可知,當使用高速IO接口時,在接收端通常需要匹配的端接電阻,有利于高低電平的轉換和提高信號的完整性,且端接電阻盡可能的放置在接收端。

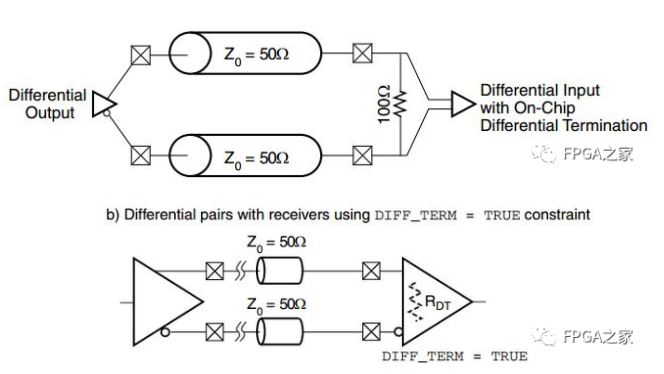

(a)差分輸入端接電阻

通常需要在差分輸入端并行端接100Ω的電阻,FPGA在差分輸入接收器提前內置了端接電阻,其阻值R為100Ω,為可選項opTIonal。設計者也可以采用外接端接電阻來進行電阻匹配,阻值選擇更靈活。采用片上內置的端接電阻可以節省無聊和縮小PCB面積。

通過UCF文件進行約束,是否使用差分輸入端接電阻,語法規則如下:NET DIFF_TERM = “” 。

(b)單端輸入端接電阻

由上圖可知,一些單端IO接口也需要輸入端接電阻來匹配信號的完整性,例如HSTL,SSTL。SSTL電平通常應用在DDR SRAM中,例如SSTL18應用在DDR2,SSTL15_II應用在DDR3中。詳見下圖所示。

通過UCF文件進行約束,是否使用單端輸入端接電阻,語法規則如下:

NET IN_TERM = ;

(c)輸出端接電阻

由上圖可知,輸出端(也稱為源端)也可以配置輸出端接電阻,以減少信號的反射,應用在高速單端信號場合,例如FPGA輸出驅動DDR3芯片。輸出端接電阻也是opTIonal可選項,常見阻值R為none,25Ω,50Ω,75Ω。通過UCF文件進行約束,是否使用單端輸出端接電阻,語法規則如下:

NET OUT_TERM = ;

說明:由上圖可知,FPGA作為輸出端,其端接電阻可以通過內置端接電阻配置完成,但如果DDR SRAM作為后一級的輸入端,該芯片沒有片上端接電阻,故需要外接50Ω的輸入匹配電阻。

1.2 設置IO接口屬性

常見IO接口屬性包括:電平標準,輸出壓擺率,輸出驅動能力,上/下拉。詳細設置參考下文。

2 常見IO接口標準&應用

當今大廠家會基于其IO接口的總線應用場合提出新的IO接口標準,隨后被其他廠家所使用。每一種IO接口標準均有其特有的電壓、電流、輸入輸出緩沖和端接匹配技術要求。Xilinx User Guide詳細列出了常見的各種IO接口的種類,定義及應用場合,詳見下文。

3 高速IO接口應用舉例

基于FPGA的高速IO接口應用的常見例子有兩種,詳見下文。

第一種: 采用SSTL15_II接口標準,應用于DDR3 SRAM,屬于single-end IO standard;

第二種:采用LVDS33/25接口標準,應用于IOSERDES的高速串行通信,屬于differenTIal IO standard;

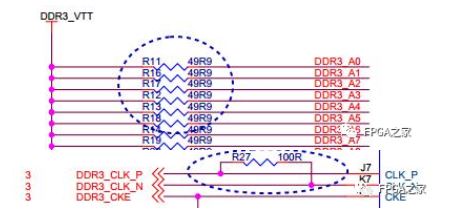

3.1 DDR3 SRAM接口驅動

FPGA驅動DDR3 SRAM芯片時,FPGA作為輸出源端,SRAM芯片作為終端,故FPGA需要配置output driver 的相關屬性參數attributes。SRAM作為input receiver,需要進行端接電阻匹配,由于沒有內置片上端接電阻,故需要在SRAM輸入管腳外接匹配電阻,由于數據端口是雙向端口,故輸入端是高阻狀態,無需匹配。而地址總線接口和差分時鐘輸入接口需要匹配對應阻值的電阻。

(a)FPGA輸出端IO Standard在UCF文件中參數配置如下:

NET “mcb3_dram_dq[*]” IOSTANDARD = SSTL15_II | IN_TERM = NONE | OUT_TERM = UNTUNED_50;

壓擺率和上下拉采用默認參數,SLOW slew rate, 12mA output drive。

(b)SRAM輸入端IO standard,地址管腳和數據管腳盡可能均勻分配在某一個或多個Bank中。

地址總線輸入端(單端接口)需匹配50Ω端接電阻,差分時鐘輸入端(差分接口)需要匹配100Ω的端接電阻,見下圖所示。

地址總線輸入接口

差分時鐘輸入接口

說明:1. SRAM輸入管腳的端接電阻盡可能靠近管腳,以保證信號的完整性;

2. 每一組bank均有獨立的Vcco和Vref,便于配置variable IO standard;

3. 為減少SSO(simultaneous switching output)的大量輸出管腳電平同一方向切換的干擾,可以增加virtual

VCC/GND pins,即將該bank未用到的管腳在FPGA程序中設置為GND或VCC;

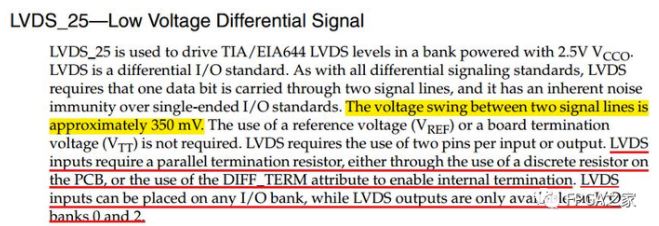

3.2 LVDS差分IO接口驅動

LVDS:低壓差差分信號,每位數據需要一對差分信號線,相較于單端接口,差分接口可以抑制共模噪聲,電壓擺幅約350mV,因此信號傳輸功耗較低。LVDS接口傳輸速率上限可達3.125Gbit/s,如果配合相應的編碼規則(如8b/10b)和使用SERDES技術,可以保證常用高速信號通信。

差分信號輸入端需要端接匹配電阻,如果輸入端為FPGA管腳,可以通過配置,使能其內置端接電阻,阻值默認為100Ω。UCF配置LVDS接口如下:

說明:1. 壓擺率越快,電平轉換時間越短,時間性能越優;

2. Spartan6 FPGA所有Bank均支持LVDS差分輸入,但只有Bank0和Bank2支持LVDS差分輸出;

更多信息可以來這里獲取==>>電子技術應用-AET<<