在為超越半導體的物理限制而開發的大量替代計算方法中,量子計算仍然是一個突出的研究領域,頂尖大學和大型科技公司都在致力于實現該技術所承諾的能力和性能實現。

在本文中,我們將研究來自著名大學和研究機構的三篇科學論文。這些論文的共同點是克服這些問題并進一步擴展量子處理器的目標。

傳輸半導體量子比特

亞琛工業大學和德國Jülich 研究所的物理學家致力于研究一種增加量子處理器內量子比特數量的新方法,并于2022年 9 月發表了他們關于開發量子信息攜帶粒子的穩定傳輸過程的發現。

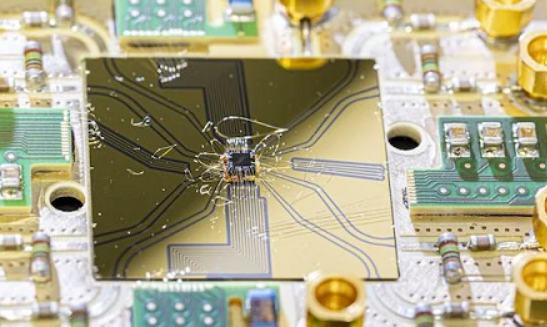

這里展示的是帶有量子總線的半導體量子芯片,這是 Jülich 研究所和亞琛工業大學 JARA 合作的成果。

使用硅和鍺自旋量子位(基于電子和電子空穴自旋的量子位),由Lars Scheiber 博士領導的團隊能夠創造出一種“量子總線”,能夠在 560 nm 的距離內傳輸電子 5,000 次而不會遇到任何重大錯誤。

與其他需要精確的信號調整和復雜的控制電子的引導電子的方法相反,亞琛工業大學和尤利希團隊提出的方法實現了一個簡單得多的系統,只使用四個正弦波作為控制信號,產生一個電勢波,根據科學家的說法,電子可以簡單地“越過”干擾。

雖然減少干擾解決了量子計算中最大的挑戰之一,但Scheiber博士的團隊尚未在實踐中證明,他們的量子比特在傳輸后仍能保留電子自旋編碼的數據,但他們的理論計算證明,在特定的電子速度范圍內使用硅是可能的。

作為歐洲 QuantERA 聯盟的一部分,“量子總線”目前是十多項已申請專利的基礎,顯示出可喜的成果,因為它可能是一次連接和控制數百萬量子比特的關鍵,而不需要目前量子計算機設計所依賴的大規模基礎設施。

增加互連自旋量子位的數量

早在 去年9 月,代爾夫特理工大學量子計算研究所 QuTech 的一組科學家就宣布了他們在開發一種用于縮放量子處理器的新型硅基方法方面的發現。

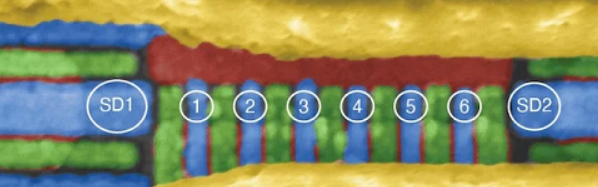

由Lieven Vandersypen 教授領導的團隊使用間隔 90 納米的電子基量子點陣列創建了一個六自旋量子比特硅芯片,形成了非常類似于傳統半導體晶體管的形狀。

六量子比特量子處理器的圖像。量子比特是通過調整芯片上紅色、藍色和綠色電線上的電壓來創建的。圖片由QuTech提供

根據該研究論文,這種結構可以使用微調的微波輻射、磁場和電勢來控制,以在單個量子位上讀取和寫入信息,并使它們相互作用并創建量子邏輯門和兩個糾纏系統或每個三個電子。

通過這樣做,Lieven Vandersypen 教授的芯片在通用操作、狀態準備和量子位測量方面實現了可觀的保真度,同時與其他架構相比降低了錯誤率,這是朝著創建基于硅的容錯量子計算機邁出的寶貴一步。

這項研究與其他研究的不同之處在于,QuTech 團隊能夠在使用熟悉的半導體制造方法生產的芯片上增加量子比特數的同時保持精度,這與需要復雜得多的基礎設施開發的超導量子計算機相反。

擴展受量子啟發的處理器

該領域的另一項突破來自東京理科大學 (TUS)。由Takayuki Kawahara 教授領導的研究團隊正在研究一種新方法,該方法于 去年9 月宣布,旨在開發一種可擴展且完全耦合的量子啟發設備。這種設備簡稱為退火處理器或退火機。

雖然退火機不一定能利用粒子的量子特性,但通過模擬Ising模型的行為(換句話說,描述相互作用的磁鐵的自旋),它能夠有效地解決投資組合、物流和交通流優化等問題。

Kawahara教授的架構采用28納米CMOS邏輯(模擬退火而不是量子退火,如D-Wave的量子退火器研究)開發,并具有512個全耦合自旋,于2020年在IEEE SAMI會議上首次提出,盡管當時這個設計由于各個旋轉之間的互連數量,難以擴展。

現在,該團隊設計了一種新方法,將系統能量狀態的計算分配給多個芯片陣列,然后由控制芯片收集,形成最終能量結果,用于更新模擬自旋的值。

TUS 研究人員提出了一種完全連接的可擴展退火處理器。該方法使用由多個耦合芯片和一個控制芯片組成的陣列計算器。圖片由東京理科大學提供

這使得該研究小組能夠開發出該系統的新版本,即384個自旋的FPGA實現,根據他們的測試,與CPU模擬相比,該系統能夠以584倍的速度解決優化問題,并且能效提高46倍。

Kawahara 教授希望進一步研究并創建定制LSI芯片,以提高其方法的容量、性能和效率,希望改進需要解決復雜優化問題的領域,例如藥物研究和材料科學。

這一切對未來意味著什么?

顯然,2022 年為量子計算帶來了積極而充滿希望的音符。雖然開發具有數百萬而不是少數量子比特的量子處理器還有很長的路要走,但本文涵蓋的研究為解決困擾該領域的一些最大挑戰的新想法鋪平了道路。

研究電子傳輸、開發容錯自旋量子比特系統以及通過使用傳統電子學模擬量子結構,可能是繞過量子力學定律所提出的限制的關鍵,并將量子計算機帶出實驗室,帶入現實世界,解決復雜的現實世界問題。

更多信息可以來這里獲取==>>電子技術應用-AET<<