7 月 23 日消息,微電子標準制定方 JEDEC 固態技術協會當地時間 22 日宣布,DDR5 MRDIMM 和 LPDDR6 CAMM 內存技術規范即將正式推出,并介紹了這兩項內存的關鍵細節。

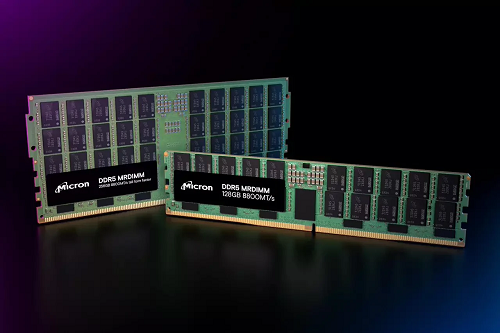

DDR5 MRDIMM 中的“MR”即 Multiplexed Rank(多路復用列),這意味著該內存支持兩個或以上的 Rank(列),并可在單個通道上組合和傳輸多個數據信號,無需額外的物理連接就能有效提升帶寬。

JEDEC 規劃了多代 DDR5 MRDIMM 內存,目標最終將其帶寬提升至 12.8Gbps,較 DDR5 RDIMM 內存目前的 6.4Gbps 翻倍。

在 JEDEC 的設想中,DDR5 MRDIMM 將利用與現有 DDR5 DIMM 相同的引腳、SPD、PMIC 等設計,與 RDIMM 平臺兼容,并利用現有的 LRDIMM 生態系統進行設計與測試。

此外 JEDEC 還規劃了 Tall MRDIMM 外形尺寸。正如其名,這一設計將采用更高的外形尺寸,使其支持的 DRAM 封裝數量翻倍,可進一步提升內存容量。

▲ 美光 MRDIMM 內存產品,左側為 Tall 版

而在 LPDDR6 CAMM 方面,JEDEC 表示預計將實現 14.4GT/s 以上的最大速度,同時將提到 24bit 位寬子通道、48bit 位寬通道并支持“連接器陣列”(注:原文為 connector array)。

本站內容除特別聲明的原創文章之外,轉載內容只為傳遞更多信息,并不代表本網站贊同其觀點。轉載的所有的文章、圖片、音/視頻文件等資料的版權歸版權所有權人所有。本站采用的非本站原創文章及圖片等內容無法一一聯系確認版權者。如涉及作品內容、版權和其它問題,請及時通過電子郵件或電話通知我們,以便迅速采取適當措施,避免給雙方造成不必要的經濟損失。聯系電話:010-82306118;郵箱:[email protected]。