摘 要: 從分析人工神經網絡" title="人工神經網絡">人工神經網絡的設計原理入手,闡述了全數字" title="全數字">全數字電路人工神經網絡的設計方法。通過一個小規模前饋人工神經網絡的設計實例,簡要說明了利用VHDL語言及編譯平臺,完成一種可調整權值" title="權值">權值的通用人工神經網絡的設計算法和流程。

關鍵詞: 人工神經網絡 VHDL 數字電路

人工神經網絡(ANN)是一門起始于19世紀90年代,復興于20世紀80年代的綜合性學科,涉及生物、電子、計算機、物理等多種學科,有著非常廣泛的應用前景。長期以來,人們都在想方設法了解人腦的功能,用物理可實現系統去模仿人腦的神經網絡。其實現方法是多種多樣的,總的來說可分為兩種:一種是利用現代高性能的計算機形成具有模擬能力的通用軟件來完成神經網絡的預期功能;另一種是利用硬件直接實現神經網絡,如模擬VLSI 實現、數字VLSI 實現、模數混合VLSI 實現。

迄今為止,人們利用C、Basic等高級語言開發了很多神經網絡軟件包,實現了許多算法和模型,但是用軟件模擬的神經網絡并不能達到真正的并行處理,且對計算機性能要求很高;硬件實現中的模擬VLSI,雖然速度快和集成度高、便于實現非線性運算,但精度低、對噪音和溫度的變化非常敏感、設計復雜、突觸權值存儲困難;而硬件實現的數字VLSI,雖然免疫力強、速度快, 但是部件(如乘法器" title="乘法器">乘法器) 占芯片面積大[1]。不過,隨著大規模集成電路和HDL語言的不斷發展,數字VLSI設計日益成熟,EDA設計工具的不斷更新換代,使得全數字電路ANN的實現工藝難度越來越小,集成度和可靠性越來越高;同時FPGA的現場可編程特性,又使得ANN的調整更加方便快捷,因而數字VLSI逐步成為ANN實現的發展主流。本文通過一個小規模前饋ANN的設計實例,簡要說明利用VHDL以及QuartusII編譯平臺完成一種可調整權值的通用ANN的設計算法和流程。

1 人工神經網絡的實現原理

人工神經網絡就是采用物理可實現系統模仿人腦神經細胞的結構和功能的系統[2]。它把很多處理單元有機地連接起來形成網絡,進行并行的工作;通過模擬生物神經細胞發出信息脈沖,控制網絡的運行。神經細胞單元的信息是寬度和幅度都相同的脈沖串" title="脈沖串">脈沖串,而脈沖串的間隔則是隨機變化的。例如某個神經細胞單元興奮,其軸突輸出的脈沖串的平均頻率就高;若細胞單元不興奮,則脈沖頻率就低甚至沒有脈沖。多個神經細胞單元的軸突脈沖可以加權,形成細胞單元的電位變化,電位變化累加超過一定閾值,就產生一個脈沖,通過控制閾值大小,就可以控制脈沖。人工神經元的示意圖如圖1所示。

圖中,x1…xn表示其他神經元的軸突輸出脈沖,ω1…ωn為其他神經元與第i個神經元的突觸連接,ωi可正可負,分別表示興奮和抑制,則:

在式(1.1)中,si表示神經元i突觸后的累加值,θi為閾值。在式(1.3)中,vi為神經元i的狀態,yi為神經元i的輸出,它是一個單調上升的函數,且為有限值,這是由于生物體中神經元脈沖發放率有一個最大值,不能無限上升的緣故。

總之,人工神經網絡由很多幾乎相同的單元組成,這些神經元的輸入與輸出的函數關系為單調上升的非線性關系,它們之間的連接采用權的辦法實現,每個神經元的輸入是其他神經元輸出的加權和,因此在電路實現中需要完成:

(1)實現神經元輸入與輸出的線性關系。

(2)實現兩個信號的相乘。在神經網絡中權的數量很多,加權的計算都用乘法完成,因此對應于兩個信號相乘的電路必不可少。

(3)實現加權后脈沖累加。

2 一種前饋人工神經網絡的全數字電路模型

在全數字電路組成的人工神經網絡中,乘法是利用與門進行的。如圖2所示,兩個脈沖序列通過“與”以后的輸出即為二者的乘積;兩個脈沖序列的占空比為1/2和1/3,相“與”后,脈沖序列的占空比為1/6,從而達到相乘的目的。

?

權存儲在寄存器中,寄存器可以與外界的計算機內存或EPROM相聯,因而權可從外面寫入。這意味著權的存儲和權的改變沒有什么困難,可以設計出可重構的人工神經網絡模型。

累加器是用計數器完成的,從乘法器輸出的脈沖串經過計數器實現累加,當累加到達閾值時即作為神經元的一個狀態輸出。

圖3給出了一個簡單的前饋人工神經網絡的結構示意圖[3]。圖中,xi代表第i個輸入,wij代表輸入i與神經元j之間的權值,yj是第j個神經元的輸出。則:

式中, f( )是激化函數(如線性閾值的sigmoid的函數)。

根據ANN的設計實現原理,可以把圖3所示的網絡結構設計成如圖4所示的數字電路結構。

?

圖4中,每個矩形框內部的電路構成一個神經元,在垂直方向上有幾組移位寄存器,在水平方向上有個大的環形結構。垂直的環形移位寄存器存儲著前面所有的權值,水平環行移位寄存器中裝載的是輸入信號。每個權值在自己的移位寄存器中的相對位置必須和輸入值匹配。在每個垂直的環形移位存儲器輸出端有一個乘法器/累加器電路,用于對權值和輸入信號進行乘-累加運算。運算的結果送給查找表(LUT),用于實現激化函數,得到輸出yi。

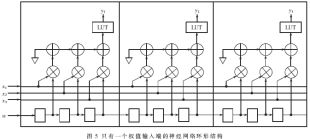

這個電路只用到了三個乘法器,有效地節省了資源。但是各個權值單獨輸入,不便于外部調整,不適于通用人工神經網絡的編程。為此,設計如圖5所示電路。圖中,只使用一個輸入端口加載所有的權值,權值按照順序移位,直到每個寄存器都存儲相應的權值,然后權值與輸入相乘并累加,最終得到期望的輸出結果。

3 VHDL語言的編程實現

為了使設計具有通用性,按照圖5的結構用二維數組表示輸入和輸出,并自定義一個程序包,用來定義數組的數據類型:verctor_array_in和vector_array_out。由于程序包中的參數是通用的,可被多個實體即電路塊調用,因而大大地提高了設計效率。

人工神經網絡設計權值通用程序包如下:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

use ieee.std_logic_arith.all;

package currency_data_type is

constant b:integer:=3;——輸入位數或者權重,改變b的值,可以調整網絡的規模和大小

type vector_array_in is array(natural range〈〉) of signed (b-1 downto 0);

type vector_array_out is array(natural range〈〉) of signed (2*b-1 downto 0);

end currency_data_type;

同時,將輸入位數、神經元的數目以及每個神經元的權重等參數放入類屬說明中,由設計實體即設計電路外部提供,因而設計者可以根據需要方便地調整網絡的結構和規模。

具體程序如下:

ENTITY dann IS

generic(n: integer :=3;——加入類屬說明,可從外部通過類屬參量重新設定電路規模

m: integer :=3;

b: integer :=3);

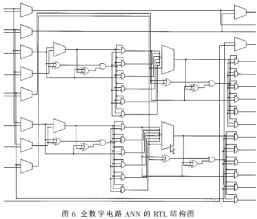

編寫完的程序經過編譯綜合,便可得到如圖6所示的門電路。

4 仿真分析

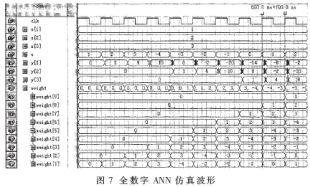

經過QuartusII對程序綜合編譯之后,還需要對電路進行波形仿真,以檢驗設計的正確性和程序的實用性。波形仿真如圖7所示。

為了觀測方便,在仿真時把輸入信號固定為x1=1,x2=2,x3=3,時鐘周期為10MHz。程序中共有九個權值,需要九個時鐘周期來移入。因此到第9個周期的時候,由圖7可知,權值weight[1..9]分別為[0,-1,-2,-3,-4,3,2,1,0],則輸出為:

由于選用的FPGA器件不同,芯片內部產生延遲,導致波形中毛刺出現,但相對于模擬電路,精度和穩定性仍有很大的提高。在實際的系統設計中,可以根據需要并結合成本考慮選擇恰當的芯片下載。

?

通過上面的設計,不難發現,數字電路在權值累加和非線性函數的計算上比較麻煩,綜合編譯的時候,數字乘法器占用的資源巨大,尤其是隨著神經元和輸入位數的增加,成平方倍增長。但是,以一套較好的EDA工具為平臺,使用VHDL語言從頂至下設計全數字電路的人工神經網絡,不僅能夠避開電路搭配的繁瑣,縮短設計周期,提高設計效率,而且由于FPGA器件的現場可編程特性,可以靈活控制網絡的規模和結構,設計出可通用的網絡模型,大大節省了開發周期,延長了設計壽命。

參考文獻

1 Keulan E et al. Neural network hardware performance criteria.In:Proc of the IEEE Conf on Neural Networks,Vol. Florida,1994. 1885~1888

2 張立明. 人工神經網絡的模型及其應用.上海:復旦大學出版社, 1993:3~4

3 喬廬峰(譯).VHDL數字電路設計教程.北京:電子工業出版社, 2005:243~250

4 潘 松.VHDL實用教程.成都:電子科技大學出版社,2000

5 羅 莉. 數字神經元芯片的設計與應用.計算機研究與發展, 1998:798~802