引言

便攜式MP3播放器作為一種集音頻播放、數(shù)據(jù)存儲(chǔ)為一身的數(shù)碼產(chǎn)品,其功能結(jié)構(gòu)為電子設(shè)計(jì)人員所津津樂道。新功能的MP3播放器不斷地更新?lián)Q代。為了滿足MP3播放器功能新增的需求,我們設(shè)計(jì)了一套基于CoolRunner CPLD的軟硬件開發(fā)系統(tǒng),制作相應(yīng)開發(fā)板,探索了一種快速實(shí)現(xiàn)的方案。

MP3應(yīng)用開發(fā)板的選型和設(shè)計(jì)

主控模塊芯片及其外圍器件

XCR3256是Xilinx公司開發(fā)的CoolRuner CPLD芯片,可實(shí)現(xiàn)6000門的數(shù)字邏輯電路,內(nèi)嵌256個(gè)宏單元,支持4個(gè)全局時(shí)鐘,具有低功耗、可快速ISP、延時(shí)可預(yù)測等特點(diǎn),可滿足MP3功能和數(shù)碼產(chǎn)品方面的一些特殊要求,我們選用XCR3256芯片實(shí)現(xiàn)M P3主控模塊。該主控模塊用于對各外圍器件的控制,協(xié)調(diào)各外圍器件的工作。外圍器件主要有解碼芯片組(MAS3507D和DAC3550A)、Flash存儲(chǔ)器、LCD、USB接口、并口等。主控模塊與各外圍器件的框圖如圖1所示。

圖1 MP3應(yīng)用開發(fā)板結(jié)構(gòu)框圖

主控邏輯單元是整個(gè)主控模塊的核心部分,決定著MP3播放器各功能,如播放、快進(jìn)、下載之間的優(yōu)先度和順序,為其他邏輯單元提供實(shí)現(xiàn)更加復(fù)雜操作的控制信號。主控邏輯單元通過狀態(tài)機(jī)對其他模塊進(jìn)行控制,其狀態(tài)機(jī)如圖2所示,該圖詳細(xì)地描述了MP3播放器不同工作階段的操作條件和各階段之間的切換情況。

特別需要說明的是:①LOW_PWR使DAC3550A工作在低功率模式下;②IDLE是播放與下載、快進(jìn)、后退等操作之間的轉(zhuǎn)換狀態(tài);③UPDATE_TRACK將歌曲曲目更新,并傳遞給LCD顯示。

圖2 主控邏輯單元狀態(tài)機(jī)

DAC3550A是一款專為音頻應(yīng)用而設(shè)計(jì)的高精度數(shù)模轉(zhuǎn)換芯片,具有低功耗操作模式,連續(xù)采樣頻率從8KHz到50KHz均可自主選擇,這就給設(shè)計(jì)帶來了極大的靈活性;還提供了簡潔的I2S總線接口和I2C總線接口,主控模塊正是通過I2C總線對DAC3550A三個(gè)寄存器AVOL(16bits)、GCFG(8bits)、SR_REG(8bits)寫入相應(yīng)命令而實(shí)現(xiàn)控制的。DAC3550A接口電路圖設(shè)計(jì)如圖3所示。

圖3 DAC3550A接口電路圖

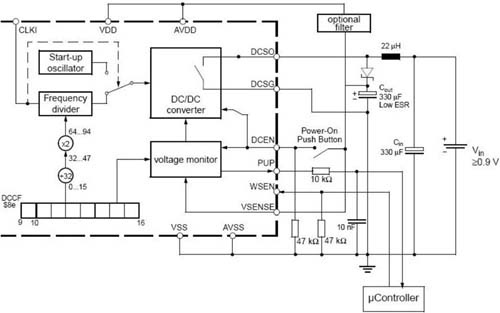

MAS3507D可實(shí)現(xiàn)2階或3階的MPEG音頻解碼功能,內(nèi)嵌的功率管理器可降低低采樣頻率時(shí)的功率,并可以在芯片閑置時(shí)將其暫時(shí)斷電(power off)。該芯片還可以對音效進(jìn)行調(diào)整,以滿足用戶不同需求;為輸出音頻數(shù)據(jù)而提供的I2S總線端口使MAS3507D和DAC3550A的連線更加簡潔方便。MAS3507D是通過給主控模塊的反饋實(shí)現(xiàn)對DAC3550A輸入控制的,MAS3507D DC/DC轉(zhuǎn)換接口電路如圖4所示。

圖4 MAS3507D DC/DC轉(zhuǎn)換接口電路

開發(fā)板工作流程

MP3應(yīng)用開發(fā)板的工作流程為:

上電→提取用戶命令→讀存儲(chǔ)器→將MP3音頻文件送至MAS3507D進(jìn)行解碼→解碼后的數(shù)字信號經(jīng)DAC3550A數(shù)模轉(zhuǎn)換→模擬信號輸入耳機(jī)。

性能設(shè)計(jì)

設(shè)計(jì)過程中,為滿足今后功能擴(kuò)展及增強(qiáng)開發(fā)平臺系列化的需要,我們對開發(fā)板的功能布局做了很多調(diào)整。

我們將CoolRunner芯片與解碼芯片組連接的引腳設(shè)計(jì)成插針形式,可及時(shí)更新和選用新的解碼芯片組,而解碼芯片組決定著MP3播放器所能播放音頻文件的格式及音質(zhì)。低功耗是MP3播放器追求的一項(xiàng)重要指標(biāo),開發(fā)板中選用的XRC256XL芯片及解碼芯片組(MAS3507D和DAC3550A)均滿足了低功耗的要求。

布線要點(diǎn)

MP3應(yīng)用開發(fā)板的設(shè)計(jì)軟件我們選用ProtelDXP。在布線時(shí),我們注意到一些問題,如I2C總線在高電平時(shí)對串?dāng)_和干擾的高度敏感性要求在總線或帶狀傳輸線超過10cm并且包含VDD和VSS時(shí),布線必須按SDA、VDD、VSS和SCL從上到下的順序進(jìn)行;對MAS3507D和DAC3550A之間負(fù)責(zé)數(shù)據(jù)傳輸?shù)腎2S總線應(yīng)盡量減少布線長度,并且避免周圍信號線的干擾。

MP3應(yīng)用開發(fā)板的調(diào)試

我們設(shè)計(jì)了一個(gè)描述MP3主控模塊的IP Core,特別注意到了USB端口的下載功能及歌詞與音頻的同步顯示功能。

調(diào)

試環(huán)境

仿真和綜合過程中,我們使用的EDA工具有:Xilinx公司開發(fā)的ISE 6.2,Synplicity公司的Synplify Pro7.3以及Mentor Graphics公司的Modelsim SE5.7e。

調(diào)試流程

關(guān)鍵的測試流程如下:

(1)在ISE6.2下將修改后的IP Core編譯通過,編寫測試文件。用Modelsim SE5.7e進(jìn)行功能仿真。該測試文件比較全面地考慮了實(shí)際情況,例如對I2C總線的數(shù)據(jù)線SDA和時(shí)鐘線SCL增加了上拉模塊PULLUP,以模擬實(shí)際中上拉電阻對I2C總線的上拉作用。該測試文件很好地模擬了主控模塊對各外圍器件的控制,全面反映了開發(fā)板的工作情況,并且是在硬件制作完成之前就對主控模塊進(jìn)行功能和時(shí)序上的仿真驗(yàn)證,除了證明了源代碼功能上的正確性和時(shí)序上的精確性,同時(shí)還大大縮短了設(shè)計(jì)周期。

(2)調(diào)用Synplify Pro7.3對MP3主控模塊的源代碼進(jìn)行綜合,生成網(wǎng)表文件及布局布線約束文件等。

(3)利用ISE 6.2將網(wǎng)表中的邏輯符號門組裝到物理元件(CLB和IOB)中,并將元件放置到器件中進(jìn)行連接,同時(shí)提取出時(shí)序數(shù)據(jù)并生成各種報(bào)告。

(4)利用在布局布線中獲得的精確參數(shù)再次驗(yàn)證電路的時(shí)序,調(diào)用Modelsim SE5.7e進(jìn)行后仿真。

(5)燒寫驗(yàn)證。編寫UCF(User Constraints File)文件mp3.ucf,設(shè)置好全局約束、端口約束等,然后使用ISE集成的配置工具iMPACT,生成PROM格式的配置文件,再將其通過JTAG端口下載至自行設(shè)計(jì)成功的MP3應(yīng)用開發(fā)板。在MP3音頻文件被下載至FLASH存儲(chǔ)器后,就可以對該IP Core進(jìn)行調(diào)試。經(jīng)調(diào)試,我們所預(yù)期的功能如播放、快進(jìn)、后退、靜音等,均得到的實(shí)現(xiàn),表明調(diào)試成功。

結(jié)語

本文介紹了基于CoolRunner CPLD的MP3應(yīng)用開發(fā)板的設(shè)計(jì)流程,驗(yàn)證了利用現(xiàn)有IP Core設(shè)計(jì)的可行性和高效性。在設(shè)計(jì)過程中,硬件(實(shí)驗(yàn)評估板)的設(shè)計(jì)和基于IP Core的算法設(shè)計(jì)可同步進(jìn)行,避免了兩者因異步帶來的設(shè)計(jì)周期的延長。實(shí)踐證明本文的設(shè)計(jì)思路和實(shí)現(xiàn)方法是一種靈活、快速、可靠地開發(fā)數(shù)字系統(tǒng)平臺的設(shè)計(jì)方案。

參考文獻(xiàn):

1. 王誠,薛小剛,鐘信潮 FPGA/CPLD設(shè)計(jì)工具─Xilinx ISE5.x使用詳解,人民郵電出版社,2003.

2. 金西 VHDL與復(fù)雜數(shù)字系統(tǒng)設(shè)計(jì),西安電子科技大學(xué)出版社, 2003.