高速串口數據通信在現代通信系統和控制系統中應用日益廣泛,較之傳統的基于RS232傳輸標準,具有更高的可靠性,更強的兼容性,更快的傳輸速率。

由于不同的串口數據通信采用的方式各不相同,有異步模式、同步模式,而且數據傳輸格式也各不相同,有的采用傳統SCI傳輸格式,有的采用自定義數據格式,有的采用幀長度固定方式,有的采用幀長度可變方式等,而且每一幀的數據長度可以從10bit到幾千bit,所以高速串口的設計要求不同其實現方案也不同。本文重點介紹基于SOPC(可編程系統芯片)的高速異步串口通信系統的設計方法。

目前的嵌入式處理器種類繁多。Altera 公司的Nios II處理器是用于可編程邏輯器件的可配置的軟核處理器,與Altera 的FPGA 組合,具有很高的性價比。

總體設計及系統架構

高速串口數據通信系統采用雙線平衡驅動,半雙工同步傳輸或單向廣播同步傳輸,線路傳輸速率為5Mbits/s,總線連接關系如圖1所示。

系統中主機模塊能調度總線上的數據幀收發,保持數據通信的實時性,數據傳輸時由主機模塊發送數據幀。數據幀若為半雙工同步傳輸幀,則數據幀只對其中一個外圍模塊有效,同時當外圍模塊收到數據后,應發送相應的應答信號;數據幀若為單向廣播同步傳輸幀,則數據發向所有外圍模塊,而不需要任何應答信號。

系統以固定的數據幀格式傳送數據,不同于傳統的SCI格式,幀長為7字節(共56bits),由2字節引導序列、1字節地址,3字節數據、1字節幀結束序列組成。幀的發送順序:字節內低位先發,多字節內低字節先發。

無論是主機模塊還是外圍模塊均采用相同的串口通信設計,串口通信設計包含兩個主要部分:通信接口部分和管理控制部分。通信接口部分主要完成數據幀結構的封裝和解封裝,并通過幀頭的分析識別進行時隙定位,同時能讓系統內的每一終端實現多機共享通信資源的通信機制,該模塊由VHDL語言實現。管理控制部分由NiosII軟核實現的,為了能在串行通信方式上實現時分復用,進而實現多設備同時通信,系統設計出一套完整而獨特的控制幀格式,并通過這些幀格式控制實現建立連接,撤銷連接和相應管理。因此,利用NiosII的特點,形成特殊的幀頭判決、同步時鐘提取、控制信息的判斷、收發模式變換,這些都依賴專用模塊的實施并靠高速執行速度來適應多終端下的高傳輸速率。

鑒于以上系統架構和設計要求,串口通信采用模塊化設計思路和方法,模塊結構如圖2所示。

NiosII軟核CPU開發工具SOPC Builder提供簡潔的操作方式,可將用戶的數字電路模塊封裝成標準的NiosII軟核外設模塊,這使得NiosII軟核可以很容易地與用戶邏輯結合,構成功能更加強大的SOC系統。在高速串口數據通信的設計中,既需要一個高速的處理器作為系統的控制管理核心,又有大量用戶自定義的數字電路功能模塊需要在FPGA芯片中實現,因此,采用FPGA芯片和NiosII軟核CPU作為高速串口數據通信的硬件平臺是一個優化的選擇。

通信接口模塊設計

通信接口模塊設計采用VHDL語言設計,由兩部分組成:數據幀發送電路和數據幀接收電路。數據幀發送電路將NiosII 要發送的數據、地址按照數據幀格式進行組幀,然后同步傳輸到總線上,該部分設計的關鍵是并串轉換、合并數據和同步控制,數據的發送率為5Mbits/s,而工作時鐘fclk為25MHz,對fclk進行5分頻,得發送時鐘ftxd為5MHz。當有數據要發送時,每一個即ftxd的上升沿到來時傳送數據,先發送幀頭2字節引導序列,即“1110011100111110”,然后發送串行數據。由于NiosII的內部數據寬度通常是32位,故將1字節地址和3字節數據由軟件將其合并成一組32位寬度的數據,合并時地址在低位,數據在高位,然后將要發送的32位數據緩存在一個32位寬度的矢量區間,引導序列結束后從低位到高位依次發送數據,即data[0]、data[1]……data[31],最后發送結束標志字節“1110011”,發送結束。

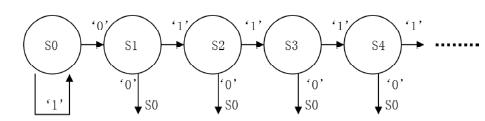

接收電路的設計重點考慮的問題是如何準確判斷到數據幀頭,然后解析地址,數據的速率為5Mbit/s,FPGA的工作時鐘fclk為25MHz,參考RS-232串口通信的設計思想,用高倍時鐘對接收的數據進行采樣,即每5個fclk采樣一個bit,此處可以先設計一個5進制計數器,每一次計數,保存采集的數據,在第2、3、4次采樣時,若所采到的值相同,則判斷這個bit為當前的采樣值。在判斷2字節引導序列時采用狀態機設計法和序列檢測器的設計思想,判斷第1個bit是否為‘0’,如果是‘0’則繼續判斷下一bit是否為‘1’,如果是‘1’則一直等待在第1狀態直到判斷到‘0’才跳轉,判斷狀態機如圖3所示。

用戶定義的Avalon總線模塊設計

NiosII是基于RISC技術的通用嵌入式處理器芯片軟內核,它特別為可編程邏輯進行了優化設計,也為可編程單芯片系統設計了一套綜合解決方案。Avalon總線是一種高效的總線結構,主要用于連接片內處理器NiosII和各種外設IP core,以構成可編程系統芯片(SOPC)。數據幀發送電路和數據幀接收電路通過Avalon總線和NiosII處理器連接在一起,Avalon總線規范定義了主端口和從端口之間通過Avalon總線模塊傳輸數據所需的信號和時序。設計時通信模塊采用從端口傳輸模式,數據幀發送電路采用具有外設控制等待周期的從端口寫傳輸模式,發送電路除串行數據輸出線外,還必須提供符合Avalon總線傳輸要求的信號線,即Address、Writedata(31..0)、Write_n、Chipselect、Waitrequest,與NiosII工作同步的時鐘信號clk,當CPU要發送數據時,將Address、Write_n信號有效,同時將要發送的32位數據裝載到Writedata(31..0)上,而同步時鐘clk一直處于工作狀態,當clk上升沿判斷到以上信號有效后,Avalon總線對Address譯碼,然后置Chipselect有效,而發送電路VHDL程序設計時必須判斷Address、Chipselect是否有效,如果有效,則在下一個clk上升沿前將Waitrequest置為無效,數據傳送電路就從Avalon總線獲取Writedata數據,如果Waitrequest有效,則這個總線周期就成為等待周期,其他信號以及數據信號保持不變,但外設必須保證不會使Waitrequest無限期地保持有效,這樣會使得一個從外設能夠將Avalon總線永久“掛起”,其連接關系和時序關系如圖4所示。同理,數據接收電路采用具有外設控制等待周期的從端口讀傳輸模式,可以將串轉并后的數據送入到NiosII中進行處理。

軟件設計

基于NiosII的C語言設計,可以采用單線程模式,也可采用uc/基于NiosII的C語言設計,可以采用單線程模式,也可采用uc/OSII多任務操作系統。這里對接收和發送的數據處理主要采用以下指令實現,“IORD(base, 1)”讀指令,其中base就是需要讀取的外設基地址,數據接收電路作為外設在建立SOPC Builder時定義的名稱為“user_uart_rxd”,則base應改為“user_uart_rxd_base”,而第2個參數‘1’表示其偏移地址;“IOWR(base, 1, data)”寫指令,其中base是需寫入外設基地址,數據發送電路作為外設在建立SOPC Builder時定義的名稱為“user_uart_txd”, 則base應改為“user_uart_txd_base”,而第2個參數‘1’表示其偏移地址,第3個參數data是發送數據。

計算機仿真波形如圖5、圖6所示。它們之間的時序關系參照本文的第二部分。

結語

運用此5Mbit/s的UART進行通信,效果十分穩定、可靠性高,傳輸速度快,采用RS485接口模式傳輸距離遠,同時不易被干擾以至出現誤碼、丟數據、丟幀等情況。因此采用SOPC嵌入式系統設計技術可以實現系統設計的小型化、集成化和高可靠性,還可以減少風險、降低成本、縮短開發周