引言

誤碼儀是評估信道性能的基本測量儀器。本文介紹的誤碼儀結合FPGA 的特點,采用全新的積分式鑒相結構,提出了一種新的誤碼測試方法,經多次測試驗證,方案可行,設計的系統穩定。本文設計的誤碼儀由兩部分組成:發信機和接收機。

1 發信機

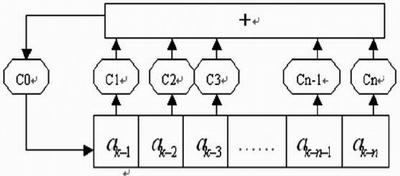

發信機的主要功能是產生具有隨機特性的偽隨機m 序列,通過FPGA 由VHDL 編程實現。偽隨機序列產生原理如下:

圖1 偽隨機序列產生原理圖

其中,ak-i是各移位寄存器的狀態,Ci對應各寄存器的反饋系數,為1表示參與反饋,為0不參與反饋。反饋函數為:

當級數n 和反饋系數一旦確定,則反饋移位寄存器的輸出序列確定了,m序列的一個重要的性質是:任一m序列的循環移位仍是一個m序列,序列長度為m = 2n-1 。

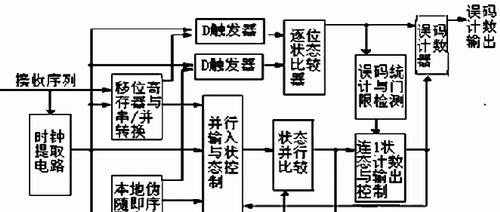

2 接收機

接收機主要由時鐘同步模塊、狀態同步模塊組成,其功能框圖如圖2 所示。

圖2 誤碼器接收機功能框圖

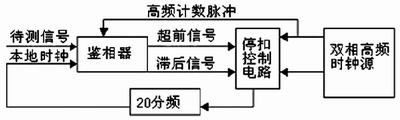

2.1 時鐘提取模塊

本單元所采用的時鐘提取方法是采用新的積分鑒相來實現的,通過在一個時鐘周期內對碼元進行積分,判斷超前滯后,從而極大的降低了因干擾信號的出現導致誤調的可能性。時鐘提取的原理圖如下:

圖3 時鐘提取原理圖

(1 )鑒相器

導前- 滯后型數字鑒相器的特點是,它輸出一個表示本地估算信號超前或滯后于輸入信號的量.如果本地估算信號超前于輸入信號,則輸出“超前脈沖”, 以便利用該“超前脈沖”控制本地估算信號的相位推后。反之,則輸出“滯后脈沖”,并使本地估算信號的相位前移. 導前- 滯后型數字鑒相器可分為微分型和積分型兩種.由于積分型導前- 滯后數字鑒相器,具有優良的抗干擾性能. 因此本設計采用了積分型導前-滯后型數字鑒相器.

積分型導前-滯后型數字鑒相器中,本地時鐘的上升沿為同相積分的清洗時刻,上升沿到來時,在本地高頻時鐘下,同相計數器開始計數,當輸入碼元是“1”時,每來一高頻脈沖計數器加1計數,當輸入碼元是“0”時,每來一高頻脈沖計數器減 1計數。當下一上升沿到來時,將計數值輸出,并清零計數器,計數器在高頻脈沖下重新開始計數.本地時鐘的下降沿為中相積分的清洗時刻,在下降沿到來時,在上述同樣的高頻時鐘下,中相積分計數器開始計數,當碼元為“1”時,計數器加1,當碼元為“0”時,計數器減1。當下一下降沿到來時,將計數值輸出,同時對計數器清零,重新計數。在準確同步的情況下,同相積分的積分區間正好和接收的一個碼元寬度相重合,同相積分計數器輸出為± T(+T表示碼元為1,-T 表示碼元為0),而中相積分器的輸出為0 或± T.在中相積分周期內若碼元出現0→1或1→0變化,則中相積分器輸出為0。在中相積分周期內,若碼元沒有翻轉,碼元始終為“1”,則中相積分計數器輸出為T。若碼元始終為“0”,則中相積分計數器輸出為-T。若本地估算時鐘超前于輸入碼元,當同相積分計數器的輸出大于0,則隨后的中相積分計數器的輸出也大于0,當同相積分計數器的輸出小于0時,則隨后的中相積分計數器的輸出也小于0。當同相積分計數器輸出為+T或-T時,隨后的中相積分計數器輸出也為+ T或-T 時,表明是處于連“1”或連“0”狀態,則超前或滯后標志都為0。若本地估算時鐘滯后于輸入碼元,當同相積分計數器的輸出大于0,則隨后的中相積分計數器的輸出小于0,當同相積分計數器的輸出小于0時,則隨后的中相積分計數器的輸出將大于0 。

當下降沿到來時,先檢測同相計數器的輸出,當為0時,如果中相計數器的輸出為0,則表示還沒開始檢測,就沒有超前滯后信息。如果中相計數器的輸出不為0,則表示本地估算的時鐘剛好與待檢測的時鐘正交,處于超前和滯后分界處,在這里對其做超前處理。如果同相計數器的輸出不為0,此時如果中相計數器的輸出為0,則表示剛好兩時鐘同步,故沒有超前和滯后信息。如果中相計數器的輸出為土20,即為整個碼元的長度。則表示中相計數過程始終為“1”或“0”,出現連“1”或連“0”狀態,為防止誤操作,同樣認為沒有超前和滯后。如果此時中相計數器的輸出不為0,也不為整個碼元,則將同相計數器的輸出和中相計數器的輸出的符號位進行異或,即兩者符號相同表示超前,符號不同表示滯后。

(2)雙相高頻時鐘源與停扣控制電路

雙相高頻時鐘源是形成兩路窄脈沖信號,兩個窄脈沖信號剛好相差180 度。停扣控制電路主要由添門和扣門組成,當來一個超前脈沖,加到扣門,扣除一個晶體脈沖,這樣分頻器的輸出脈沖相位就滯后了1/20周期。當來一個滯后脈沖,加到添門,控制添門打開,加入一個晶體脈沖到或門。由于加到添門的晶振信號與加到扣門的晶振信號的相位相差180度,因此當從添門加入一個晶振脈沖到或門時,相當于在扣門輸出的晶振信號中間插入一個窄脈沖,也就使分頻器輸入端添加了一個脈沖,這樣分頻器的輸出相位就提前了1/20周期。從而實現位同步。

2.2狀態同步模塊

狀態同步模塊主要包括逐位比較檢測模塊、誤碼統計與門限檢測模塊、并行輸入與狀態控制模塊、狀態并行比較模塊、連“1”狀態計數器模塊。

(1)誤碼統計與門限檢測模塊:在時鐘的節拍下,對誤碼脈沖計數,同時對時鐘脈沖進行計數。若誤碼個數占時鐘個數的30% 以上,則認為誤碼率很高,說明系統兩序列的狀態不同步,此時門限檢測器將輸出低電平,需要進行同步搜索。若誤碼個數占的比例較低,則輸出高電平,說明此時系統已狀態同步,不再進行同步搜索。

(2)并行輸入與狀態控制模塊:當控制端為“0”時,該模塊照原樣將兩組并行輸入信號送到輸出端,為“1”時,將所有輸出信號置“0”。這時狀態比較器的所有輸入信號都電位相同并輸出高電平,以表示系統已同步,進入同步保護狀態。

(3)連“1”狀態計數器模塊:該模塊的功能有兩個:一是對狀態比較器輸出的連“1”狀態進行計數,當計數器的計數量達到設置值時,計數器輸出為 “1”,并控制“并行輸入與狀態控制”電路,使各并行輸出位置

“0”。這樣,狀態比較器的各輸入位都為“0”,則其輸出為“1”,表示狀態已同步;若狀態不同步,則連“1”計數器的輸出始終為“0”。連“1”計數器的另一功能是當其輸出為“1”時,才使誤碼計數器進行計數。若在整個系統已同步后,出現了狀態失步,則通過誤碼統計與門限電路的輸出狀態控制連“1”計數器。當連“1”個數到達設定的個數時輸出為“1”,并送給并行輸入與狀態控制器,使其輸出置為“0”,以實現同步保護控制。

3 結束語

本文設計的誤碼儀的優點是可以很方便的應用于基帶傳輸信道的測試,可準確測量出基帶傳輸信道的傳輸誤碼,且成本較低。