摘 要: 一種針對大規模SoC設計的高效FPGA驗證流程,分析了該流程所涉及的關鍵技術:通用硬件平臺" title="硬件平臺">硬件平臺設計、FPGA軟件環境設計和軟硬件協同驗證等。采用這些技術,FPGA平臺可以快速且真實地模擬芯片應用平臺,從而實現軟硬件并行設計和協同驗證。該驗證流程已靈活應用于大規模SoC項目設計中,大大提高了SoC產品的研發效率。

關鍵詞: SoC FPGA驗證 軟硬件協同驗證

隨著SoC(System on Chip)設計的規模不斷擴大以及市場競爭日趨激烈,如何更快速設計出更高性能的SoC產品已經成為IC設計公司能否成功的關鍵。這其中,驗證的工作量平均占據總設計工作量的80%甚至更多,對于一個大規模SoC系統,驗證的效率和可靠性往往決定了項目的成敗。

最常用的驗證方法是通過軟件仿真驗證設計的功能,但由于軟件仿真速度和仿真模型" title="仿真模型">仿真模型的局限性,驗證往往難以達到令人滿意的要求。而FPGA驗證憑借速度和真實性的優勢,已經成為VLSI設計中非常重要的環節。

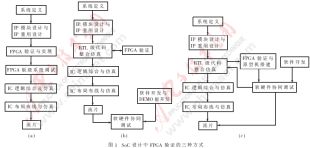

對于IC設計,一般來說有三種FPGA驗證方式,如圖1所示。

流程(a)只適用于結構簡單且對設計周期要求不高的應用。IC設計經過簡單的仿真即可嘗試在FPGA上運行,若實現結果真實可靠,再進行IC后端設計,然后流片。但當芯片比較復雜時,在FPGA開發板上的調試將花費大量時間,且由于FPGA本身的局限性,并不能完美地驗證SoC設計中的某些特殊任務,如低功耗設計、多時鐘域交互、數模混和等。

對于大規模且有特殊設計要求的IC設計可采用流程(b),它要求建立一個完善的SoC軟件仿真環境,IC設計的主要功能都可以在軟件虛擬平臺上得到比較全面的驗證。之后再把SoC設計在FPGA平臺上實現,憑借FPGA速度快和結果真實的優勢,可在FPGA平臺上運行大量的測試程序,以提高驗證的完備性。但該流程要求花費很多經費和時間構建硬件平臺,并且在驗證過程中,研究如何產生激勵和分析FPGA運行情況也將花費非常多的時間。考慮到項目周期和經費等因素,這種FPGA驗證流程很難對SoC設計進行徹底的驗證。同時,軟件人員必須在流片后才能在真實的環境下調試應用程序,這也就增加了項目風險和研發周期。

隨著市場競爭日趨激烈,SoC設計公司越來越需要找到一種更加完備的設計與驗證方法來提高SoC設計的效率和可靠性,驗證流程(c)則是最好的選擇。它是一個可適應于各種項目的通用的FPGA硬件驗證平臺,不必經常重新設計硬件平臺。該平臺具有強大驗證能力,可以非常真實地模擬各種SoC設計的功能和應用平臺,從而可以對其進行全面的驗證。該流程要求建立一個完善的FPGA綜合與仿真環境,與IC設計的環境統一起來,使得任何一個仿真的激勵都可以類比地在IC設計前端仿真、在IC后端仿真和在FPGA后端仿真。通過比較它們的結果,很容易地找到設計中的缺陷。這樣,整個驗證工作都將變得輕松而且透明。

在成功建立FPGA軟硬件設計環境后,軟件研發人員就可以并行的在該平臺上開發和調試應用軟件,并及時把系統級調試結果反饋到IC設計前端,這大大提高了研發效率,也非常全面地驗證了整個IC設計。同時,還可以在FPGA中加入某些監測分析模塊,真實地反饋芯片內部的運行數據,如處理器執行效率、總線利用率、帶寬等,這些對SoC項目的決策都是至關重要的。

下面將詳細闡述通用硬件平臺建設、軟件環境建設和軟硬件協同驗證等相關技術。

1 FPGA硬件平臺建設

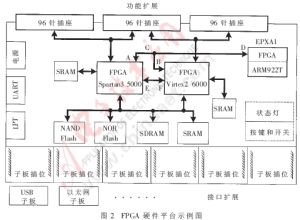

對于不同項目情況,FPGA硬件平臺建設有所不同,但主要應考慮FPGA邏輯資源、應用資源、擴展能力、PCB信號質量、易于調試、組態和成本等方面因素。下面結合項目實例(圖2)進行介紹。

1.1 FPGA邏輯資源

該硬件平臺采用Xilinx公司FPGA芯片 virtex2 6000(X2V6000)和spartan3 5000(X3S5000)各一片,它們分別具有600萬門和500萬門的邏輯資源。virtex2 6000面向于高端應用,時鐘和存儲資源更多、速度更快,主要用于實現對性能要求較高的DSP內核;spartan3 5000具有更低的成本,用于實現對性能要求稍低的片上IP應用模塊。該平臺還包含一片Altera公司的FPGA芯片EPXA1,該芯片包含ARM922T硬核,它將保證該FPGA硬件平臺能驗證ARM+DSP等多核的SoC項目,也方便了驗證和調試。

1.2 應用資源

為了能更廣泛地適應SoC應用方案,兩片大容量FPGA都各自與SRAM相連,以彌補片內RAM資源的不足。該硬件平臺還包含一個公共存儲器總線,用于連接常用的RAM和FLASH資源。這樣硬件平臺基本滿足了SoC應用方案對存儲資源的需求。

1.3 擴展能力

一個SoC的應用方案可能用到各種特殊的資源,通用的FPGA硬件平臺應該能承載這些資源。示例中采用了兩種擴展方式:一種是功能擴展,由三個96針的插座構成,它們與FPGA的距離近、延遲小、連接FPGA的I/O" title="I/O">I/O數量多,可用于連接功能擴展板,也可以通過該插座使兩塊FPGA板互連,使FPGA資源加倍,從而驗證更大規模的SoC設計。另一種是接口擴展,用于擴展SoC的外設資源,如SoC中常用到的USB總線收發器、以太網控制器等,都可以單獨作為子板來擴充,這些子板尺寸相同、引腳排列相似、且大多可采用兩層板實現,即靈活又降低了風險和成本。

1.4 PCB信號質量

由于FPGA具有非常多的I/O資源,使得保證PCB信號質量成為難點。該硬件平臺設計為14層板,采用Cadence公司的軟件Allegro進行PCB設計,采用sigXplore進行信號完整性分析。對各種拓撲情況下的信號質量仿真表明,由于FPGA自帶數控匹配電阻,兩點互連線可以得到較好的信號質量,加大布線間距后,串擾也可以小到令人滿意的水平,但連接多個器件的信號反射比較嚴重。對于公共存儲器總線,布局時應盡量拉近芯片間的距離,并設置最大線長約束。當線長足夠短時,經仿真,信號質量可以達到要求。對于三個FPGA間的互連線,由于線數非常多,很難全部縮短它們的長度,這時應設置布線約束,如圖2,使AC與BC的距離相等,從而使A點和B點對C點的反射貢獻相同,AD或BD可以得到較好的通信質量。然而AB間的通信質量卻由于D點的反射而變得很差,但這兩塊FPGA間可以通過EF點來通信。這樣,三片FPGA間的通信就都可獲得較好的信號質量。

綜上所述,FPGA硬件驗證平臺的搭建應根據項目情況有所不同,但所考慮的因素大體上可以分為以上四類,本文所提出的開發平臺示例已經針對這四個方面提出了較好的解決方案,該硬件平臺已成功應用于FPGA驗證項目中。

2 FPGA軟件環境建設

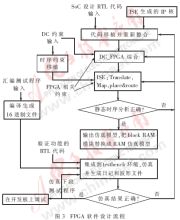

FPGA軟件環境部分的工作,不僅包括對特殊的RTL代碼及相關約束的修改,如門控" title="門控">門控時鐘處理、硬IP核替換等,還要根據特定的硬件平臺,增加FPGA相關的約束,并搭建一個能夠自動仿真和驗證的環境。因為在這一過程中RTL代碼和約束要經過多次版本的變化,靠手工進行維護非常容易出錯,這些錯誤很難檢驗,甚至可能損壞開發板。所以必須建立一個足夠完善的軟件環境,能夠在人的稍微干預下,自動完成以上處理,并易于定位錯誤。圖3所示是FPGA軟件環境設計流程圖,下面將分類介紹搭建軟件環境的幾個重要環節。

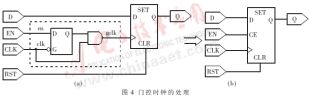

2.1 門控時鐘的處理

在SoC的設計中,經常會用到門控時鐘。如圖4(a)所示,當en為‘1’時,時鐘clk可傳送到gclk;當en為‘0’時,gclk恒為‘0’。為了防止真實芯片中en和clk延遲差異可能造成的毛刺,該電路還需要一個latch鎖住en的狀態。對于SoC設計,使用者可以根據芯片使用情況把一些不用的模塊的時鐘關閉,這大大降低了芯片的功耗。

由于FPGA芯片特定的結構,它的全局時鐘線數非常有限,并且經過與門輸出的信號傳輸到全局時鐘需要很大的額外延時,這使得圖4(a)電路很難在FPGA中實現。通常的辦法是,在FPGA中采用如圖4(b)所示的電路來代替門控時鐘的功能,該電路把源時鐘clk和en信號分別接到每個觸發器端。當en信號為‘0’時,clk信號雖不停止,但觸發器并不觸發,這使得該電路的功能與4(a)相同。該方法把芯片內的時鐘線數大大縮小,使之可以采用全局時鐘線布線,這充分利用了FPGA中全局時鐘0偏斜的特點,避免了由于時鐘線的延時所產生的時序問題,提高了系統的性能。目前,DC_FPGA綜合工具可以支持門控時鐘的自動處理,它要求把RTL代碼中門控時鐘單元改寫成特定的風格,并增加幾條約束語句,即可自動實現如圖3所示的處理。該方法使時鐘樹非常復雜的SoC設計的FPGA驗證變得簡單,在實用中取得了非常好的效果。

2.2 硬IP核替換與RTL重新整合

在SoC設計中,經常會使用一些硬IP核,如PLL、SRAM、ADC、USB transceiver等,這些電路大部分屬于模擬電路,無法在FPGA中實現。對于PLL、SRAM等模塊,一般采用FPGA內部的時鐘管理資源和存儲資源來實現,只要在RTL調用關系上作些調整即可。對于其他硬IP核,需要在開發板上選用同樣功能的芯片,與FPGA共同實現它們的功能。在RTL級,首先要取消對硬IP核的調用,然后在ISE軟件約束中,把原先連接IP的信號綁定" title="綁定">綁定到FPGA的I/O上,并與功能芯片的特定信號相接。由于用于替換硬IP的資源很難做到在引腳和功能上完全一致,還需要根據具體情況對RTL代碼稍作修改。

對于多FPGA驗證,需要把SoC設計分成幾個部分,分別在不同的FPGA上實現。這時主要應考慮FPGA資源的合理利用以及功能的完整性,讓各個FPGA完成相對獨立的功能,這將簡化RTL代碼的分割,也使調試工作變得相對容易。

2.3 約束的移植

在IC的后端設計中,需要加入很多時序、功能等約束,如最大時鐘周期、false path、重命名等。這些約束在FPGA實現過程中也要求有效,但因FPGA工具軟件約束語法不同,需要進行約束的移植。在漢芯的FPGA驗證項目中,綜合工具DC_FPGA與DC的約束語法兼容,可以直接采用DC的約束語句。DC_FPGA綜合生成EDIF文件,在ISE下進行布局與布線操作,這時應采用perl語言把DC中的時序相關約束轉換成ISE的約束,這種做法減少了人為錯誤,提高了執行效率。

另外,還要加入FPGA的相關約束,主要包括FPGA后端布局布線策略的設置、存儲器初始化和I/O的綁定等約束。對于前兩種,可根據項目的要求和ISE的語法加入適當約束即可。但對于I/O非常多的FPGA,I/O綁定約束靠手工維護很容易出錯,而且如果綁定到錯誤的位置,有可能造成比較大的故障,甚至損壞硬件。這里建議在RTL級為每塊FPGA寫一個通用的頂層模塊,信號的命名與原理圖中一致,并在約束文件中綁定到正確位置,再由該頂層文件調用實際的SoC設計代碼,這種做法將會大大降低版本變更中人為出錯的可能。

2.4 自動仿真環境搭建

FPGA后端仿真對于檢驗FPGA操作流程中各個步驟的正確性是至關重要的一步,沒有一個比較完善的后端仿真,SoC設計就很難成功地在FPGA平臺上實現。在漢芯的項目中,RTL代碼的前端仿真環境已經實現了激勵的自動生成與結果的自動比對功能。如圖3所示,驗證人員把測試各個模塊的匯編程序和RTL代碼輸入,仿真環境會自動編譯程序并把生成的指令和數據初始化到RAM中,并開始仿真。在仿真過程中會自動把所要求的寄存器或RAM中的內容與正確的值相比較,并給出正確與否的結論,同時也會生成相應的波形和日記文件以供分析。對于FPGA后端仿真環境,應該具備前端仿真環境的驗證功能,并且與前端仿真環境保持一致,這保證了同一個激勵程序分別在前后端的環境下仿真,可以得到相同的結果。當出現不一致時,比較生成的波形就很容易定位FPGA后端操作中的問題。

基于上述分析,建立FPGA后端仿真環境首先要求在FPGA后端工作的每個步驟中,從層次結構、命名規則等方面都要與前端RTL代碼保持一致,這可以通過工具軟件中相應的約束來實現。另外,仿真中要求能把匯編程序下載到片內RAM中,而ISE軟件生成的仿真模型中,片內RAM已經變成了由很多塊block RAM拼成,對它們的初始化會很復雜。一個好的解決方案是在后端靜態時序分析都正確的前提下,把ISE軟件生成的仿真模型文件中的RAM替換成與前端仿真模型中的RAM相一致,這即保證了與前端一致,也方便了對其初始化和檢測內容。

3 軟硬件協同驗證

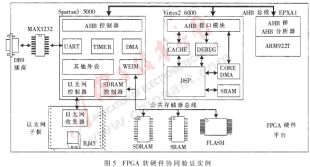

下面將結合項目實例介紹軟硬件協同驗證技術,如圖5所示。該項目采用具有10級流水線的低功耗高性能DSP核,與ARM922T構成雙核的SoC,面向移動平臺應用。由于在仿真環境中難以對整個系統進行充分的分析和驗證,故將該SoC在FPGA平臺上實現。該平臺通過以太網采用DMA方式把圖像數據傳給DSP,由DSP程序實現各種圖像處理的算法,并把處理結果從以太網傳回PC機,同時通過UART報告處理進度。利用該驗證平臺可實現如下任務。

3.1 系統驗證

進一步驗證在真實應用情況下整個SoC設計的功能的正確性。由于ARM具有一套完善的開發工具,可以非常容易地控制它產生激勵并監測DSP和外圍模塊的運行情況。首先,通過ARM實現調試DSP的功能,在DSP內部加入DEBUG模塊后,就可以通過它對DSP進行程序下載、單步、斷點等功能調試。另外,還可以在ARM上運行測試程序,把系統運行到特定時間和步驟的執行結果提取出來并自動比較是否正確,然后把這些信息通過UART傳到PC機,這將使整個系統的運行完全透明。

3.2 架構分析

對于一個SoC設計,架構的設計是至關重要的,它要求根據SoC具體應用情況對芯片的功耗、帶寬、成本等多方面因素進行折中,超過實際需要的性能或帶寬將會帶來成本和功耗的增加,這些都將影響產品的市場競爭力。通過加入一些特定的分析監測模塊,就可以在FPGA平臺上更加容易地分析系統架構的性能。如圖5所示,AHB分析器可以把AHB總線上的主從設備的切換頻率和效率、最大總線利用率等細節情況真實地反饋到PC機,為SoC架構的分析提供非常真實的資料。

3.3 軟件優化與分析

對于一個SoC平臺系統,軟件的設計與優化也是非常重要的。在FPGA平臺上有上述提到的多種手段監控和分析軟件運行情況,這樣可以更好地優化軟件,發揮SOC平臺的最大潛力。還可以通過分析不同功能的應用軟件對系統帶寬和處理能力的真實需求,研究增加硬件協處理功能的可行性和必要性,做到真正的軟硬件協同設計與驗證。

上述SoC項目實例已在FPGA開發板上實現,成功地運行了小目標檢測等多個圖像處理程序,并實時反饋了DSP指令流水中斷、DMA數據搬移、AHB總線競爭等許多芯片運行情況的信息。其中,基于對AHB總線競爭信息的分析,優化了軟件的數據調度機制,同時改進了總線仲裁機制,切實地提高了AHB總線的數據吞吐率。

參考文獻

1 Hauck S, Borriello G.Pin Assignment for Multi FPGA Sys-tems.IEEE Transactions on Computer-aided Design of Integ-rated Circuit and Systems, 1997;16(9)

2 Gschwind M. FPGA Prototyping of a RISC Processor Core for Embedded Applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2001;9(2)

3 Synopsys. Design Compiler FPGA user guide. CA: Synopsys Inc., Mar., 2004

4 Synopsys. VCS user guide. CA: Synopsys Inc., Sep., 2003