在船舶交管和樓宇保安等視頻監控中,為了快速判斷某圖像來自何時何處,通常會在圖像上疊加時間地點信息,這些信息一般是若干個字符。完成此功能的字符疊加器" title="字符疊加器">字符疊加器一般采用分立的集成電路或專用OSD芯片來實現。本文提出一種基于CPLD" title="CPLD">CPLD的簡易字符疊加器,具有成本低、抗干擾性能好等特點,適用于視頻監控。由于采用了CPLD器件,增強了系統集成度和設計靈活性。

系統組成及基本原理

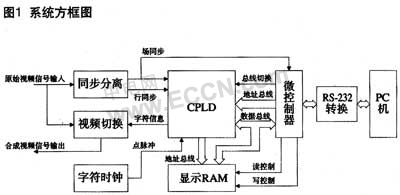

這種字符疊加器的系統方框圖如圖1所示。圖中CPLD采用ispLSI1016,完成地址生成、總線切換、并串轉換、地址鎖存等核心功能。外圍器件還包括微控制器、顯示緩存RAM" title="RAM">RAM、以及RS-232串口電平轉換芯片等。

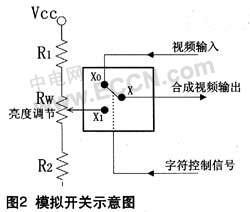

其中,字符時鐘提供CPLD固定的時鐘信號,以保證CPLD在一定的時序下正常工作,并產生視頻疊加所需的各種信號。微控制器采用AT89C52,其在場同步脈沖的外中斷觸發下,在視頻信號回掃消隱期間,接收上位PC機通過串口下傳的字符信息,寫入顯示RAM中。也可根據上位PC機的指令將固化在其內部FLASH ROM中的點陣字符信息直接寫入顯示RAM中。場、行同步脈沖是字符顯示的基準,所以輸入的視頻信號先經同步分離電路分離出場、行同步脈沖。視頻同步分離器采用LM1881,該芯片能夠分離出PAL、NTSC、SECAM制式視頻信號中的復合同步信號、場同步信號、消隱信號、奇偶場信號。此芯片也適用于非標準的視頻信號。視頻切換是將兩路視頻信號合成為一路視頻信號,若對于數字信號可采用數據選擇器,但對于模擬信號來說,只能采用模擬開關,其原理如圖2所示。當沒有字符控制信號的時候,將視頻輸入X0和輸出X短路,即視頻信號直通,若此時字符控制信號輸入端有字符信號時,則將輸出端X與可調節的固定電平X1相連。本設計中采用的是CD4066,顯示緩存RAM采用普通的8位RAM。RS-232串口電平轉換采用MAX232。

CPLD芯片的內部邏輯設計

CPLD內部電路主要由定時、并串轉換、地址總線切換以及地址鎖存等組成。

定時部分

該部分由八分頻器、行計數器、列計數器以及消隱處理單元組成。

由于CPLD器件內部未內置時鐘振蕩器,所以其主振信號采用外部已經整形的脈沖信號。此設計中采用了帶驅動的方形石英振蕩器。通過計算,點時鐘脈沖應該為8MHz左右。

將外部產生的時鐘脈沖作為最高點脈沖。由于RAM的數據總線寬度是8位,這里將點脈沖進行8分頻,得到字符脈沖,完成此功能的是一個3位同步計數器。然后再對字符時鐘進行6位二進制計數,即列計數,由此可以知道一行橫向最多可以顯示64個英文字母或者32個漢字(受到CPLD容量和顯示RAM空間的限制),完成此功能的是一個6位同步計數器。以上兩個計數器的清零端接外部的行同步脈沖的反相信號。當行同步信號到來的時候,掃描進入回掃期,這時兩個計數器都清零并不再計數,直到行同步信號消失。6位同步計數器計滿需要52μs,正好與我國電視標準掃描正程時間相等。對其用外部行同步信號清零,則可以保證產生的字符信號與外部視頻信號保持同步。此外,再用一個9位同步計數器來完成對行同步脈沖的計數,并用視頻信號的場同步脈沖反相信號對其清零,該行同步計數器取值應小于312。最后,將行計數器和列計數器的輸出依次接在顯示RAM地址線上,建立起掃描時刻和顯示RAM單元的聯系,即顯示RAM成了屏幕顯示的映象。當掃描線掃到某固定位置,同時讀出顯示RAM相應單元的數據,這樣就可以在屏幕上任意位置顯示字符。

并串轉換部分

該部分由并串轉換單元和字符輸出單元組成。

因為顯示RAM的數據寬度是并行8位,所以為了視頻疊加需要把它轉換成串行的視頻數據流,即需要一個并串轉換電路。本文電路由一個帶置數端的8位移位寄存器構成。當8分頻的字符時鐘到來時,將數據總線上顯示RAM送出的8位字符數據存入寄存器,隨后用點脈沖將數據逐一移出。為了保證在掃描回程中沒有視頻信號出現,字符輸出單元將串行的視頻數據流和行同步、場同步以及地址切換信號相與后再輸出字符信息。 地址總線切換部分

由于并串轉換部分需要不斷從顯示RAM中讀取數據,以便轉換成相應的視頻數據流,同時微控制器也需通過隨時修改顯示RAM中的內容以達到改變屏幕顯示的目的,顯示RAM需要能夠處理兩條總線上的內容。為了使只有一條數據地址總線的普通RAM能夠處理兩條總線上的數據,需要有地址信號切換電路,這里選用雙16位數據選擇器。為了屏幕顯示不受總線切換的影響,則要求總線切換必須在掃描逆程進行。 地址鎖存部分

由于MCS-51系列的微控制器總線是數據地址復用的,而本設計中的微控制器采用的又是總線控制方式,所以地址和數據信號需要采用鎖存器進行分離。在本設計中,將鎖存器也置入CPLD內部,從而使外部的電路變得更簡單。

對于該CPLD芯片的邏輯設計一般可采用硬件描述語言VerilogHDL或VHDL" title="VHDL">VHDL來完成,亦可采用如本設計中的原理圖輸入法來完成。

微控制器程序的設計

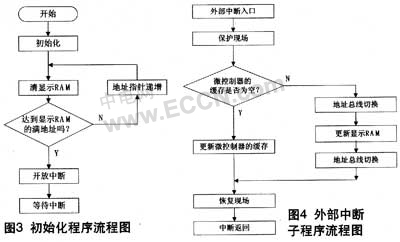

初始化程序主要用于系統的初始化配置、開放外中斷及對顯示RAM的清除,其流程及外部中斷子程序流程圖如圖3、圖4所示。

實踐證明,通過以上硬件和軟件設計,該字符疊加器在視頻監控中能夠實現很好的效果。特別是由于采用了CPLD器件,大大增強了設計的靈活性。