摘要:全雙工異步串行通信在TMS320C55xDSP上的通常實現方式是利用DSP的McBSP接口加外接芯片實現,這種設計方法增加了實現UART的硬件成本和電路設計復雜度。提出了一種直接利用DSP的MCBSP接口和DMA通道實現UART的方法,給出了使用C語言和CSL的編程方法。與傳統實現方法相比,具有實現成本低,硬件電路簡單,移植性強等特點,稍加修改可應用于C5000和C6000各系列芯片中。

關鍵詞:DSP;全雙工異步串行通信;多通道緩沖串口;DMA ;過采樣

1 引言:

MS320C55x數字信號處理器通過多通道緩沖串口(McBSP)提供了與外設的多種同步串行通信方式。然而,由于DSP中串行通信由數據信號、幀同步信號和時鐘3種信號配合實現,其中幀同步信號和數據信號由不同的數據線傳輸。而異步串行通信則在一根傳輸線上實現數據發送或接收,且不需要專門的時鐘信號線。因此DSP與異步設備的接口,如UART通信實現相對復雜,需要對McBSP的相關寄存器進行正確初始化。DSP中實現全雙工異步通信的通常做法是使用專用的串行接口芯片,如TL16C550,這種設計方法編程相對簡單,但增加了設計成本和電路復雜度。本文介紹了一種TMS320C55x DSP芯片利用McBSP和DMA直接實現UART的方法,基于該方法實現的DSP異步串行通信模塊已成功應用于控制偏振圖像采集處理的DSP硬件設備中。 www.51kaifa.com/

2 UART在DSP上的實現

異步串行通信要求DSP能夠模擬和檢測到UART的幀信號。由于DSP串口是同步串口,而且DSP時鐘為高速時鐘,經分頻或倍頻后無法保證與UART的異步串行時鐘精確同步。DSP的幀同步信號無法與UART的幀信號同步,造成串行通信信號中信號位的偏移。最好的解決方法是減小偏移和對接收的數據流進行過采樣,本文采用了對UART信號的16倍過采樣。www.51kaifa.com/

2.1 McBSP設置

DSP的McBSP通過3種信號實現同步通信:數據、幀同步和時鐘。異步通信發送和接收各在一條線上進行,具有自己的幀時序。

UART的通信時鐘由使用的通信波特率(每秒傳輸的數據位個數)決定,通常為2400,9600,19200等。DSP與UART異步通信時,由于DSP的內部時鐘頻率通常都不是UART時鐘頻率的整數位,因而會造成雙方通信時數據位的偏移,為了盡量減小這種偏移,McBSP的串口時鐘需要正確的設置時鐘頻率以達到與UART波特率相匹配。

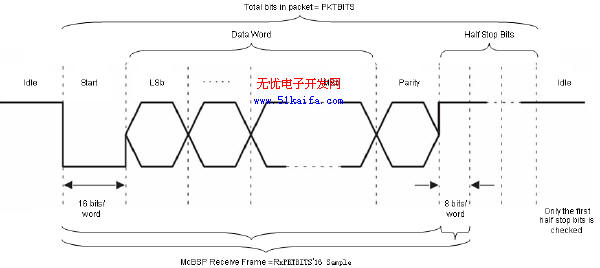

數據包(PKTBITS)由起始位、數據位、奇偶校驗位和停止位組成,起始位為1位,停止位通常為1,1.5,2位,數據數通常為8位,如何使用校驗,那么數據包還包括1位校驗位。以上數據位中,每1位都被DSP以16倍波特率的時鐘頻率過采樣。

發送時,為保證UART能收到半個停止位,需要將DSP的McBSP發送端口設置為2相的數據幀。第1相為16位的數據字,第2相為8位的數據字。那么第1相數據長度為(起始位+數據位+校驗位)個字,第2相長度為停止位的字長。發送時的總幀長(TxPKTBITS)為這兩相的總字長。接收數據包格式與發送相似,其結構如圖2所示。DSP的串口發送引腳與外部串口設備的接收引腳相連,不使用FSX引腳和CLKX引腳。

接收時,McBSP通過接收幀同步信號引腳(FSR)檢測數據的到來,根據幀同步信號的不同,幀同步信號可配置成上升沿觸發或下降沿觸發,由于UART的起始位為低電平,因此使用下降沿觸發。將UART發送數據信號與McBSP的數據接收引腳DR和FSR相連,實現用UART的發送信號觸發McBSP的接收幀同步信號。在McBSP接收一幀數據期間,為了防止下降沿再次觸發一幀數據接收,McBSP應該設置為接收數據包期間忽略幀同步信號。

圖1 UART接收數據包的幀格式

接收完一幀數據后,需要對數據解碼,收于DSP發送和接收時鐘是UART串口時鐘頻率的16位,因此每個UART數據位對應于DSP中1個16位字(停止位對應8位字)。在McBSP接收寄存器中將接收幀設置為2相,第1相16位字,字長為RxPKTBITS(起始位+數據位+校驗位),第2相為8位字,對應于停止位字數。此外,接收幀延時值應該設置為1位。

3.2 McBSP時鐘采樣率設置

McBSP與UART通信時,McBSP接收到一幀的幀同步信號后,該幀期間之后出現的幀同步信號將被忽略。為了獲得最大數據流量,一幀數據發送結束時,其停止位后緊接著為起始位,幀同步信號的檢測依賴于停止位到起始位的下降沿。為了正確檢測到幀同步信號,高電平應該至少保持一個時鐘周期以上時間。

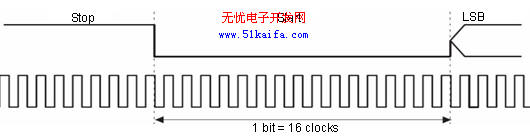

理想情況下,串口時鐘信號邊沿與數據位邊沿精確對應,此時,每個數據位對應16倍時鐘周期。起始位和串口時鐘的下降沿偏最小,如圖3所示。

圖2 McBSP串口時鐘與UART時鐘精確同步時的時序

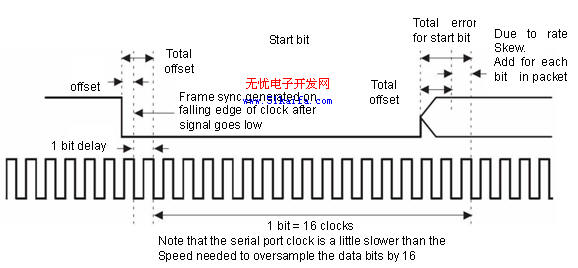

正常通信時,McBSP的幀同步信號與UART串口的時鐘之間會有一定的偏差,如圖所示。

圖3 McbSP串口時鐘與UART時鐘存在偏差時的時序

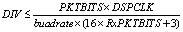

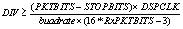

存在偏差時,為保證McBSP能檢測到接收到信號的下降沿,McBSP的串口采樣時鐘頻率必須準確設置。其設置方法如公式1、2所示。其中,DIV是McBSP寄存中串口采樣時鐘分頻值,DSPCLK是DSP的CPU時鐘頻率,baudrate為通信波特率。

(1)

(1)

(2)

(2)

通信波特率為19200,DSP時鐘頻率為75MHz,接收數據包為10位(1位起始位,8位數據位,無校驗,1位停止位:PKTBITS=10,RxPKTBITS=9.5),根據公式1計算得DIV ,由于分頻值DIV為整數,因此取DIV 。根據公式2計算得DIV ,取整后得DIV 。取DIV最佳值為244。TMS320VC55x DSP以常用波特率通信時的分頻值如表1所示。

表1 常用波特率下TMS320VC55x的McBSP串口DIV值

|

|

75-MHz DSP Clock |

100-MHz DSP Clock |

||||

|

Baud Rate |

Divisor Minimum |

Exact Divisor |

Divisor Maximum |

Divisor Minimum |

Exact Divisor |

Divisor Maximum |

|

19200 |

240 |

244.14 |

248 |

320 |

325.52 |

331 |

|

38400 |

120 |

122.07 |

124 |

160 |

162.76 |

165 |

|

57600 |

80 |

81.68 |

82 |

107 |

108.51 |

110 |

|

115200 |

40 |

40.69 |

41 |

54 |

54.25 |

55 |

3.2 DMA設置

UART通信時,DSP發送和接收到的數據存儲在數據存儲器中,為了實現DSP的高速處理,減少DSP響應McBSP數據寄存器中斷的次數。發送和接收數據與McBSP發送和接收寄存器DXR和DRR之間的數據傳輸通過DMA通道完成。這里以使用DMA通道4和通道5為例,其中,DMA通道4作為數據接收通道,DMA通道5做為數據發送通道。將通道4和通道5的同步事件分別設置為McBSP串口接收事件和串口發送事件,DMA通道4的源地址為McBSP的接收寄存器DRR地址,目的地址為數據存儲器中存放接收數據的變量地址;DMA通道5的源地址為數據存儲器中待發的數據,目的地址為McBSP的DXR寄存器地址。每當McBSP接收到數據時,會觸發DMA通道4將接收到的數據拷貝到DSP數據存儲器的相應置,同時目的地址指針自動加1;發送數據時,DMA通道5將待發送數據拷貝到DXR,將數據依次發出。

發送數據時,待發字符被打包成適于UART接收的數據格式,以發送16進制無符號數0xAA為例,首先發送起始位,然后是數據位最低位,最后發送停止位。該數值在數據存儲器中按地址由低到高的存放格式為:0x0000,0x0000,0xFFFF,0x0000,0xFFFF,0x0000,0xFFFF,0x0000,0xFFFF,0xFFFF。

接收到數據后,取過采樣到的每個16位二進制數據字的中間四位,若中間四位中1的個數不小于3,則表示收到當前的UART數據位值為1;若中間四位中0的個數不小于3,則表示收到當前的UART數據位值為0。否則認為數據傳輸出錯。

4 程序設計

在McBSP和DMA寄存器設置正確的基礎上,利用TI公司提供的Code Composer Studio集成開發環境編寫了UART串口通信軟件,軟件開發中使用了CSL(片上支持庫),使整個開發過程快速、直觀、具有很強的可讀性。程序流程如圖所示:

圖4 TMS320VC55x UART程序流程圖

5 實驗分析

硬件和軟件設計完成后,進行了測試實驗,實驗上位機為PC機,DSP處理器為TI公司的TMS320VC5509A,通信波特率為19200,DSP外部晶振頻率為20MHz,CPU時鐘頻率為100MHz,UART數據格式為1位起始位,8位數據位,1位停止位,無校驗。多次實驗結果表明數據發收準確,無誤碼現象發生。

6 結論

DSP系統直接與外部全雙工異步串行設備的通信時,通過正確的使用DSP上的McBSP和DMA通道,利用16倍過采樣原理準確的計算McBSP通信接口的采樣值和配置相關寄存器,能夠實現DSP與外部異步設備的可靠通信。與傳統的采用串并轉換芯片的實現方法相比,具有更低的成本更簡單的外部電路。本文中的程序針對TI公司的TMS320VC5509x DSP芯片編寫,通過對少數寄存器的修改,該程序可直接應用于TI公司的C5000和C6000系列DSP芯片上。

本文作者創新點:提出了一種直接利用DSP的McBSP接口和DMA通道實現UART的方法,具有實現成本低,硬件電路簡單,移植性強等特點。

參考文獻:

1 TMS320VC5509A Fixed-Point Digital Signal Processor Data Manual. Texas Instruments

2 TMS320VC5501/5502/5503/5507/5509/5510 DSP Multichannel Buffered Serial Port (McBSP) Reference Guide. Texas Instruments

3 Implementing a Software UART on the TMS320C54x with the McBSP and DMA. Texas Instruments

4 TMS320VC5503/5507/5509/5510 DSP Direct Memory Access (DMA) Controller Reference Guide

5 TMS320C55x Chip Support Library API Reference Guide. Texas Instruments

6 TMS320C6000 McBSP: UART. Texas Instruments

7 安穎,劉麗娜.基于DSP的高速信號采集與處理系統的設計【J】.微計算機信息,2005,1:57-58。