數字電壓表是大學物理教學和實驗中的重要儀表,其數字化是指將連續的模擬電壓量轉換成不連續、離散的數字量并加以顯示。傳統的實驗用模擬電壓表功能單一、精度低、體積大,且存在讀數時的視差,長時間連續使用易引起視覺疲勞,使用中存在諸多不便。而目前數字萬用表的內部核心多是模/數轉換器,其精度很大程度上限制了整個表的準確度,可靠性較差。本文采用National Semiconductor。公司性能優越的8位A/D轉換器ADC0809對模擬電壓采樣,以一片高性能FPGA芯片為控制核心,以軟件實現了諸多硬件功能,對電壓信號的轉換結果進行準確實時的運算處理并送出顯示。系統的主要功能都集成在一塊芯片上,大大減少了系統的分立元件數量,降低了功耗,增加了可靠性,較好地實現了電壓的精準測量。

1 設計方案比較

采用雙積分式模/數轉換器為核心器件,稱為雙積分式電壓表。在一個測量周期內,將被測電壓Ui加到積分器的輸入端,在確定的時間內進行積分。然后切斷輸入電壓,在積分器的輸入端加與Ui極性相反的電壓U,進行定值積分,但積分方向相反,直到積分輸出達到起始電平為止,從而將Ui轉換成時間間隔量進行測量。只要用計數器累計時間間隔內的脈沖數,即為Ui之值。電路簡單,便于維護。但電壓表的測量精度完全受限于模/數轉換的精度。而且系統無升級空間。

另外,采用單片機作為系統的控制核心。輸入信號經模/數轉換后送到單片機進行數據處理,根據不同電壓信號計算出不同數值,并送出顯示。這種方案優點是的單片機技術成熟、運算功能較強、編程靈活、設計成本也較低,能較準確地測量輸入電壓。但在單片機系統中必須使用許多分立元件組成其外圍電路,整個系統顯得十分復雜,可靠性較低,抗干擾能力差,而且功耗高。

采用現場可編程門陣列即FPGA為系統核心,是當今電子產品設計的熱門發展方向。系統最大限度地將所有器件集成在FPGA芯片上,體積大大減小、集成度高,可靠性高。而且邏輯單元控制靈活、適用范圍極廣,實現了大規模和超大規模電路的集成。其硬件功能完全由軟件編程實現,修改調試方便,在不改變原有電路的基礎上便可實現系統升級。較好地克服了另外兩種方案的缺陷,具有自己獨特的優勢。綜合上述分析,采用FPGA技術,優勢明顯。

2 系統工作原理

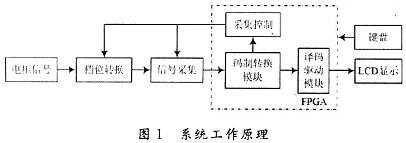

首先,被測電壓信號進入A/D轉換器,FPGA中控制信號模塊發出控制信號,啟動A/D轉換器進行轉換,其采樣得到的數字信號數據在相應的碼制轉換模塊中轉換為顯示代碼。最后譯碼驅動模塊發出顯示控制與驅動信號,驅動外部的LCD模塊顯示相應的數據。通過外部的鍵盤,可以手動對系統進行復位控制和檔位選擇,不同的檔位決定不同的電壓輸入范圍,在程序中實現自動轉換。基本工作原理框圖如圖1所示。

3 關鍵電路設計

3.1 A/D轉換電路

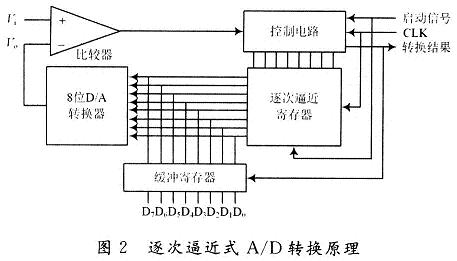

實現A/D轉換的方法比較多,常見的有計數法、雙積分法和逐次逼近法。由于逐次逼近式A/D轉換具有速度快,分辨率高等優點,而且采用該法的ADC芯片成本較低,因此在設計中采用該種方式。逐次逼近式A/D轉換器的原理如圖2所示。它由逐次逼近寄存器、D/A轉換器、比較器和緩沖寄存器等組成。當啟動信號由高電平變為低電平時,逐次逼近寄存器清0,這時,D/A轉換器輸出電壓V。也為O,當啟動信號變為高電平時,轉換開始,同時,逐次逼近寄存器進行計數。轉換原理如圖2所示。

逐次逼近寄存器工作時與普通計數器不同,它不是從低位向高位逐一進行計數和進位,而是從最高位開始,通過設置試探值來進行計數。在第一個時鐘脈沖到來時,控制電路把最高位送到逐次逼近寄存器,使它的輸出為10000000,這個輸出數字一出現,D/A轉換器的輸出電壓V。就成為滿量程值的128/255。這時,若Vo>Vi則作為比較器的運算放大器的輸出就成為低電平,控制電路據此清除逐次逼近寄存器中的最高位;若Vo≤Vi則比較器輸出高電平,控制電路使最高位的1保留下來。

若最高位被保留下來,則逐次逼近寄存器的內容為10000000,下一個時鐘脈沖使次低位D6為1。于是,逐次逼近寄存器的值為11000000,D/A轉換器的輸出電壓Vo到達滿量程值的192/255。此后,若Vo>Vi則比較器輸出為低電平,從而使次高位域復位;若Vo

這里采用的ADC0809是單片雙列直插式集成芯片,是8通道8位A/D轉換器,其主要特點是:分辨率為8位;總的不可調誤差±1 LSB;當模擬輸入電壓范圍為0~5 V時,可使用單一的+5V電源;轉換時間為100μs;溫度范圍-40~+85℃;不需另加接口邏輯可直接與CPU連接;可以輸入8路模擬信號;輸出帶鎖存器;邏輯電平與TTL兼容。

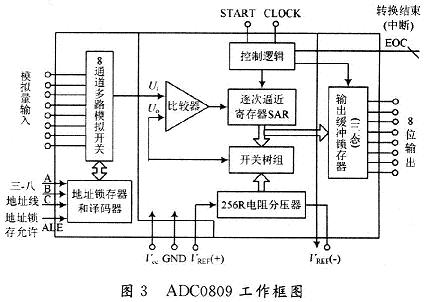

ADC0809帶有8位轉換器、8位多路切換開關以及與微處理機兼容的控制邏輯的CMOS組件。它的8位A/D轉換器轉換方法為逐次逼近法。在A/D轉換器的內部,含有一個高阻抗斬波穩定比較器,一個帶有模擬開關樹組的256R分壓器,以及一個逐次逼近的寄存器。8路的模擬開關由地址鎖存器和譯碼器控制,可以在8個通道中任意訪問一個單邊的模擬信號。其工作框圖如圖3所示。

該A/D轉換器無需調零和滿量程調整。由于多路開關的地址輸入能夠進行鎖存和譯碼,而且三態TTL輸出也可以鎖存,易于與微處理器進行接口。

如圖3所示,它由兩大部分所組成:第一部分是8通道多路模擬開關,它用于控制C,B,A端子和地址鎖存允許端子,可使其中一個通道被選中;第二部分為一個逐次逼近型A/D轉換器,它由比較器、控制邏輯、輸出緩沖鎖存器、逐次逼近寄存器以及開關樹組和256R電阻分壓器組成。后兩種電路,即開關樹和256R電阻分壓器,組成了D/A轉換器。控制邏輯用來控制逐次逼近寄存器從高位到低位逐次取1,然后將此數字量送到開關樹組,即8位開關,用來控制開關S7~S0與參考電平相連接。參考電平經256R電阻分壓器,輸出一個模擬電壓Uo,Uo,Ui在比較器中進行比較。當Uo>Ui時,本位D=O;當Uo≤Ui時,則本位D=1。因此,從D7~D0比較8次即可逐次逼近寄存器中的數字量,即與模擬量Ui所相當于的數字量相等。此數字量送入輸出鎖存器,并同時發轉換結束脈沖。

該電壓表電路中,ADC0809的工作時序如圖4所示。主要控制信號:START是轉換啟動信號,高電平有效;ALE是3位通道選擇地址(ADDC,ADDB,ADDA)信號的鎖存信號。當模擬量送至某一輸入端,由3位地址信號進行選擇,而地址信號由ALE鎖存;EOC是檔位轉換的狀態信號。EOC輸出高電平時,表示轉換結束;在EOC的上升沿后,若使能輸出信號OE為高電平,則三態緩沖器打開,將轉換完畢的8位數據結果輸至數據總線,至此ADC0809的一次轉換結束。

3.2 檔位轉換電路

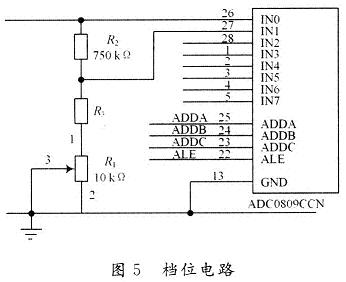

為了增加數字電壓表的測量范圍,設計了檔位選擇電路。采用精密電阻分壓方法,簡潔實用。ADC0809有8路數據輸入端口,原理上可以分為8個檔位。從實用性出發,只分了兩檔,如圖5所示。圖5中電位器負責電阻校準。盡管采用精密電阻,各電阻值的制造誤差不可避免,用電位器來微調校準以保證測量精度。ADC0809的輸入范圍為0~5 V,檔位的切換是通過程序來控制ADC0809各個通道的選通來自動實現。只要輸入的電壓范圍超過5 V,則檔位自動切換到另一檔,即選通通道INl。

當輸入電壓范圍為O~5 V時,INO導通。此時U=U26,當輸入電壓范圍為5~50 V時,FPGA判斷選擇檔位,INl導通。此時有U=U27即U=(R1+R3)/(R1+R2+R3)=U26/10。

由于ADC0809數字量輸出為8位,數字量化范圍為0~255,當輸入電壓為滿量程5 V時,轉換電路對輸入電壓的分辨能力為:

![]()

3.3 FPGA內部模塊設計

(1)碼制轉換模塊。在此碼制變換模塊DATA_CONVERSION功能是將AD0809采樣送來的8位二進制數轉換為可被LCD識別的字符型LCD碼。首先,將8位二進制碼變換為BCD碼;然后,再分別進行轉換,得到字符型碼,并送入譯碼顯示模塊。

(2)譯碼驅動模塊。數字電壓值的顯示由LCD實現。選用了HY系列字符型液晶顯示模塊HD44780。實現了低功耗,而且可帶單位雙排顯示,字體美觀大方。

整個電路十分簡潔。系統工作過程:FPGA芯片EP2C5T144對ADC0809及LCD進行初始化。當有輸入信號Vi時,由FPGA向ADC0809傳送控制信號控制字,使其對輸入的模擬信號進行轉換,變為8位的數字信號并送到輸出端。由FPGA經過碼制變換等處理后,再通過LCD的接口驅動,向其發送數據。當ADC0809采樣完成后,FPGA中的碼字轉換模塊將數據轉換為LCD可識別的字符型數據,然后送至驅動模塊,由其驅動LCD,將字符型數據送到LCD的DO~D7端,實現顯示。

4 關鍵算法實現

4.1 檔位自動切換算法

將數字電壓表分為兩個檔位,分別是0~5 V,0~50 V。檔位切換算法如下:

設定初始量程為0~5 V。采集100個數據點,對輸入信號Vi的采樣值取絕對值的最大值,將其作為Vi的最大值的估計值。如果Vi的最大絕對值估計值小于5 V,則將檔位切換到O~5 V,否則,切換到0~50 V。

4.2 信號采樣周期自調整算法

為協調好數據精度和系統負擔兩者之間的關系,對于疊加周期信號的輸入信號Vi,規定單個周期的數據采集不少于8個點,因此要對AD0809的采樣周期進行自適應調整。這里使用過零點檢測的方法,如果疊加信號的周期在0~25 Hz范圍內,采樣周期為5 ms。疊加信號周期在25~50 Hz時,采樣周期為2 ms;疊加信號周期在50~100 Hz時,采樣周期為1 ms。

設采樣周期的初始值為2 ms,采樣數為100點。則有:首先采集100個數據,計算平均值,作為輸入信號Vi的均估值(平均值的估計值);再采集100個數據,與Vi的均估值進行比較,計算過零點的數量并統計;根據此數量,調整采樣周期,當此數量大于20時,令采樣周期為1 ms。當此數量不大于10時,令采樣周期為5 ms。其他令采樣周期為2 ms。

4.3 檢測疊加信號周期算法

依舊采用檢測過零點的數目來檢測周期。

設采集的數據點為1O0個,計算均值,作為輸入信號Vi的均估值;再采集數據,與Vi的均估值進行比較,計算過零點的數量并統計,同時統計每個數據過零點的時刻;檢測到三個過零點時,判斷其是否符合均勻分布,判斷是否檢測到一個周期。若檢測到一個周期,則停止檢測并計算此周期,否則繼續檢測。若檢測到相當數量的數據點,過零點數量仍小于3個,則認為輸入信號為直流信號。

5 程序流程

程序流程如圖6所示。

6 測試結果分析

采用高精度數字多用表UT88B輸出值作為標準值。由表1所示。

由數據對比可以看出,在O~5 V檔位上,該數字電壓表的誤差基本在O.01 V內。在O~50 V檔位上,誤差有所增大,但也控制在O.02 V以內,體現了ADC0809的轉換精度,電路整體設計合理可靠。至于O.02 V以內的偏差,可修改程序,采用軟件的方法進行數據校正,也可以進一步校正A/D的基準電壓。

7 結語

利用現場可編程門陣列技術,設計了該新型數字式電壓表。用軟件替代諸多硬件,在一塊高性能FPGA芯片上,實現采樣時序的控制、檔位的判斷選擇、碼制的轉換和LCD驅動,極大地提高了系統集成度和可靠性。文中重點介紹了檔位電路和FPGA內部模塊的設計以及關鍵算法的實現步驟。由測試結果,可看出該儀表測量范圍較寬,測量精度較高,能夠滿足物理實驗中電量的測量要求。經實際使用證明,系統運行穩定、操作方便。為了方便電壓表系統與計算機直接通信,還可進一步增加RS 232接口,進行電平轉換,可將測得的數據實時導入計算機中使用。