0 引 言

USB(通用串行總線)是英特爾、微軟、IBM、康柏等公司1994年聯合制定的一種通用串行總線規范,它具有數據傳輸速度快,成本低,可靠性高,支持即插即用和熱插拔等優點,迅速得到廣泛應用。

在高速的數據采集或傳輸中,目前使用較多的都是采用USB 2.0接口控制器和FPGA或DSP實現的,本設計在USB 2.0接口芯片CY7C68013的Slave FIFO模式下,利用FPGA作為外部主控制器實現對FX2 USB內部的FIFO進行控制,以實現數據的高速傳輸。該模塊可普遍適用于基于USB 2.0接口的高速數據傳輸或采集中。

l 系統硬件模塊設計

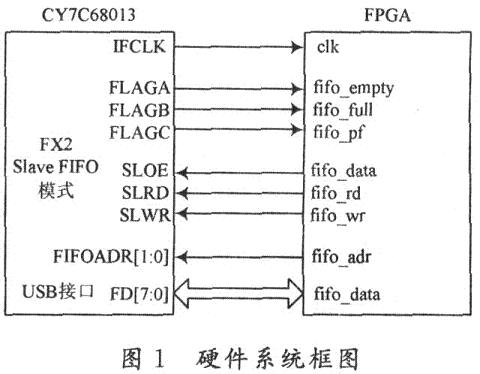

1.1 系統硬件框圖

圖1中展示了Slave FIFO方式下FX2 USB和FPGA的典型連接。其中,FD[7..O]為8位雙向數據總線FLAGA~FLAGC為FX2內FIFO的標志管腳,映射FIFO的當前狀態;SLCS為Slave FIFO的片選信號;SLOE用于使能數據總線FD的輸出;FIFOADR[1..0]用于選擇和FD連接的端點緩沖區(00代表端點2,01代表端點 4,10代表端點6,11代表端點8);SLRD和SLWR可分別作為FIFO的讀寫選通信號。

1.2 USB 2.0接口芯片CY7C68013

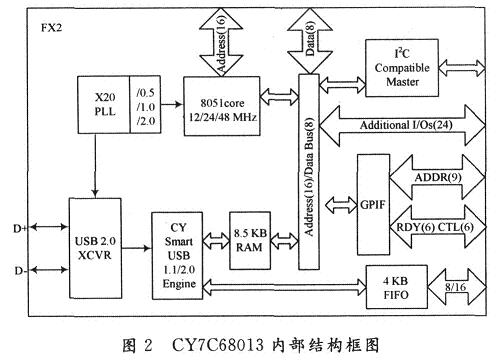

1.2.1 CY7C68013的結構特點

Cypress公司的USB FX2是第一個包含USB 2.0的集成微控制器,它內部集成了1個增強型的8051,1個智能USB串行接口引擎,1個USB數據收發器,3個8位I/O口,16位地址線,8.5 KB RAM和4 KBFIFO等。增強性8051內核完全與標準8051兼容,而性能可達到標準8051的3倍以上。其框圖如圖2所示。

1.2.2 CY7C68013的工作模式

CY7C68013有Ports模式、Slave FIFO和GPIF三種接口方式。

Ports模式是一種最基本的數據傳輸方式,其數據傳輸主要由固件程序完成,需要CPU的參與,因此數據傳輸速率比較低,適用于傳輸速率要求不高的場合。

Slave FIFO方式是從機方式,外部控制器,如FPGA,可像對普通FIFO一樣對FX2的多層緩沖FIFO進行讀寫。FX2內部的FIFO提供所需的時序信號、握手信號(滿、空等)和輸出使能等。這里就是在Slave FIFO模式下實現USB 2.O接口和FPGA的數據通信。

可編程接口GPIF是主機方式,GPIF作為內部主機控制端點FIFO,可以軟件編程讀寫控制波形,幾乎可以對任何8/16 b接口的控制器、存儲器和總線進行數據的主動讀寫,非常靈活。

2 系統軟件模塊設計

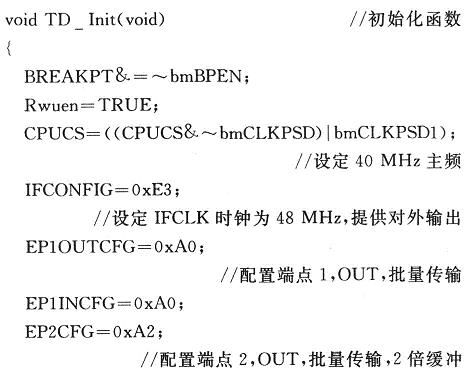

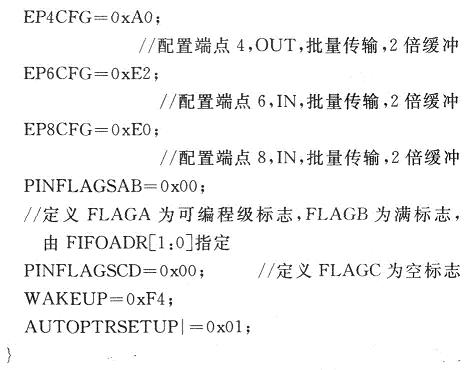

2.1 USB固件程序設計

應用中采用異步FIFO方式,使用內部48 MHz時鐘,自動方式,固件程序采用Cypress公司提供的固件程序框架,在其初始化函數中添加了用戶配置代碼。該設計中異步自動從屬FIFO數據傳輸的初始化代碼如下:

2.2 FPGA控制程序設計

CY7C68013A提供的端口FIFO的讀寫操作,與普通FIFO讀寫操作方式一樣。CY7C68013A為每個端口提供了“空”標志、“滿”標志和“ 可編程級”標志。FPGA檢測這些信號,用于控制讀寫的過程。FPGA在完成這些端口FIFO的操作時,采用Verilog HDL硬件描述語言實現了FIFO的讀寫時序,并在ALTERA公司提供的QuartusⅡ8.O開發工具中綜合編譯并映射到FPGA中運行。

2.2.1 從屬FIFO異步“讀”操作

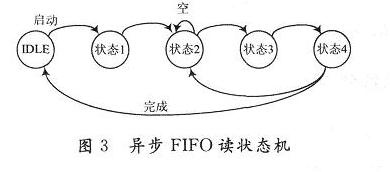

實現異步從屬FIFO“讀”的狀態機如圖3所示。其狀態轉移進程如下:

IDLE:當“寫”事件發生時,轉到狀態1。

狀態1:指向OUT FIFO,激活FIFOADR[1:O],轉向狀態2。

狀態2:激活SLOE,如果FIFO空標志為“假”(FIFO不空),則轉向狀態3;否則停留在狀態2。

狀態3:激活SLOE,SLRD,傳送總線采樣數據;撤銷激活SLRD(指針加1)和SLOE,轉向狀態4。

狀態4:如果有更多的數據要求,則轉向狀態2;否則轉向IDLE。

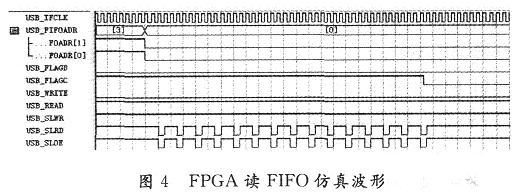

實現以上狀態機的仿真波形如圖4所示。

2.2.2 從屬FIFO異步“寫”操作

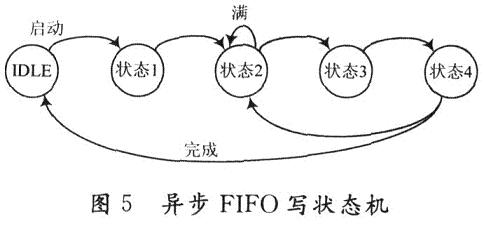

實現異步從屬FIFO“寫”的狀態機如圖5所示。其狀態轉移進程如下:

IDLE:當寫事件發生時,轉到狀態1。

狀態1:指向IN FIFO,激活FIFOADR[1:O],轉向狀態2。

狀態2:如果FIFO滿標志為“假”(FIFO不滿),則轉向狀態3;否則停留在狀態2。

狀態3:傳送總線驅動數據。為一個IFCLK激活SLWR,轉向狀態4。

狀態4:如果有更多的數據要寫,則轉向狀態2;否則轉向IDLE。

用QuartusⅡ進行仿真驗證,其仿真波形如圖6所示,在此過程中USB_SLWR信號很重要,經分析可知,本狀態機實現的FIFO寫控制信號完全正確。

3 實驗結果

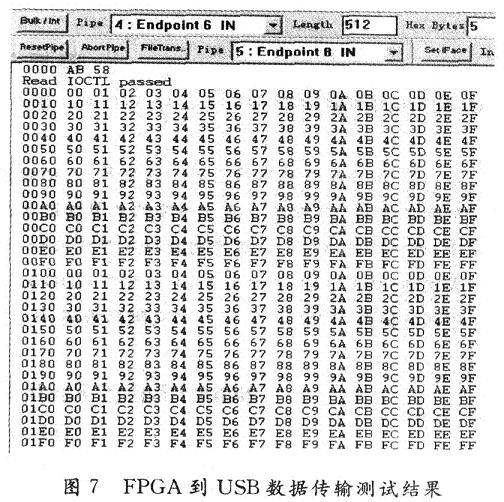

對傳輸的數據進行驗證,可通過FPGA編程生成O~255的數據傳送至CY7C68013的EP6端點,連續傳送兩次,然后利用EZ一USB Control Panel軟件測試所接收到的數據,測試結果如圖7所示,可以看出,數據傳輸準確無誤。

4 結 語

USB 2.0控制器CY7C68013已經被廣泛應用到許多數據傳輸領域,由于USB具有靈活的接口和可編程特性,大大簡化了外部硬件的設計,提高了系統可靠性。該設計可擴展性好,已經被應用于數據傳輸與采集的板卡上,經實際測試,沒有出現數據的誤碼等錯誤,數據傳送正確,傳輸速率可達30 MHz/s以上,滿足設計要求。