引言

隨著半導體工藝技術的發展,IC設計者已能將微處理器、模擬IP核、數字IP核和存儲器(或片外存儲控制接口)集成在單一芯片上,即SoC芯片。對片上系統(SoC)數據記錄需要低功耗、大容量、可快速重復擦寫的存儲器。常用的介質主要有:動態存儲器(DRAM)、靜態存儲器(SRAM)和閃速存儲器(FLASH MEMORY)。DRAM容量大,但需要不斷刷新才能保持數據,會占用微處理器時間,同時增加了功耗;SRAM雖然不需要動態刷新,但價格太貴,并且斷電后跟DRAM一樣數據都無法保存。FLASH MEMORY是一種兼有紫外線擦除EPROM和電可擦除可編程只讀存儲器(EEPROM)兩者優點的新型非易失存儲器。由于它可在線進行電可擦除和編程,芯片每區可獨立擦寫至少1000 000次以上,因而對于需周期性地修改被存儲的代碼和數據表的應用場合,以及作為一種高密度的、非易失的數據存儲介質FLASH是理想的器件選擇。在我們設計的系統中,處理器是Openrisc1

200,所用的FLASH是AMD與富士公司的Am29LV160D芯片。利用FPGA實現接口,由于Openrisc1200(OR1200)采用WISHBONE總線,所以本設計的接口具有可移植性。

Am29LV160D芯片特點

Am29LV160D是一種僅需采用3.0V電源進行讀寫的閃存。該器件提供了70ns、90ns、120ns讀取時間,無需高速微處理器插入等待狀態進行速度匹配。為了消除總線競爭,芯片引入了片選使能(CE#),寫使能(WE#)和輸出使能(OE#)控制端口。芯片采用分塊結構,非常適用于要求高密度的代碼或數據存儲的低功耗系統。

● 甚低功耗

工作在5MHz時, 電流典型值為:

睡眠模式下電流為200nA;

備用模式下電流為200nA;

讀數據時為9mA;

編程/擦除模式下電流為20mA。

● 靈活的分塊結構

一個16KB,兩個8KB,一個32KB,和31個64KB塊(字節模式);

一個8KB,兩個4 KB,一個16 KB,和31個32 KB塊(字模式);

支持整個芯片擦除;

復雜的塊保護特性。

● 具有內部嵌入算法

內部嵌入擦除算法自動預編程和擦除整個芯片或任意塊的組合;

內部嵌入算法自動將給定地址的數據寫入芯片及對其校驗。

● 與JEDEC標準兼容

● 具有硬件RESET復位與Ready/Busy擦寫查詢管腳

● 具有擦除暫停與擦除繼續功能

|

|

圖1

WISHBONE總線簡介

WISHBONE總線規范是一種片上系統IP核互連體系結構。它定義了一種IP核之間公共的邏輯接口,減輕了系統組件集成的難度,提高了系統組件的可重用性、可靠性和可移植性,加快了產品市場化的速度。WISHBONE總線規范可用于軟核、固核和硬核,對開發工具和目標硬件沒有特殊要求,并且幾乎兼容所有的綜合工具,可以用多種硬件描述語言來實現。

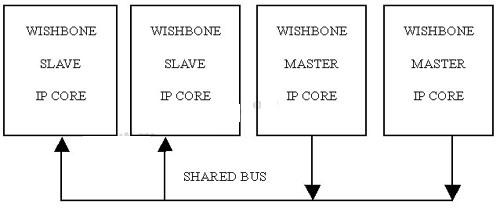

靈活性是WISHBONE總線的另一個優點。由于

IP核種類多樣,其間并沒有一種統一的間接方式。為滿足不同系統的需要,WISHBONE總線提供了四種不同的IP核互連方式:

點到點(point-to-point),用于兩IP核直接互連;

數據流(data flow),用于多個串行IP核之間的數據并發傳輸;

共享總線(shared bus)(見圖1),多個IP核共享一條總線;

交叉開關(crossbar switch),同時連接多個主從部件,提高系統吞吐量。

FLASH接口的設計

|

|

圖2

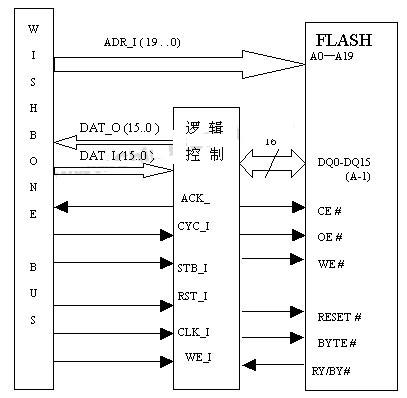

由于OR1200采用的是WISHBONE共享總線,其地址線為32位,數據線也為32位。設計中采用將低位與FLASH相聯接,并將接口位度設計為16位。原理框圖如圖2所示。邏輯接口部分采用FPGA來實現。系統選用Xilinx公司最新推出的90nm工藝制造的現場可編程門陣列芯片Spartan-3來實現接口設計,利用它的可編程性特性帶來了電路設計的簡單化和調試的靈活性。

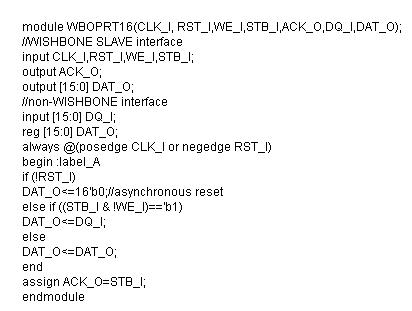

FLASH讀接口設計

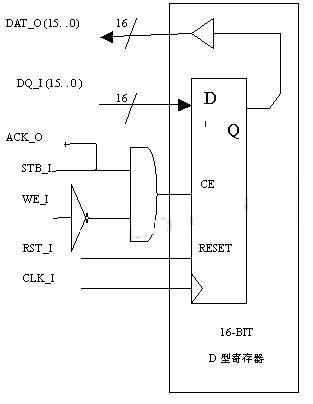

該接口可實現單周期讀與塊讀功能,時序部分與WISHBONE兼容。由于采用的FLASH最大讀周期時間至少為90ns,故只有在總線時鐘工作在10MHz以下頻率時可以直接將ACK_O端口與STB_I端口相聯。當MASTER(指令CACHE)發出塊讀信號時,將發出一個LOCK_O=VIH信號給總線仲裁器,要求總線能不間斷提供總線。其對SLAVE(FLASH接口部分)控制信號為:

WE_I=VIL,CYC_I=VIH,STB_I=VIH,BYTE=VIH

當MASTER結束塊讀時發出STB_O= VIL信號即可。其輸出接口部分如圖3所示。該輸出接口模塊源代碼如下:

|

|

圖3

FLASH寫接口設計

因為FLASH寫命令需要多個時

鐘周期時間,其中采用Unlock Bypass模式時為2個時鐘周期,采用正常寫模式需要4個時鐘周期,并且在對FLASH寫和擦寫時更是需要等待幾十微秒到幾秒鐘的時間,因此對接口SLAVE必須引入寫或擦寫完成狀態信號來控制總線數據的傳輸。為簡化設計采用RY/BY引腳來判斷。輸出端口原理圖與圖3類似,只需對部分端口進行修改即可。

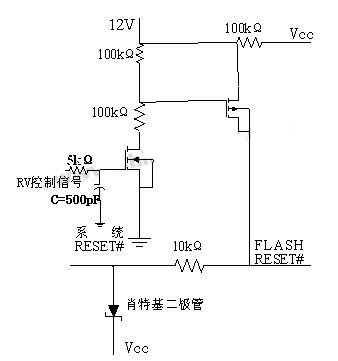

為了能夠對塊保護的程序代碼進行升級,特別設計了一個12V電源電路來實現暫時塊寫保護解除功能,如圖4所示。利用Am29LV160D芯片提供的暫時塊寫保護解除模式——即通過對RESET#引腳加VID電壓。在該模式下先前被保護的塊可以通過塊地址選中來進行編程和擦除。并且一旦VID移除所有先前保護的塊恢復到保護狀態。

|

|

圖4

圖4中RV控制信號處采用了R=5kΩ,C=100pF,以便使得VID電壓上升時間與下降時間≥500ns,從而滿足相應的時序要求。肖特基二極管的引入保證了系統RESET信號被鉗制在Vcc+0.3V以內。總體上來說,該電源隔離電路的引入對整個系統的成本影響很小,而使系統可以在線編程被保護的FLASH存儲塊。

總結

本文介紹了AMD公司Am29LV160D芯片特點,并在此基礎上設計了基于WISHBONE總線的接口。該接口設計方法對其他相關SoC總線接口設計具有直接的參考意義。