引言

隨著數字信號處理芯片性價比的不斷提高,數字信號處理的應用領域飛速發展,同時Pentium高速CPU的出現,要求有極高的數據通量予以支持,而低速的ISA總線在解決這些問題方面逐漸無能為力,取而代之的是高速的PCI總線。PCI總線可將高速外圍設備直接掛在CPU總線上,33MHz/32位時數據傳輸速率可達132MB/s,66MHz/64位時更是性能加倍,打破了數據傳輸速率的瓶頸,使得CPU的性能得到充分發揮。如果采用美國TI公司生產的高速高性能數字信號處理器DSP取代原來的單片機作為板載CPU,可以充分利用PCI總線的優點直接將采集的數據傳到微機內存,有效地解決了數據的實時傳輸和存儲問題。

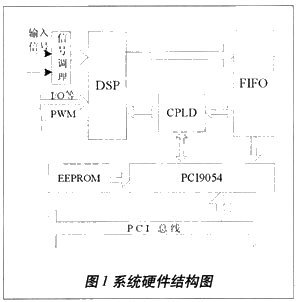

測控系統的硬件組成

系統基本硬件結構如圖1所示。整個高速測控系統主要由信號調理電路、DSP模塊、FIFC)存儲器、CPLD控制電路、PC19054接口芯片等組成。系統采用主從結構,PC機作為上位機,用于完成對系統的控制(如AD轉換的開始、DSP復位、中斷響應、數據接收與處理等)。DSP作為下位機,用于完成數據的采集與處理、PWM波以及其他外圍信號的控制等。

DSP測控模塊介紹

系統采用的DSP芯片為TI公司的TMS320LF2407。電路設計時,利用的DSP內部的16通道A/D轉換實現數據采集,DSP與FIFO的電路接口電壓都為3.3V,可實現無縫連接,DSP的數據總線直接與FIFO的數據輸入端口相連,DSP與FIFO的時鐘頻率應設為相同。這樣,無需插入等待周期,控制信號經CPLD直接轉換為FIFO的讀寫信號,實現數據的高速存儲。

先進先出存儲器

在DMA傳輸方式下,由于PCI9054內部的FIFO只有32級深度,實時傳送高速數據時,PCI9054內部的FIFO會很快存滿,而DSP內的數據仍會源源不斷的傳送過來,易造成數據的丟失,因此必須要擴展外部FIFO。

本系統采用I D T公司高速CMOS同步FIFO芯片IDT72V3660,它的容量為4096×36bit;有高達100MHz的讀寫速度;可以兼容3.3V和5V兩種接口電壓。該FIFO具有標準的"滿"(FF#)、"半滿"(HF#)、"空"(EF#)等標志。系統可以根據這些標志信號控制對FIFO的讀寫操作。在CPLD的邏輯控制下,當WEN#有效時,在WCLK的每一個上升沿,FIFO會把輸人數據線上的數據存入內部存儲器。當REN#有效且輸出允許(OE#有效)時,在RCLK的每一個上升沿,FIFO會把內部存儲器中的數據發送到輸出數據總線上(低電平用"#"表示)。

控制邏輯芯片CPLD

本系統采用Altera公司的EPM7128來實現系統的邏輯控制,主要包括DSP控制邏輯、FIFO控制邏輯、PCI9054接口控制邏輯三個部分,其中,對PC219054的邏輯控制是設計的重點。設計中利用MaxPlusⅡ軟件進行VHDL語言編程、仿真和調試。

PCI9054及外部接口分析

PCI與板載CPU的橋接有兩種設計方案,一種是采用FPGA,通過軟件編程實現硬件功能。另一種是利用專用PCI橋接芯片,適合快速開發的場合。

本系統采用PLX公司的PCI總線專用接口控制芯片PC19054。它符合PCIV2.1和PCIV2_2規范;可同時支持3.3V和5V兩種信號環境;提供了兩個獨立的可編程DMA控制器;內部有6種可編程FIFO,以實現零等待突發傳輸及局部總線和PCI總線之間的異步操作;在PCI總線端支持33MHz/32位,傳輸速率最高可達132MB/s;在局部端可編程實現8/16/32位的數據寬度,支持復用/非復用的32位地址/數據,時鐘最高可達50MHz。

PCI9054局部總線可工作在M、J、C三種模式,M模式是專門為Motorola公司的 MPC850和MPC860提供直接非復用的接口;J模式地址/數據線復用;C模式與J模式差別不大,但地址/數據線非復用,更符合連接習慣。本設計采用C模式。

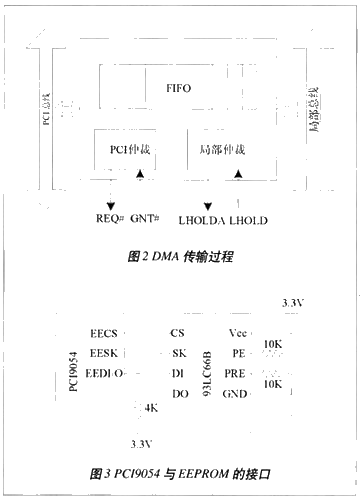

PCI9054的數據傳輸模式可分為主模式、從模式、DMA模式。模式的選擇主要根據硬件設計者對硬件的設計需要而定。本系統采用DMA模式,在DMA傳輸模式下,PCI9054既是PCI端的主控方,又是局部端的主控方。

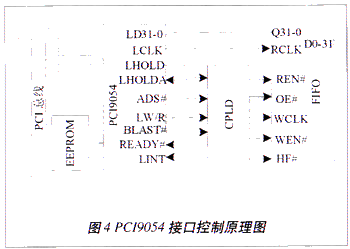

PCI9054集成了兩個互相獨立的DMA通道,每個通道都支持Block DMA和Scatter/(3ather DMA,其中通道0還支持請求(Demand)DMA傳輸方式。當有通道進行DMA傳輸時,DMA控制器將發起對局部總線和PCI總線操作,其傳輸過程如圖2所示。 PC219054提供了三個物理總線接口:PCI總線接口、EEPROM接口、局部總線接口。PCI總線接口依照PCI擴展板上定義的引腳分配情況將彼此對應的信號連接在一起即可。本系統采用的EEPROM為4K、3.3V串行的93LC66B,通過對PCI時鐘分頻來產生EEPROM時鐘,內部存放PCI9054的配置信息,系統加電時PCI9054自動加載EEPROM中的配置信息,并由BIOS通過PCI總線對配置寄存器讀寫,來完成各種控制功能。接口電路如圖3所示。

PCI9054在DMA傳輸方式下,通過設置其DMA控制器內部的寄存器即可實現兩總線之間的數據傳送。傳輸過程由以下幾個步驟實現:

1.設置傳輸方式寄存器:通過寄存器DMA MODE0或DMAMODE1的位9來設置DMA通道的傳輸方式,置0表示Block傳輸,置1表示Scatter/Gather傳輸;

2.設置命令/狀態寄存器:啟動/停止DMA操作,并讀此寄存器返回DMA狀態;

3.設置描述寄存器:設置DMA的傳輸方向;

4.設置傳輸計數寄存器:以字節為單位設置傳輸數據量;

5.設置PCI地址寄存器:設置PCI總線側的地址空問;

6.設置局部地址寄存器:設置局部總線側的地址空間。 當進行數據采集時,由應用程序或通過DSP的外部引腳(pi

n21)向DSP發出采集命令,同時復位FIFO,在13SP內部程序和CPLD的控制下,數據經DO-31源源不斷地輸入到FIFO中,當FIFO半滿時發出半滿標志信號(HF#),CPLD接到半滿信號后,立即向PCI9054發出中斷請求信號(LINT),驅動程序響應中斷,在中斷響應程序內,發出讀命令、要讀取的字節數、傳輸方向、地址信號等,PCI9054設定"DMA傳輸開始位"啟動數據傳輸,當ADS#為低(有效),BLAST為高(無效),LW/R為低(有效)時,表明PCI9054開始一個有效的讀數據周期,CPLD產生一個低電平信號REN#給FIFO,同時作為Ready信號返回給PCI9054, 表明已準備就緒。直到ADS#為高(無效)且BLAST#為低(有效)時,表明PCI9054已經開 始最后一個周期,同時設定D M A"傳輸結束位"結束DMA操作,此時REN#信號再次變高電平(無效),完成一次數據突發傳輸。接口電路如圖4所示。

該系統的軟件設計主要包括DSP測控程序、PCI設備驅動程序和Windows應用程序三個部分。驅動程序是連接硬件系統和應用程序的橋梁,是整個測控系統開發中的關鍵一步。在此簡單介紹一下PCI設備驅動程序開發過程。

在Windows環境下共有三種類型的驅動程序,分別是VXD、NT、WDM。因為WDM可以應用在windows98/2000/XP下,支持即插即用、電源管理、WMI等功能,是Windows NT驅動體系基礎上發展起來的未來主流驅動程序體系,所以為這里選擇設計WDM驅動程序。

開發工具選擇Compuware公司提供的DriverStudio完~成驅動程序的開發,DriverWorks是DriverStudio中的一個部分,DriverWorks中的類庫封裝了針對驅動程序的各種通用操作,使用其中的DriverWizard向導功能,能夠非常方便地實現WDM驅動程序的開發。

其中PCI配置空間的訪問采用KPciConfiguration實現。I/O訪問采用DriverStudio中的KIoRange類實現。硬件中斷響應的處理可以采用Kinterrupt類實現。DMA讀主要是利用三個類來實現數據傳輸,分別為:KDmaTransfer、KdmaAdapter和K C o m m o n D m a B U ff e r。KDmaTransfer用于DMA傳輸控制。KdmaAdapter用于建立一個DMA適配器來說明DMA通道的特性。KCommonDmaBuffer用于申請系統提供的公用緩沖區。

執行過程中驅動程序首先設置PCI9054的工作方式和中斷寄存器、DMA配置寄存器,然后等待本地中斷的到來。當FIFO半滿時表明本地中斷到來,在設備成員函數Isr_IrqO中屏蔽本地中斷,在設備成員函數DpcFor_Irq()中調用KDmaTransfer:Continue()函數進行DMA傳輸。一次數據傳輸完畢后,驅動程序通過操作系統將內核中的數據拷貝到用戶態內存,交給應用軟件處理。

結語

在實驗室中利用PCI9054作為接口芯片的高速測控系統,可實現持續數據傳輸速率達50MB/s,且系統運行穩定,具有廣泛的應用前景。