摘 要: 介紹了基于CPLD的刷卡式電腦聯網集控型自動存包系統的設計,并對系統的軟硬件構成、CPLD內部邏輯設計、工作原理等進行了詳細說明。該系統速度快、安全性好、可靠性高,而且具有操作簡便、查詢快捷、便于實時監控等特點。

關鍵詞: CPLD 電子存包 串行通信

近年來,隨著信息科技的發展,電子存包系統由于其安全性高、可靠性高、方便快捷等特點,在車站碼頭、超市、圖書館、賓館、游泳館、俱樂部等公共場所及機關、企事業單位文件檔案管理等部門得到了廣泛的應用,有著廣闊的市場前景。

1 系統組成

本文所介紹的電子存包系統是一種電腦聯網集中控制的磁卡式自動存包系統。如圖1所示,系統由集控計算機和分機兩級監控系統對存包柜進行監視與控制。

集控計算機(簡稱主機)為用戶分配箱位和密碼,通過與其連接的磁卡讀寫器" title="讀寫器">讀寫器將密碼寫入磁卡中交給用戶。主機使用特定的通信協議查詢和控制各個分機,然后由分機對其下屬箱位進行控制。主機與分機之間采用RS-485接口連接。RS-485在傳輸距離為1200米時速度可達100kbps、傳輸距離遠、可靠性很高,而且用于多點互連時很方便,可以省掉很多信號線,非常適合用于分布式系統中。

分機具有接收并緩存讀卡器數據、與主機通信、控制存包柜動作等功能,主要由CPLD芯片、光耦合模塊、讀磁卡模塊、紅外探測模塊、電磁鎖驅動模塊等外圍電路組成。CPLD芯片選用Altera公司的EPM3256A TC144-10,其技術參數如表1所示。

在本設計中,所有的控制與通信功能全部集成到CPLD內部,充分發揮了CPLD使用靈活、測試方便、可靠性好等優點。

2 硬件設計

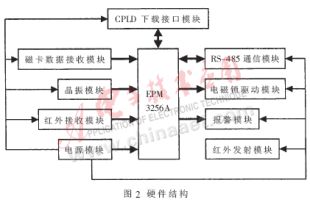

2.1基本硬件組成

電子存包系統的基本硬件結構,即分機的硬件組成如圖2所示。

電源模塊使用變壓器將220V交流電變為9V交流電,然后經過整流、穩壓輸出3.3V、5V、12V三路直流電對分機系統供電。其中,3.3V直流電對CPLD供電,5V直流電對外圍電路供電,12V直流電用來驅動電磁鎖。

磁卡數據接收模塊" title="接收模塊">接收模塊主要由一片MAX202和一個9幀D型接口以及五個0.1μF電容組成,當用戶刷卡動作完成時,磁卡中密碼數據立即被傳送至CPLD中暫存。當主機輪循至該分機時,分機將密碼發送給主機。

晶振模塊利用4060分頻器和4020分頻器對2.4576MHz晶振頻率進行分頻,分別得到9600Hz、153600(9600×16)Hz、2.35Hz的頻率信號作為CPLD的輸入時鐘信號。

紅外線發射與接收模塊的作用是利用紅外線檢測各個存包柜內是否有物品,通過紅外接收模塊將檢測結果反饋到CPLD,然后由CPLD發送給主機。

RS-485通信模塊中使用了光耦器件4N25進行光電隔離以抑制噪聲對通信線路的干擾,并由一片RS-485收發器芯片SN75LBC184實現TTL電平與RS-485電平之間的轉換。

電磁鎖驅動模塊負責對CPLD輸出的3.3V開門信號進行放大,以驅動電磁鎖進行開門動作。為保證輸出功率,采用了二級直流放大,電磁鎖由末級功放管BD241驅動。每個分機控制八個箱位,因此如圖3所示的驅動電路共有八路。

另外,本系統還選用了三晶公司生產的SJE-102磁卡讀寫器和SJE-451讀卡器作為磁卡讀寫設備,分別與主機、分機相連接。

2.2 CPLD內部邏輯設計

CPLD內部邏輯的頂層原理圖如圖4所示。由圖可見,CPLD內部邏輯電路由主控模塊(main)、串行數據" title="串行數據">串行數據收發模塊(s8)、磁卡數據接收模塊(mag_s8)、磁卡數據緩存" title="數據緩存">數據緩存模塊(mag)以及開門信號延時模塊(door)和報警模塊(beep)幾部分組成。

2.2.1 主控部分的設計

主控模塊主要由一個狀態機實現,采用VHDL語言描述。該狀態機共有四個狀態,分別是等待偵聽狀態、等待尋址幀狀態、發送密碼及箱位號碼并接收主機開箱信號狀態和接收主機強制開箱信號狀態。

在這里采用全0幀“00000000”作為復位幀,當接收到復位幀時,系統立即返回等待偵聽狀態;采用全1幀“11111111”作為起始標識幀,在等待偵聽狀態下接收到全1幀時則轉入等待尋址幀狀態。尋址幀分為一般尋址幀和強制開箱尋址幀兩種。一般尋址幀由四位分機編號+“1000”組成,而強制開箱尋址幀由四位分機編號+“0001”組成。當分機在等待尋址幀狀態下收到這兩種尋址幀時便分別轉入發送密碼及箱位號碼狀態和接收主機強制開箱信號狀態。

2.2.2 串行數據收發部分的設計

本設計有兩個串行數據發送與接收模塊,分別用于與主機通信和接收磁卡數據,采用的通信速度都是9600bps。這兩部分的設計思想是統一的,其中磁卡數據接收模塊只用到了串行數據的接收技術。

在發送電路的設計中,利用clk端口的9600Hz時鐘信號,根據所采用的幀格式,將主控模塊得到的并行數據DATAIN[7..0]前后分別加入起始位、奇偶校驗位和停止位后串行輸出到端口TXD。

在接收電路的設計中,接收電路始終用16倍波特率的時鐘CLK16采樣串行數據接收端RXD端口的狀態。在檢測到由“1”到“0”的變化時,若連續采樣8次,RXD一直都保持為“0”,則認定是數據的起始位;否則認為是干擾信號,計數器將被復位,重新開始采樣。在確認起始位后,每隔16個CLK16信號周期讀取一次數據位,這樣保證了恰好在每個數據的中點讀取,直至停止位。一幀接收完畢后,接收計數器復位,開始偵聽下一幀的起始位。采用這種接收方法不但可以減少誤判起始信號,而且還允許發送時鐘和接收時鐘的頻率有一定的誤差。

在實際應用中,如果在檢測到RXD下降沿后連續采樣8次為“0”才確認起始位,那么起始位被忽略的情況時有發生。經過實驗與分析,發現這是由于CPLD外圍的光耦器件4N25的開關速度較慢的緣故,于是改進了設計。在檢測到RXD下降沿后,從第三個CLK16信號周期開始計數,連續采樣6次,如果6次全為“0”,即認定是起始位。采用這種方法后誤判率為0,大大提高了系統的可靠性。

2.3 其它模塊

磁卡數據緩存模塊的功能相當于一個緩存器,將磁卡數據接收模塊接收到的數據暫存,等待主控模塊的調用;開門信號延時模塊為外圍的電磁鎖驅動電路提供大約1秒鐘寬度的開門脈沖信號以保證電磁鎖動作所需要的必要通電時間;報警模塊用于提示用戶刷卡成功與否。

由于磁卡數據緩存模塊和開門信號延時模塊占用了很大一部分的片內寄存器資源,在對這兩部分的設計中改用了原理圖輸入方法。相對于使用VHDL語言進行描述,采用這種方法可以更精確地確定寄存器的數量,減少不必要的寄存器。實踐證明,采用這種輸入方法,綜合后的芯片使用率降低了6%(16個LC),提高了芯片功能的可擴展性。

3 軟件設計

本系統的軟件編程工具采用C++ Builder6.0,實現了動態分配箱位號碼和密碼、寫磁卡、輪循分機、校驗密碼并發送開箱信號、顯示系統運行狀態、生成系統運行日志等功能。

由于在系統運行過程中有多項任務需要同時進行,設計采用了多線程技術。在后臺,主機使用查詢的方式不斷地輪循各個分機,當進行寫磁卡操作時,程序另外開辟一個線程對磁卡讀寫器進行操作。

串行通信" title="串行通信">串行通信控件采用TurboPower公司的Async Professional控件集中的TapdComPort控件,該控件功能完善,是目前穩定性和可靠性最高的串行通信控件。

在設計時要特別注意的是一定要保證主機軟件與分機硬件之間通信協議的一致性,要充分考慮到分機CPLD中狀態機各狀態轉換的各種可能,避免出現死鎖情況。

參考文獻

1 Altera Ltc.Max3000A PLD Family Data Sheet[Z].Altera Corporation,2003

2 潘 松,黃繼業.EDA技術實用教程[M]. 北京:科學出版社,2002

3 雷麗文,朱曉華,蔡征宇,繆均達. 微機原理與接口技術[M].北京:電子工業出版社,1997