0 引言

近年來,隨著鐵路建設的跨越式發展,對機車信號檢測的準確性和可靠性提出了越來越高的要求,傳統的手持式信號檢測系統已經遠遠不能滿足需要,本文提出的車載信號采集系統采用數字信號處理(DSP)技術實現對機車信號波形的頻譜分析。利用可靠的硬件和軟件技術實

現機車信號檢測的實時性和高精度要求。系統采用USB總線接口有效地解決了傳統總線形式(如RS232、并口、ISA等)傳輸速度低、安裝繁瑣、易受機箱內環境的干擾、計算機系統資源限制等缺點,具有廉價、高速、支持即插即用、使用維護方便等優點。

1 系統總體設計

本數據采集系統的設計主要分為硬件和軟件設計兩部分。其中硬件設計主要包括信號調理、A/D轉換、數據存儲、控制部分以及USB接口部分等實現內容。

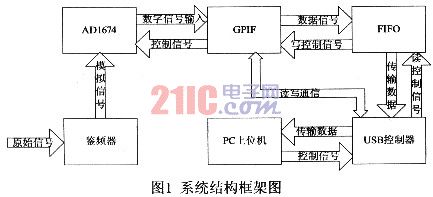

系統軟件設計分為USBN件(Firmware)、USB設備驅動程序以及主機應用程序三部分內容。在Windows操作平臺下,主機應用程序通過USB設備驅動程序與系統硬件接口USBDI(USBDeviceInterface)進行通信,然后由系統產生USB數據的傳送動作。固件則是運行在接口芯片中的代碼,用以響應各種來自系統的USB標準請求,完成數據的交換工作和事務處理。系統結構框架圖如圖1所示。

2 系統硬件設計

USB數據采集板硬件電路設計實現共分為5大部分,它們分別是信號調理、A/D轉換、數據存儲、控制部分以及USB接口部分。

2.1 信號調理

信號調理部分由脈沖計數式鑒頻器完成。它由四部分組成(如圖2所示),即過零比較器、微分電路、脈沖形成電路和低通濾波器,輸入的調頻波Ui(t)經過零比較器后變成調頻方波信號U1(t),調頻方波信號通過微分電路后變為微分脈沖序列U2(t),微分脈沖序列經過脈沖形成

電路后變為等脈寬的方波脈沖序列U3(t),等脈寬的方波脈沖序列通過低通濾波器后就輸出調制信號Uo(t)。鑒頻器各部分的波形如圖3所示。

|

2.2 主控芯片的工作方式

本設計采用的主控芯片是Cypress公司的USB2.0控制芯片CY7C68013,它與計算機通過USB接口相連,使設備能在PC機的控制下進行操作。USB主控芯片通過邏輯控制電路連接到FIFO和A/D轉換后的數據傳送至FIFO芯片進行緩沖,緩沖后的數據輸入主控芯片的從FIFO中,

然后從FIFO以DMA(直接內存存取)的方式經由SIE(串行接口引擎)傳給PC機。

為了實現高速數據采集的功能,A/D芯片采用的ADl674,它是一款12位,最高轉換速度可達100kHz的A/D轉換芯片,考慮到對FIFO容量的需求,系統采用GPLD和FIFO來實現。選用IDT7205完成數據緩存。其最高工作頻率為133MHz,容量為8kB,能滿足設計要求。

CY7C68013與外設有兩種接口方式:通用可編程接口GPIF方式和從屬FIFO方式。GPIF的核心就是一個可編程狀態機,可產生6個控制和9個地址輸入信號,并能接收6個外部和2個內部“ready”輸入信號。GPIF向外部接口產生正確的選通信號和握手信號,外部接口用于對FIFO數據的傳進和傳出。GPIF是主機的方式,而從屬FIFO方式是從機方式,它由外部控制器控制,可像對普通FIFO一樣對FX2的多層緩沖FIFO進行讀寫。FX2的從屬FIFO工作方式可設為同步或異步,工作時鐘可選為內部產生或外部輸入,其它控制信號也可根據需要設置為高有效或低有效。

2.3 FlF0的數據緩存作用

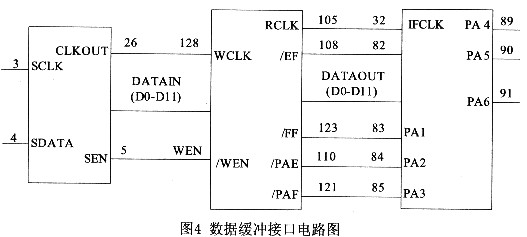

由于A/D最高采樣頻率可達100MHz,而主控芯片CY7C68013中的FIFO只有4kB,不能滿足A/D數據轉換器的要求,因此需要在A/D和CY7-C68013之間增加一個高速的FIFO來緩存數據。FIFO是先進先出的數據緩存器,數據在其內部順序寫入、順序讀出,其數據地址由內部讀寫指針自動加1完成。它具有雙口輸入輸出、采集傳送速度快等特點,能滿足高速數據傳輸的要求。由FIFO構成的數據緩沖電路主要部分的接口電路如圖4所示。

IDT7205有兩種工作模式,即IDT標準模式和FWFT模式。本設計中采用IDT標準模式,這種模式通過FF、PAF、PAE、HF、EF五個標志位來實現數據的傳輸。/WEN(寫使能端)置為有效時,數據可以寫入FIFO。在WLCK(寫時鐘)的控制下,數據持續寫入FIFO,當第一個數據被寫入時,/EF(空標志)無效,數據不斷地寫入FIFO,即將寫滿時/PAE(將空標志)無效,/PAF(將滿標志)有效,表示FIFO即將寫滿。當FIF0寫滿時,/FF(滿標志)置為有效,控制A/D芯片停止寫數。開始讀數據時的第一個讀操作使/FF置為無效,此時開始持續地讀取數據,當FIFO中數據減少到一定程度,會使/PAF(將滿)和/HF(半滿)兩個標志位置為無效,持續讀出數據,而不寫入數據;當FIFO中只剩下N個字時(N為空狀態的缺省值),/PAF有效;當FIFO中的數據被全部讀出時,/EF置為有效,此時控制主控芯片停止讀取數據,與此同時A/D也開始下一個讀取數據過程。

3 系統軟件設計

3.1 固件設計

USB固件是運行在FX2芯片CY7C68013中的代碼。在數據采集卡連接到計算機后,通過一個能自動完成固件下載以及設備重枚舉功能的設備驅動程序,即固件下載驅動程序將USB固件下載到FX2的RAM中。

Cypress公司針對FX2系列的USB芯片給出了一個Firmware(固件)庫,用戶只需要在源程序中包含進EZUSB.H和EZREGS.H, 并且把EZU-SB.LIB和USBJMPB.OBJ添加進項目即可。

在設計中還利用了FX2的框架。FX2程序框架用于加速開發芯片外設。框架為FX2的初始化、處理設備標準USB設備請求以及USB掛起時的電源管理提供了現成的805l代碼,只需簡單地提供USB描述符表,編寫完成外設功能的代碼就可以開發一個功能完善的USB外設。

CY7C68013芯片的端點數總共有7個,根據設計需要,我們選擇了其中的3個端點,其中1個控制端點、1個發送端點和1個接收端點。

3.2 驅動程序

在采集卡工作的運行WindowsxF臺的主機上,Cypress公司提供了Windows下的通用驅動程序(GDP)。本采集卡使用這個通用驅動程序,不需要自己另行開發。

3.3 用戶程序設計

用戶程序設計部分則是基于C++Builder開發平臺,設計并實現數據采集系統的功能。系統軟件總體上包括數據采集(通道控制、觸發控制)、波形顯示、參數測量、頻譜分析及波形存儲與回放等五大模塊。軟件界面如圖5所示。

3.3.1 數據采集模塊

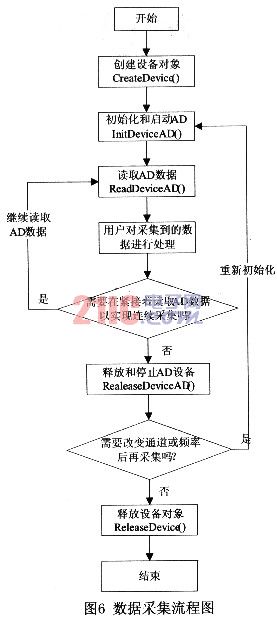

數據采集模塊在整個系統中占有重要的地位,它是系統的核心。其工作流程圖如圖6所示,本模塊主要完成通道控制、觸發控制等功能。數據采集部分的參數設置正確與否,直接影響到后面的分析、處理、顯示等功能能否實現。這部分的參數設置主要包括:

(1)通道控制。主要包括通道個數控制,系統提供的通道數為末通道數減去首通道數加1。

(2)觸發控制。主要包括觸發方式、觸發類型、觸發方向、時鐘源選擇等。

3.3.2 波形顯示模塊

波形顯示模塊主要應用Chart實現波形顯示。波形圖顯示信號時域特性。系統可以顯示任意形狀的波形信號。對波形曲線進行操作,包括移動、對研究區域放大和縮小等。

3.3.3 參數測量模塊

參數測量模塊主要實現波形的參數測量、分析功能,完成包括各通道信號的載波頻率以及實際采樣頻率等幾個參數的測量,并顯示其測量結果。參數測量模塊程序設計實現中,主要應用了循環結構中的While循環。

3.3.4 頻譜分析模塊

頻譜分析模塊采用FFT算法,完成數據信號的頻譜分析。頻譜分析功能主要實現時域信號和頻域信號的轉換。

3.3.5 波形存儲和回放

為了實現對波形數據及各種測量數據的有效管理,可將這些數據予以存儲和回放。

(1)波形存儲。開始采集之前系統自動提示用戶創建新文件。系統可以同時保存多通道的時域波形數據,并且只要計算機硬盤或軟盤空間足夠大,可以保存無數次波形數據。從而擺脫了傳統數字存儲系統的存儲容量的限制。

(2)波形回放。“回放”按鈕控制是否從數據文件中讀取波形數據。從軟盤或硬盤上讀取的波形數據,顯示在實時采集的波形顯示窗口,并保留在顯示窗口。當看完讀取的波形后,要回到實時采集的狀態,點擊前面板上的“采集”按鈕,進行讀取與采集的切換。并且系統特有的輸出功能可以實現語音信號的同步回放。為了節約成本我們用計算機的聲卡代替D/A轉換器,將采集的語音信號通過聲卡輸出。

4 結束語

由于采用CY7C68013芯片作為主控制器,其靈活的接口和可編程特性簡化了高速數據采集系統外部硬件的設計,提高了系統的可靠性;由于A/D轉換電路采用ADl674,保證了數據采集系統的高速性和高精度。此設計方案可改善現有的數據采集系統存在的控制復雜、傳輸效率低、模擬量噪聲大等問題,能實現低成本、高可靠性、高速、高精度和高穩定性的多點數據采集,并且適合車載作業。