摘? 要: 闡述了基于VXI總線的時鐘源" title="時鐘源">時鐘源模塊的組成及基本原理。在該時鐘源模塊中,用FPGA器件實現VXI總線寄存器基接口電路" title="接口電路">接口電路,用ECL器件完成功能電路,采用移位寄存器實現可編程延遲時間的調節。該時鐘源模塊具有經濟實用等特點。

關鍵詞: VXI總線? FPGA器件? 時鐘信號" title="時鐘信號">時鐘信號? ECL

?

在高速數字電路系統的設計中,時鐘占有非常重要的地位,系統時鐘性能的好壞,直接影響到整個電路系統的性能。在研制VXI總線數字輸入/輸出模塊的過程中,需要用到六路激勵時鐘信號和六路響應時鐘信號,激勵時鐘信號和響應時鐘信號存在延時關系。對于不同的測試電路,激勵時鐘信號和響應時鐘信號的延時時間長度可編程調節。該時鐘源輸出時鐘頻率范圍為40MHz~1Hz;頻率的準確度為0.01%;時鐘頻率穩定度為1×10-5;時鐘帶負載能力不小于8塊數字輸入/輸出模塊;輸出信號電平為ECL電平,同時兼具TTL/CMOS電平的信號輸出功能。基于VXI總線的時鐘源模塊,采用AlTERA公司的FLEX系列的FPGA實現寄存器基接口電路和部分功能電路;用MOTOROLA公司的MECL集成電路,實現時鐘源模塊的功能電路;用LabWindows/CVI軟件設計虛擬儀器軟面板,界面友好、操作方便。該時鐘源模塊可以作為自行研制的VXI總線數字輸入/輸出模塊的時鐘源,可以替代同類產品HPE1450A。在雷達故障診斷系統上長期運行的實踐表明,該電路的工作是可靠的。

1 基于VXI總線的時鐘源模塊系統組成與概述

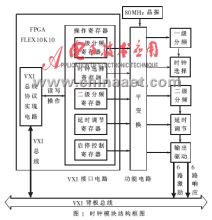

時鐘模塊為單槽、C尺寸、寄存器基器件,整體結構如圖1所示。

?

?

由圖1可以看出,時鐘模塊由接口電路和功能電路兩部分組成。接口部分實現VXI初始化自檢、地址譯碼、配置寄存器和操作寄存器的讀寫、數據傳輸應答等寄存器基器件接口功能。接口電路接收VXI總線的讀寫命令,完成數據傳輸,并通過對操作寄存器的讀寫,產生控制信號操作功能電路。用來控制功能電路的操作寄存器分為一級分頻" title="分頻">分頻寄存器、二級分頻寄存器、延時調節寄存器、啟停寄存器和時鐘選擇寄存器。接口電路全部在ALTERA公司的FLEX10K系列的可編程集成電路內實現。操作寄存器輸出的控制信號,通過電平變換電路,完成COMS/TTL電平到ECL電平的轉換,供功能電路使用。功能電路由80MHz有源晶振、一級分頻、二級分頻、時鐘選擇、延時調節和輸出驅動六部分電路組成,除了晶振外,全部采用MOTOROLA公司的MECL集成電路實現。80MHz有源晶振輸出的時鐘信號經過電平變換后,產生80MHz的ECL時鐘信號,傳送到一級分頻電路" title="分頻電路">分頻電路。一級分頻電路對80MHz的ECL時鐘信號完成第一次分頻,分頻后的信號輸出頻率為80MHz/M,占空比為1/M,M表示一級分頻數,其范圍為2≤M≤65536。二級分頻電路對信號完成第二次分頻,80MHz的ECL時鐘信號和經一級分頻電路分頻后產生的時鐘信號,同時提供給時鐘選擇電路,時鐘選擇電路選擇輸出的信號作為二級分頻的時鐘信號。80MHz有源晶振輸出的時鐘信號用兩種方式完成分頻,既可通過一級分頻后再進行二級分頻,也可直接加到二級分頻電路上產生分頻信號輸出。

兩種方式能產生不同頻率的輸出信號。第一種方式的輸出信號頻率為80MHz/M×N,且2≤M≤65536,2≤N≤4096;第二種方式輸出信號的頻率為80MHz/N,且2≤N≤4096;M和N分別為一級分頻數和二級分頻數,兩種方式輸出信號的占空比均為1/N。延時調節電路對第二級分頻后的信號完成移位操作,它能對輸入信號產生12.5ns的延遲,并輸出八路延時后的信號,將八路延時后的信號通過一個多路選擇器,選擇具有不同延遲時間的信號作為響應時鐘信號,從而實現信號的延時調節。輸出驅動電路把沒有延時的信號作為激勵信號輸出,把延時調節后的信號作為響應信號輸出。輸出的同頻率的六路激勵信號和六路響應信號,經VXI背板本地總線,傳送到數字輸入輸出模塊中,作為時鐘使用。由于MOTOROL的MECL集成電路,其輸出端全部采用射級跟隨電路輸出,具有較低的輸出阻抗和較高的驅動能力,可用作六路激勵信號和六路響應信號的驅動。

2 接口電路工作原理

接口電路的功能可由一片可編程邏輯器件(PPGA)完成,采用ALTERA公司的FLEX10K系列的EPF10K10QC208-4芯片實現。FLEX10K系列的FPGA有著較低的功耗,在5V電壓下工作時,其輸出高電平最小為2.4V,輸出低電平最大為0.45V;管腳處于高阻態時,漏電流為-40~40μA;商業級芯片的操作環境溫度為0~85°C;其最大功耗Pmax可由公式Pmax=(Tj-Ta)/θja算出,Ta為芯片工作時的環境溫度,Tj為芯片工作時的溫度。取θja=8°C/W、Ta=40°C、Tj=85°C,可得Pmax=5.625W,滿足VXI總線對接口芯片的要求。

接口電路結構圖如圖2所示。它具有如下特點:①具有VXI總線地址譯碼能力,能譯碼16位VXI總線地址,并能根據需要擴展到24位或32位;具有16位數據的傳送能力并能根據功能進行相應的擴展。②內部寄存器分別為配置寄存器、STATUS/ID寄存器、儀器類型寄存器等,可根據不同模塊功能電路,設計不同的功能寄存器。③能對VXI總線的數據傳輸仲裁和應答。④能監視功能電路的中斷請求,可通過軟件或外部跳線設置中斷級別,向VXI總線發中斷請求信號,完成中斷菊花鏈的傳遞,并將邏輯地址放到數據線上。

?

其中,各操作寄存器的定義如表1~4所示。

?

?

3 功能電路工作原理

時鐘模塊的功能電路由80MHz有源晶振、一級分頻、二級分頻、時鐘選擇、延時調節、輸出驅動六部分電路組成。這里僅重點介紹一級分頻電路和時序調節電路工作原理,其它部分不再贅述。一級分頻電路的原理圖如圖3所示,它由四個計數器MC10H016(U11、U12、U13、U14)和兩個或門MC10H109(U15、U16)組成,能實現2~65536范圍內的任意分頻。FPGA內的寄存器實現分頻預置數的設置,預置數經過MC10H124實現電平變換后,加到四片MC10H016的置數端,如圖3中的PF0~PF15。當U11計滿時,即QF0~QF3為1111時,計數滿輸出低電平有效信號,即TC1為低電平,TC1加載到U12的允許計數端 ,作為計數器U12的允許計數信號,使U12計數器計數加1;當U12計數滿時,TC2輸出低電平有效,使計數器U13開始計數;同理當U13計滿時,U14開始計數時。只有當U11、U12、U13、U14同時計滿時,U11、TC2、TC3、TC4才同時為低電平有效,TC1、TC2、TC3、TC4四路信號相或形成低電平有效的PEL信號,PEL信號即作分頻后的時鐘輸出,也作四片計數器的并行加載信號。當并行加載信號PEL為低電平有效時,表示四片計數器同時計滿,預置數PF0~PF15被加載到四片MC10H016上,作為計數的起始值,重新開始計數,完成了對時鐘信號CLK的分頻,分頻后的時鐘由PEL輸出。

,作為計數器U12的允許計數信號,使U12計數器計數加1;當U12計數滿時,TC2輸出低電平有效,使計數器U13開始計數;同理當U13計滿時,U14開始計數時。只有當U11、U12、U13、U14同時計滿時,U11、TC2、TC3、TC4才同時為低電平有效,TC1、TC2、TC3、TC4四路信號相或形成低電平有效的PEL信號,PEL信號即作分頻后的時鐘輸出,也作四片計數器的并行加載信號。當并行加載信號PEL為低電平有效時,表示四片計數器同時計滿,預置數PF0~PF15被加載到四片MC10H016上,作為計數的起始值,重新開始計數,完成了對時鐘信號CLK的分頻,分頻后的時鐘由PEL輸出。

?

?

延時調節電路如圖4所示。它由兩片移位寄存器MC10141(U28、U29)和1片八選一多路選擇器MC10H164(U30)組成,完成對經過二級分頻后的信號DIVCLK的延時處理。延時的調節范圍為D×12.5ns,0≤D≤7,12.5ns由80MHz的時鐘信號確定。圖4中的S1、S2確定移位的方向。當S1為高電平、S2為低電平時(S2端懸空時,片子的內部邏輯使其保持為低電平),二級分頻后的信號DIVCLK作用在U28的DL端,表示信號DIVCLK在80MHz的時鐘信號作用下,依次進行移位操作,輸出端STCLK1相對于STCLK0端有12.5ns的延時,STCLK2相對于STCLK1端有12.5ns的延時。依此類推,STCLK7相對于STCLK6端有12.5ns的延時。其時序如圖5所示。延時后的信號經過MC10H164,可以選擇輸出具有不同延時長度的信號作為響應時鐘信號。如選擇X7端作為輸出,則X7端相對于X0端具有7×12.5ns的延時。用該電路實現延遲,相比各種延遲線器件(如AD9500等)具有經濟、實用、可靠的特點,可以廣泛地應用于需要延遲設計的電路中。

?

?

?

4 時鐘源電路板的設計

功能電路部分主要難點在于如何消除電路噪聲。應按高速數字電路的設計理論,盡量減少電路板中的串擾、反射、電磁干擾、電路噪聲等。否則,邏輯正確的電路也無法正常工作。除了合理的電路布局和電路濾波以外,正確地設置終端匹配電路是解決問題的關鍵。ECL器件的噪聲容限較小,約為800mV,因此過大的噪聲將使器件不能正常工作。由于ECL器件功耗大,合理的器件布局,將使器件的散熱比較均勻,防止局部溫度過高,也有利于電路板的正常工作。

?

參考文獻

1 錢衛明,陰澤杰. 一種通用可編程的高速ECL時鐘成形和分頻模塊. 核電子學與探測技術,2001(1)

2 陳虎成,安 琪,王硯方.基于VXI總線的時鐘測量模塊.核電子學與探測技術,2001(1)

3 陳光禹. VXI總線測試平臺技術. 成都:電子科技大學出版社,1996

4 IEEE Standard for VMEbus Extensions for Instrumentation:VXIbus. IEEE,1996:1155~1992

5 崔少輝,孟 晨,楊鎖昌. VXI總線自動測試系統測試接口設計.電子技術應用,2002;28(7)