ADC是現代數字解調器和軟件無線電接收機中連接模擬信號處理部分和數字信號處理部分的橋梁,其性能在很大程度上決定了接收機的整體性能。在A/D轉換過程中引入的噪聲來源較多,主要包括熱噪聲、ADC電源的紋波、參考電平的紋波、采樣時鐘抖動引起的相位噪聲以及量化錯誤引起的噪聲等。除由量化錯誤引入的噪聲不可避免外,可以采取許多措施以減小到達ADC前的噪聲功率,如采用噪聲性能較好的放大器、合理的電路布局、合理設計采樣時鐘產生電路、合理設計ADC的供電以及采用退耦電容等。

本文主要討論采樣

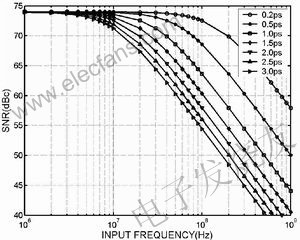

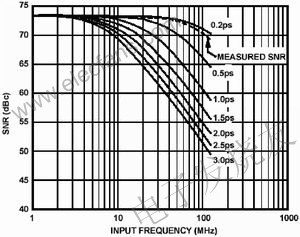

(a)12位ADC理想信噪比

(b)AD9245實測信噪比

圖1 不同時鐘抖動情形下12位ADC的信噪比示意圖

時鐘抖動對ADC信噪比的影響

采樣時鐘的抖動是一個短期的、非積累性變量,表示數字信號的實際定時位置與其理想位置的時間偏差。時鐘源產生的抖動會使ADC的內部電路錯誤地觸發采樣時間,結果造成模擬輸入信號在幅度上的誤采樣,從而惡化ADC的信噪比。歡迎轉載,本文來自電子發燒友網(http://www.elecfans.com )

在時鐘抖動給定時,可以利用下面的公式計算出ADC的最大信噪比:

根據公式(2),圖1分別給出了量化位數為12-bit時不同時鐘抖動情形下ADC理想信噪比和實測信噪比示意圖。

由圖1可以看出時鐘的抖動對ADC信噪比性能的惡化影響是十分明顯的,相同時種抖動情形下進入到ADC的信號頻率越高,其性能惡化就越大,同一輸入信號頻率情形下,采樣時鐘抖動越大,則ADC信噪比性能惡化也越大。對比圖1中兩個示意圖可以看出實測的采樣時鐘抖動對ADC信噪比性能的影響同理論分析得到的結果是十分吻合的,這也證明了理論分析的正確性。因此,在實際應用時不能完全依據理想的信噪比公式來選擇A/D轉換芯片,而應該參考芯片制造商給出的實測性能曲線和所設計的采樣時鐘的抖動性能來合理選擇適合設計需要的A/D轉換芯片,并留出一定的設計裕量。

圖2 一個實用的低抖動時鐘產生電路

兩種實用的低抖動采樣時鐘產生電路

時鐘抖動的產生機制

直接測量時鐘抖動是比較困難的,一般采用間接測量的方法,為此本節首先給出時鐘抖動的產生機制。時鐘抖動是由時鐘產生電路(一般是基于低相位噪聲壓控振蕩器的鎖相環路)內部各種噪聲源所引起的,例如熱噪聲(主要是壓控振蕩器輸出信號的熱噪聲基底)、相位噪聲和雜散噪聲等,理論分析表明:當所需產生的頻率較高時,相位噪聲和雜散噪聲對時鐘抖動的惡化并不明顯。

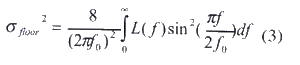

一般來說,VCO輸出級放大器的熱噪聲基底可以看成有限帶寬的高斯白噪聲,其有效帶寬大約為工作頻率的兩倍。當VCO正確地調諧到需要的輸出頻率時,噪聲基底對抖動的影響可以用下面的公式計算:

式中f0是振蕩器的中心頻率,f表示相對于中心頻率的偏移,L(f)是在頻率偏移f處的相位噪聲(單位是dBc/Hz)。為了進一步改進系統的性能,人們往往在VCO的輸出端使用一個頻率響應類似于帶通濾波器的功率匹配網絡,這對帶寬外的噪聲有一定的衰減作用。這樣,就能夠利用從0 Hz到f0區間內的積分估算最差情況下的噪聲,該范圍以外的噪聲被大大削弱,可以忽略,因為從0到f0范圍內的噪聲基底是平滑的,L(f)可視為常數,于是公式(3)簡化為:

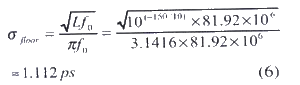

故由噪聲基底引起的邊沿時鐘抖動為:

理論上可以認為從鎖相環路輸出信號的相位噪聲特性同VCO特性基本一致,但實際的鎖相電路會引入一定的噪聲,而VCO輸出放大器也會使產生的時鐘信號的相位噪聲特性變差。所以在進行鎖相環電路的設計時,除了選擇具有較低相位噪聲的VCO外,還應選擇具有較低噪聲系數的放大器或時鐘緩沖器,并盡量將時鐘產生電路與其它電路分隔開來。

基于低相位噪聲VCO的可變采樣時鐘

圖2給出了一個實用的基于低相位噪聲VCO的低抖動可變采樣時鐘產生電路。

圖2中以MC145170作為時鐘產生環路的頻率合成器,選用Mini-Circuits公司的低相位噪聲壓控振蕩器POS-200作為時鐘產生環路的VCO,由于POS-200的輸出信號要經過多次分路,所以在其輸出信號作第一次分路后,一路反饋送入MC145170作為輸入調諧信號,另一路則經低噪聲放大器放大后輸出,然后再作一次分路,一路作為ADC的采樣時鐘,另一路則送入DSP作為ADC采樣后數字信號的同步時鐘。由上面的分析可知,只要設計得當,上述的時鐘產生電路輸出信號的相位噪聲特性將主要取決于POS-200,POS-200在偏離中心頻率1MHz處的單邊相位噪聲為-150dBc/Hz,在估計鎖相環電路輸出信號的熱噪聲基底時可以采用該值,當鎖相環輸出信號頻率為81.92MHz時,由公式(5)可以計算出輸出時鐘信號的抖動為:

如果使用的ADC為AD9245,參照圖1可以看出:當ADC前端輸入信號頻率低于50MHz時,AD9245的信噪比將優于65dB,輸入信號頻率低于100MHz時,AD9245的信噪比將優于60dB。

基于極低相位噪聲溫度補償晶振的非可變采樣時鐘

在確定采樣頻率后,如果并不要求時鐘產生電路產生的時鐘可變的話,就可采用基于溫度補償晶振的時鐘產生方法。首先由公式(2)根據所需的ADC信噪比確定最大容許的時鐘抖動,然后由公式(5)反推出最大容忍的相位噪聲基底,最后給出不同頻率偏差點上的相位噪聲特性并交由晶振制作工廠定制即可。這是一種最簡單的時種產生方法,基本不需要作太多調試,但它只適合固定時鐘采樣的情況。

在利用上述兩種方法產生采樣時鐘時,一個值得注意的地方就是采樣時鐘電路應盡可能與存在噪聲的數字系統獨立開來,在采樣時鐘的通路中也不應該有邏輯門電路,一般來說,一個邏輯門將會產生幾個皮秒甚至十幾皮秒的定時抖動。在設計時應該把采樣時鐘產生電路和系統的數字及模擬部分分離。

結語

本文首先分析了采樣時鐘抖動對ADC信噪比性能的影響,然后指出產生時種抖動的原因,最后給出了兩種實用的采樣時鐘產生方案:基于低相位噪聲VCO的可變采樣時鐘及基于極低相位噪聲溫度補償晶振的非可變采樣時鐘的產生方法。