摘要:在深入研究Nios自定制指令的軟硬件接口的基礎上,利用Matlab/DSP Builder建立快速傅里葉變換FFT核心運算指令基本模型,然后用Altera公司提供的Singacompiler工具對其進行編譯,產生 QuartusⅡ能夠識別的VHDL源程序,并將此程序在Nios中自定制成相關的FFT運算指令。利用自定制的FFT運算指令,在Nios中利用C語言 編寫基于Nios的FFT算法程序,實現了FFT運算的軟硬件協同設計。經測試表明,將FFT算法加入到Nios嵌入式處理器指令集中,可以幫助系統完成 復雜的數據處理任務,增強Nios系統的實時處理能力。該設計方法打破了軟硬件間的屏障,大大加快了系統的功能驗證。

關鍵詞:FFT;自定制指令;軟硬件協同設計;EP2C5Q208C8

在自動控制領域,往往要對被控對象進行狀態檢測,從而作出下一步的處理,達到控制的目的,因此自動控制系統離不開對被控系統的狀態進行監測,以便對其進行 處理,例如滾動軸承故障、電動機故障等均可以利用頻譜分析法對其進行狀態監測和故障診斷。要檢測被控對象的狀態,就離不開數字信號處理,因此,數字信號處 理應用廣泛。并且FFT(快速傅里葉變換)促進了數字信號處理的發展,它可應用傅里葉變換理論所能涉及的任何領域。對于FFT工程的實現方法有軟件法和硬 件法,即通過軟件程序完成FFT運算,這種方法可適用于各種數字信號處理的應用場合,很靈活,但缺點是不能進行實時處理。而使用專用硬件完成數字信號處理 的方法能夠實現實時處理,但外圍電路相對復雜,不易擴展,靈活性差,且價格昂貴。因此人們一方面尋求結構簡單、運算速度快,存儲量小的FFI實現方法,另 一方面采用先進的VLSI技術改進實現FFT的硬件結構,將算法硬件化。

Nios嵌入式處理器是FPGA生產廠商Althera推出的軟核CPU,它是一種面向用戶的、可靈活定制的通用RISC嵌入式CPU。用戶可以在 Nios指令系統中增加用戶自定義指令,以增強對強實時軟件算法的處理能力,可以把一個復雜的標準指令序列簡化為一條用硬件實現的單個指令。特別是在需要 使用大量FFT算法的場合,可以根據用戶的需要,定制專門的FFT處理器硬件和定制一些諸如復數乘法或復數加法等傳統運算指令,使Nios系統不但具有常 規數字信號處理器功能,而且具有軟件實現FFT運算處理的特點。

1 FFT算法原理

1.1 按時間抽取的基-2 FFT算法

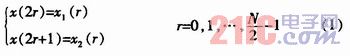

設序列x(n)長度為N,且滿足N=2M,M為正整數。按n的奇偶把x(n)分解為2個N/2點的子序列:

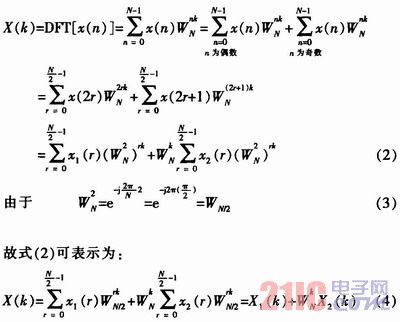

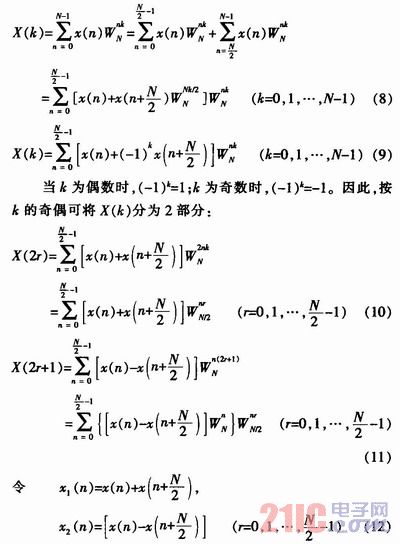

則可將DFT化為:

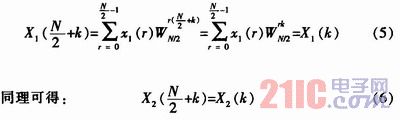

式中,X1(k)與X2(k)分別是x1(r)及x2(r)的N/2點DFT。

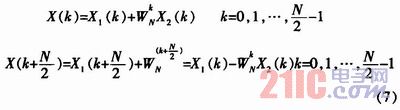

由此可以看到,一個N點DFT已分解成2個N/2點的DFT。這2個N/2點的DFT再按照式(4)組合成1個N點DFT。這里應該看到 X1(k),X2(k)只有N/2個點,即k=O,1,…,(N/2)-1。而X(k)卻有N個點,即k=O,1,…,N-1,故用式(4)計算得到的只 是X(k)的前一半的結果,要用X1(k),X2(k)來表達全部的X(k)值,還必須應用系數的周期性,這樣可得到:

說明后半部分k值(N/2≤k≤N-1)所對應的X1(k),X2(k)分別等于前半部分k值(O≤k≤(N/2)-1)所對應的X1(k),X2(k)。這樣,就可將X(k)表達為前后兩部分:

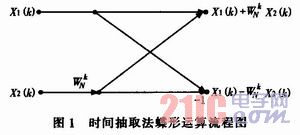

其運算關系可以利用蝶形運算流程圖來形象地描述,圖l為按時間抽取法的蝶形運算流程圖符號。

1.2 按頻率抽取的基-2FFT算法

仍設序列點數為N=2M,M為正整數。在把輸出X(k)按k的奇偶分組之前,先把輸入序列按前、后各一半(不是按偶奇)分開,把N點DFT寫成2部分,則可將DFT化為:

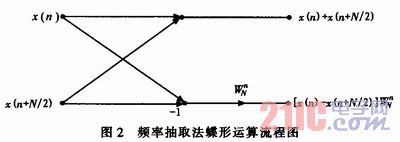

圖2為按頻率抽取法的蝶形運算流程圖符號,這樣,就把1個N點DFT按k的奇偶分解為2個N/2點的DFT了。

由以上分析可知,FFT算法中最核心的是蝶形運算單元。而一個蝶形運算單元主要由一次復數乘法,兩次復數加法構成。為此整個FFT算法中,復數乘法和復數加法是最為核心的運算單元。

2 FFT算法軟硬件協同設計

軟硬件協同設計指對系統中的軟硬件部分使用統一的描述和工具進行集成開發,完成全系統的設計驗證并跨越軟硬件界面進行系統優化。其基本的設計流程是先用 VHDL語言和C語言進行系統描述并進行模擬仿真和系統功能驗證;然后對軟硬件實現進行功能劃分,分別用語言進行設計并將其綜合起來進行功能驗證和性能預 測等仿真確認(協調模擬仿真);其次進行軟件和硬件詳細設計;最后進行系統測試。

根據上面的分析可知,FFT算法中最核心的是蝶形運算單元,而復數乘法和復數加法又是蝶形運算單元的核心,因此可以采取Nios的自定義指令功能,定制一條復數乘法指令和一條復數加法指令,以便完成一次蝶形運算。

2.1 建立NiosⅡ嵌入式處理器系統

首先,利用QuartusⅡ建立項目工程,選用的目標器件為CycloneⅡEP2C5Q:再用SOPCBuider創建NiosⅡ組件 模型,生成硬件描述文件,鎖定引腳后進行綜合與適配,生成NiosⅡ硬件系統下載文件;然后建立NiosⅡ嵌入式系統,從SOPC Builder組件欄中加入所需的組件(如NiosⅡCPU核、定時器Timer、JTAG_UART、Avalon三態總線橋、鍵輸入I/O口和 Flash等)。另外,為了實現NiosⅡ處理器對EPCS Flash存儲器的讀寫訪問,還要加入EPCS Serial FlashController組件。通過此控制器將用于FPGA配置的SOF文件和CPU運行的軟件一并存于EPCS器件中,以便大大簡化硬件系統組成 結構。為了保證所有組件的地址安排是合法的,要對各組件地址實行自動分配;最后進行全程編譯(即分析、綜合、適配和輸出文件裝配),完成NiosⅡ硬件系 統的設計。

2.2 利用DSP Builder生成復數乘法模塊

使用DSP Builder在FPGA上進行DSP模塊的設計,可實現高速DSP處理。但是,在實際應用中,除了要求DSP高速外,由于DSP處理的算法往往比較復 雜,如果單純使用DSPBuilder來實現純硬件的DSP模塊,會耗費過多的硬件資源,因此有時也無法完成許多算法復雜的模型。而NiosⅡ則是一個建 立在FPGA上的嵌入式微處理器軟核,它有一個重要的特性是具有自定制指令。在DSP算法中會反復出現一些運算(如復數乘法器、整數乘法器、浮點乘法器 等),而在通用的CPU中都沒有專門用于復數乘法計算和浮點乘法計算的相關指令。在系統設計中,利用MA-TLAB、DSP Builder或者VHDL設計并生成復數乘法器、整數乘法器、浮點乘法器等硬件模塊。在QuartusⅡ環境中對上述文件做一些修正后,在SOPC Builder窗口中將它們定制為相應的指令,并可設定或修改執行該指令的時鐘周期。在進行DSP算法運算時,可通過匯編或C語言,甚至C++語言來運用 這些自定義指令進行嵌入式程序設計。

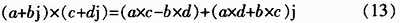

根據復數運算,設2個復數為a+bj和c+dj,則乘法表述為:

在MATLAB/Simulink下建立如圖3所示的復數乘法模型,圖中的Dataal、Databl和Resultl是DSP Builder中SOPCLibrary中Custom Ins-truction中的模塊,分別對應Nios內部ALU的2個輸入信號dataa和datab,以及ALU的輸出信號result。 Datareal、DataImag、DatbReal、Da-thlmag是一個總線位轉換模塊;BusConeatenation是總線復合模塊。 Dataa toComplex和Datab to Complex是一個實數轉復數的模塊,Com-plex Product是復數乘法模塊,Real Result是復數解出實部和虛部的模塊。

該模型完成了1個16位的復數乘法。在這個設計中,利用Nios32的32位數據位寬,把32位分成2部分,分別放入復數的實部和虛部,實部、虛部的位寬 都是16位,正好構成1個32位數,兩個16位復數進行運算后,把結果設為16位復數,也用32位表示。設此模型的文件名為co-mplex.mdl。并 點擊Signalcompiler,對complex.mdl進行轉換,在轉換窗口中分別作如下選擇:器件選擇CycloneⅡ;綜合器選擇Quart- usⅡ;“SOPC Info”的generate SOPC Builder PTF File項要選擇打勾。分別單擊轉換按鈕1-Convert和綜合按鈕2-Synthesis即可將其轉換成標準的VHDL語言。

2.3 在Nios中加入復數乘法指令

在已建立的SOPC設計中,雙擊CPU項,點擊“Import”按紐,點擊“ADD"按紐,打開Complex_ei.vhd,再點擊 “Readport-list from files"按紐,點擊“ADD to System”按紐,加入該設計作為指令執行模塊。最后再將整個項目重新編譯一次,鎖定引腳后,再下載到目標器件中。為此即在Nios指令中定制了一條名 為COMP的復數乘法指令,在進行C語言編程時,其調用格式為z=nm_comp(x,y),其中x和y為兩個復數,其運算結果放在z中。用同樣的方法, 可以建立復數加法指令和復數減法指令。由此可見,利用DSP Builder很容易地實現了FFT算法中的復數運算指令的定制。同時在定制指令時,對于浮點數的處理,采用統一為幾位二進制有效數字的辦法來解決的,比 如說:小數位數固定為4位,整數位數固定為6位,那么可以定義一個向量signal num:std_logic_vector(9down to 0);在做運算的時候,注意高6位是整數、低4位是小數,就可以達到實型數據的處理。

2.4 FFT算法軟件設計

在NiosⅡ硬件系統設計完成后,將配置文件下載到指定的FPGA中,通過SOPC Builder軟件窗口,可進入NiosⅡIDE軟件開發環境進行軟件設計。

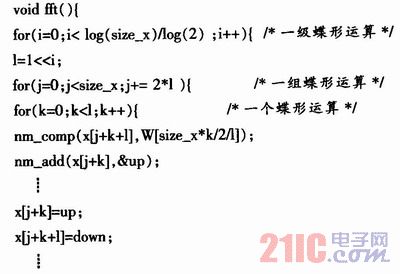

通過SOPC Buider軟件窗口,啟動NiosⅡIDE,然后新建工程,在新建工程的過程中,選擇剛才產生的CPU,新工程產生后,在工程添加文件,在文件中寫入程 序代碼。在軟件編程時設計者可以使用多種方式使用自定制指令,為了簡化軟件開發者使用自定義指令的編程,在生成的SDK中的.h文件中已經包含了自定義指 令的宏定義,可以直接用在C中。下面以基2,8點FFT為例加以說明。在定制了兩條復數運算指令后,可以使用C語言編程實現FFT算法。由于有基本的復數 運算指令和復數加法指令,為此采用C語言編寫程序,其算法變得相當簡單,FFT核心算法如下:

2.5 系統測試

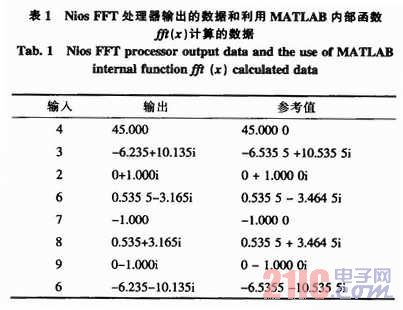

采用Altera公司的Cyclone Ⅱ系列芯片EP2C5Q208C8。用Altera提供的Nios SDK,將編譯后的可執行代碼,通過計算機串口下載到FPGA上的Nios系統內存中去并運行,將輸出結果與Matlab仿真結果進行了比較。比較結果如 表l所示,其中參考值是用MATLAB按FFT計算得到的結果,測試值是在Nios中利用C語言編寫的FFT程序計算的結果,表中某些數據誤差較大,是因 為本系統采用定點數據精度不夠,只要增加定點數據的位數就可提高運算的精度。

3 結束語

Nios是一個性價比較高的微處理器,它是以軟核的方式提供給用戶,并專為在Altera的FPGA上實現作了優化,用于SOPC(片上可編程系統)集 成,最后在FPGA上實現,通過它可以創建Nios CPU設計項目,從而為設計人員提供SOPC設計必需的軟硬件設計平臺。在定制的NiosCPU設計項目中利用Nios的用戶自定義指令功能,可以達到 FFT運算的軟硬件協同設計,實現了快速FFT的變換。由于軟件直接控制硬件,所以編譯過后的軟件調試工作,基本上都是軟硬件協同完成的。因此速度快,占 用資源少,容易擴展。